PCIe Base Specification解析(十)

文章目录

- 4.2.4 Link Initialization and Training

- 4.2.4.1 Training Sequences

- 4.2.4.2 Alternate Protocol Negotiation

- 4.2.4.3 Electrical Idle Sequences

- 4.2.4.4 Inferring Electrical Idle

- 4.2.4.5 Lane Polarity Inversion

- 4.2.4.6 Fast Training Sequence (FTS)

- 4.2.4.7 Start of Data Stream Ordered Set

- 4.2.4.8 Link Error Recovery

- 4.2.4.9 Reset

- 4.2.4.9.1 Fundamental Reset

- 4.2.4.9.2 Hot Reset

- 4.2.4.10 Link Data Rate Negotiation

- 4.2.4.11 Link Width and Lane Sequence Negotiation

- 4.2.4.11.1 Required and Optional Port Behavior

- 4.2.4.12 Lane-to-Lane De-skew

- 4.2.4.13 Lane vs. Link Training

- 4.2.5 Link Training and Status State Machine (LTSSM) Descriptions

- 4.2.5.1 Detect Overview

- 4.2.5.2 Polling Overview

- 4.2.5.3 Configuration Overview

- 4.2.5.4 Recovery Overview

- 4.2.5.5 LO Overview

- 4.2.5.6 LOs Overview

- 4.2.5.7 L1 Overview

- 4.2.5.8 L2 Overview

- 4.2.5.9 Disabled Overview

- 4.2.5.10 Loopback Overview

- 4.2.5.11 Hot Reset Overvview

- 4.2.6 Link Training and Status State Rules

- 4.2.6.1 Detect

- 4.2.6.1.1 Detect.Quiet

- 4.2.6.1.2 Detect.Active

- 4.2.6.2 Polling

- 4.2.6.2.1 Polling.Active

- 4.2.6.2.2 Polling.Compliance

- 4.2.6.2.3 Polling.Configuration

- 4.2.6.2.4 Polling.Speed

- 4.2.6.3 Configuration

- 4.2.6.3.1 Configuration.Linkwidth.Start

- 4.2.6.3.1.1 Downstream Lanes

- 4.2.6.3.1.2 Upstream Lanes

- 4.2.6.3.2 Configuration.Linkwidth.Accept

- 4.2.6.3.2.1 Downstream Lanes

- 4.2.6.3.2.2 Upstream Lanes

- 4.2.6.3.3 Configuration.Lanenum.Accept

- 4.2.6.3.3.1 Downstream Lanes

- 4.2.6.3.3.2 Upstream Lanes

- 4.2.6.3.4 Configuration.Lanenum.Wait

- 4.2.6.3.4.1 Downstream Lanes

- 4.2.6.3.4.2 Upstream Lanes

- 4.2.6.3.5 Configuration.Complete

- 4.2.6.3.5.1 Downstream Lanes

- 4.2.6.3.5.2 Upstream Lanes

- 4.2.6.3.6 Configuration.Idle

4.2.4 Link Initialization and Training

本节定义了物理层控制过程,该过程配置和初始化每个链接以进行正常操作。本节涵盖以下功能:

- configuring and initializing the Link

- supporting normal packet transfers

- supported state transitions when recovering from Link errors

- restarting a Port from low power states

链路训练过程会协商好以下信息:

- Link width

- Link data rate

- Lane reversal

- Lane polarity

链路训练包括以下功能:

- Link data rate negotiation

- Bit lock per Lane

- Lane polarity

- Symbol lock or Block alignment per Lane

- Lane ordering within a Link

- Link width negotiation

- Lane-to-Lane de-skew within a multi-Lane Link

4.2.4.1 Training Sequences

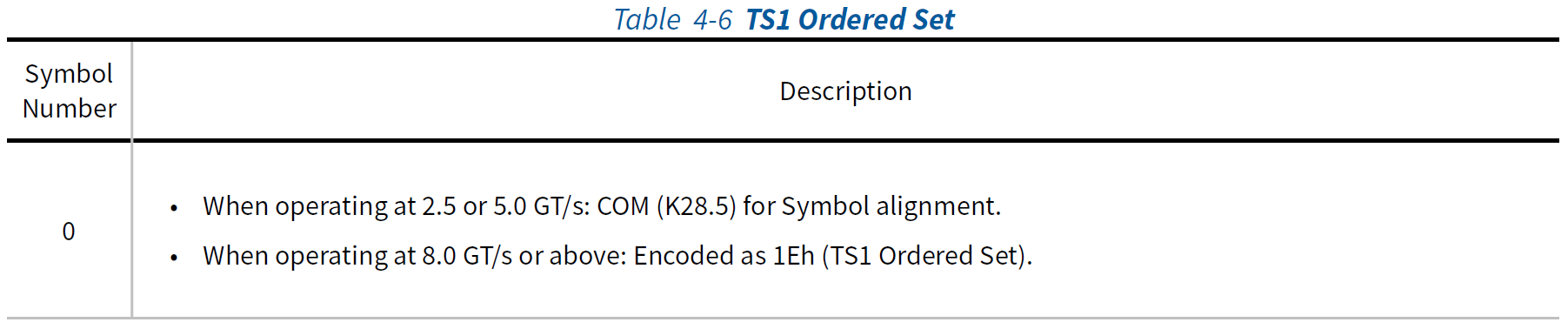

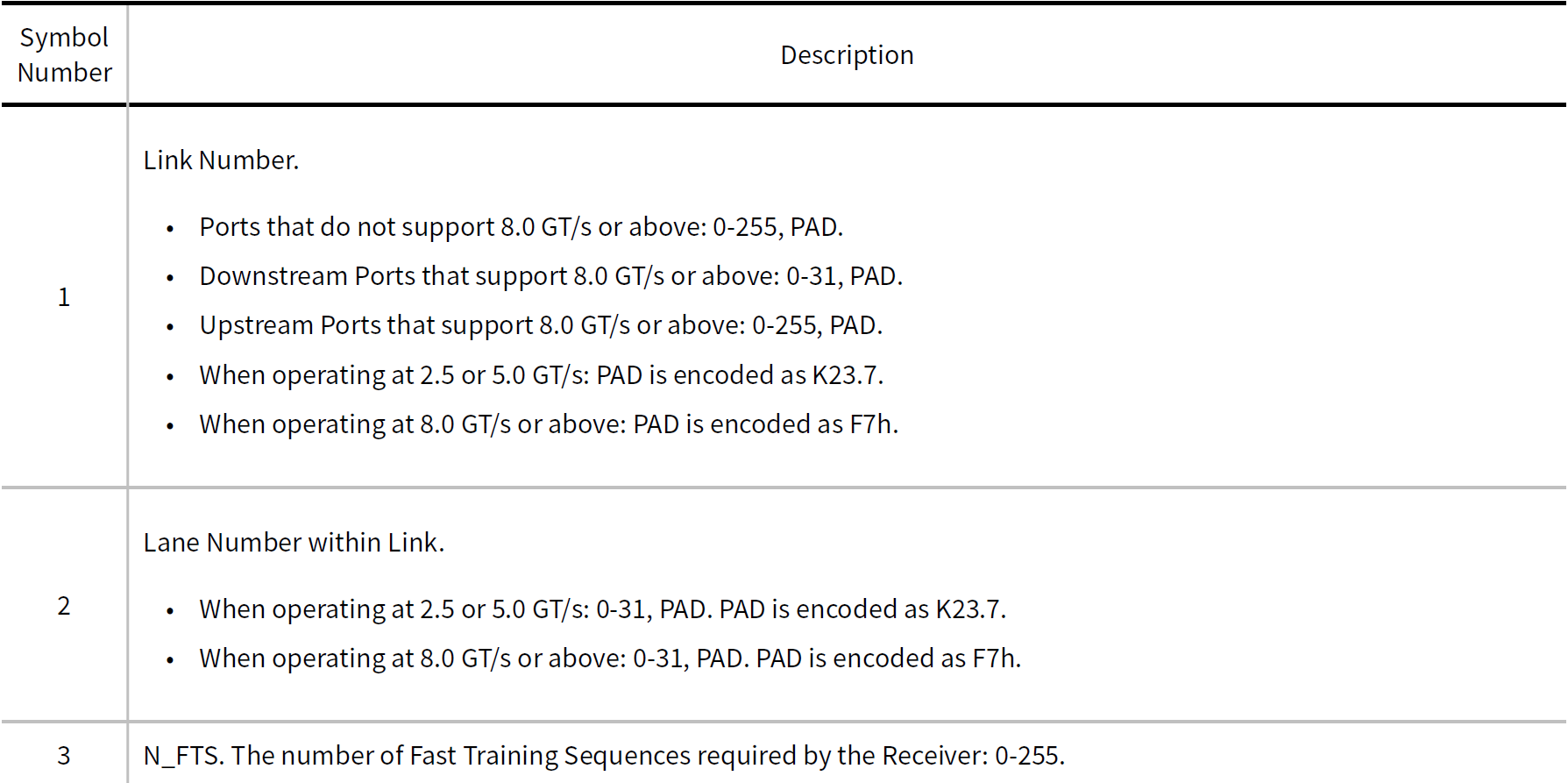

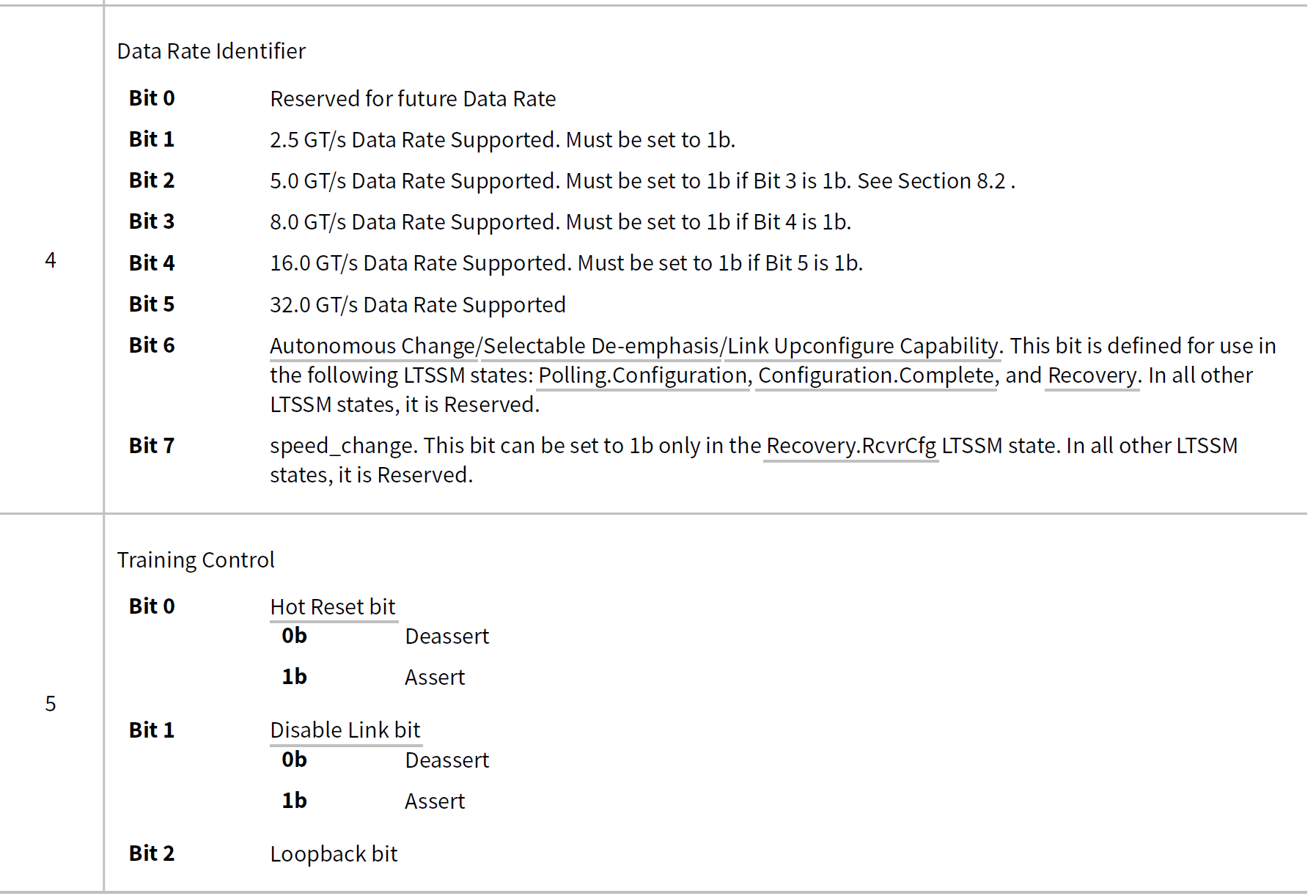

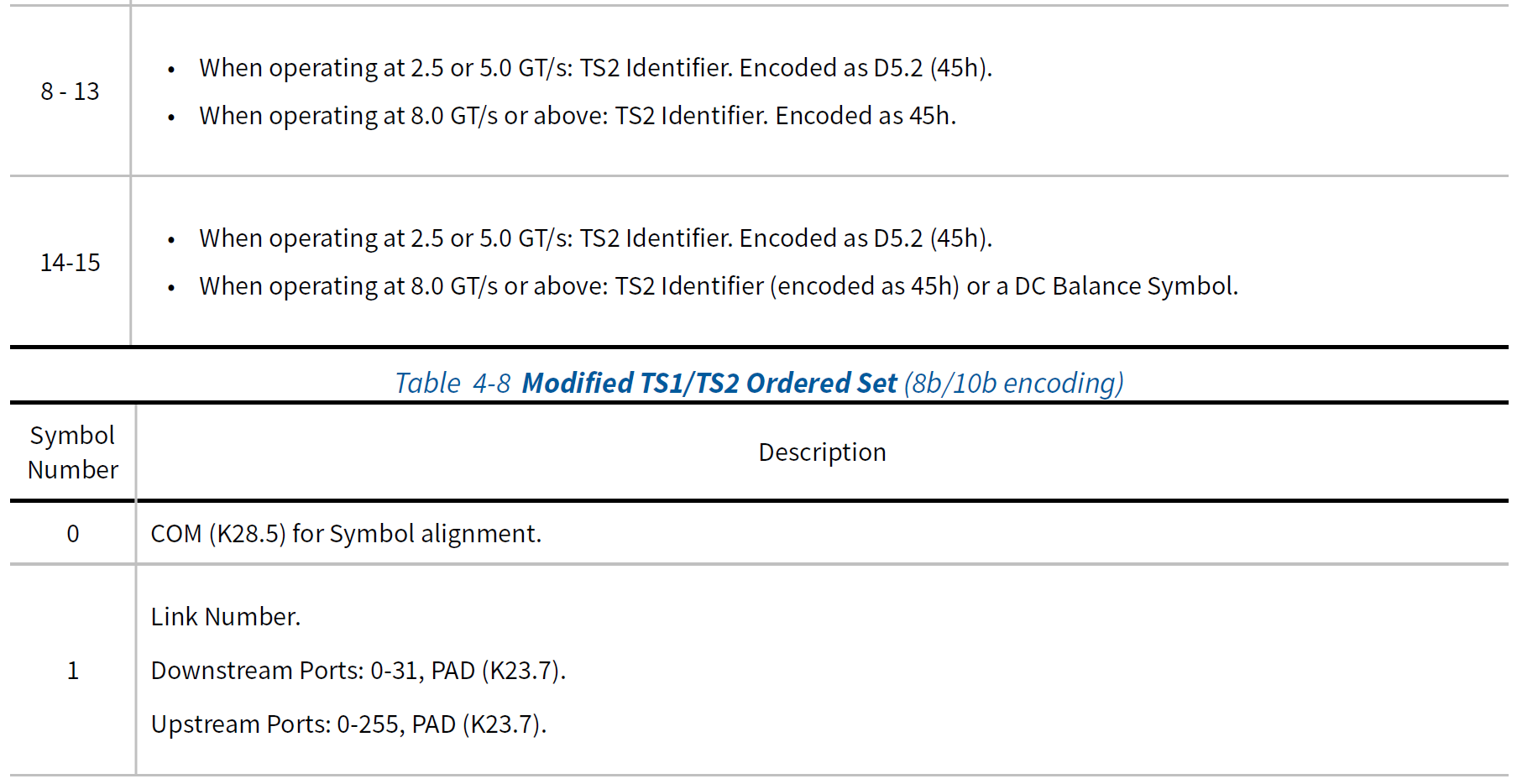

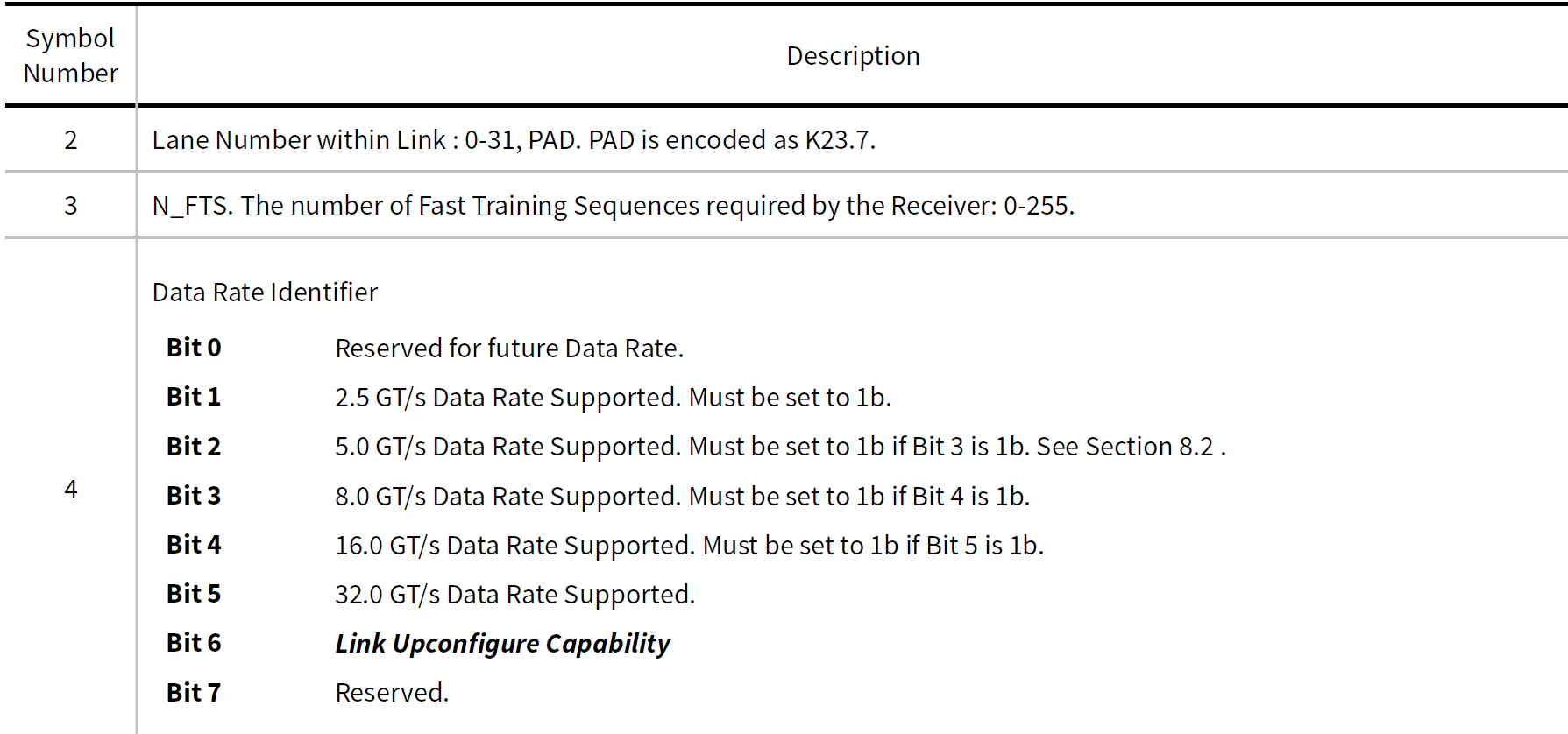

训练序列有序集用于比特对齐、符号对齐以及交换物理层参数。2.5GT/s和5GT/s速率时,训练序列有序集从不加扰,只用8b/10b 编码。到8GT/s及以上速率时,采用128b/130b编码,符号有可能加扰有可能不加扰,具体参阅Section 4.2.2.4。

训练序列(TS1或TS2或Modified TS1或Modified TS2)是连续传输的,并且只能被SKP有序集(Section 4.2.7)或对于2.5 GT/s 以外的数据速率由EIEOS有序集中断(Section 4.2.4.3)。

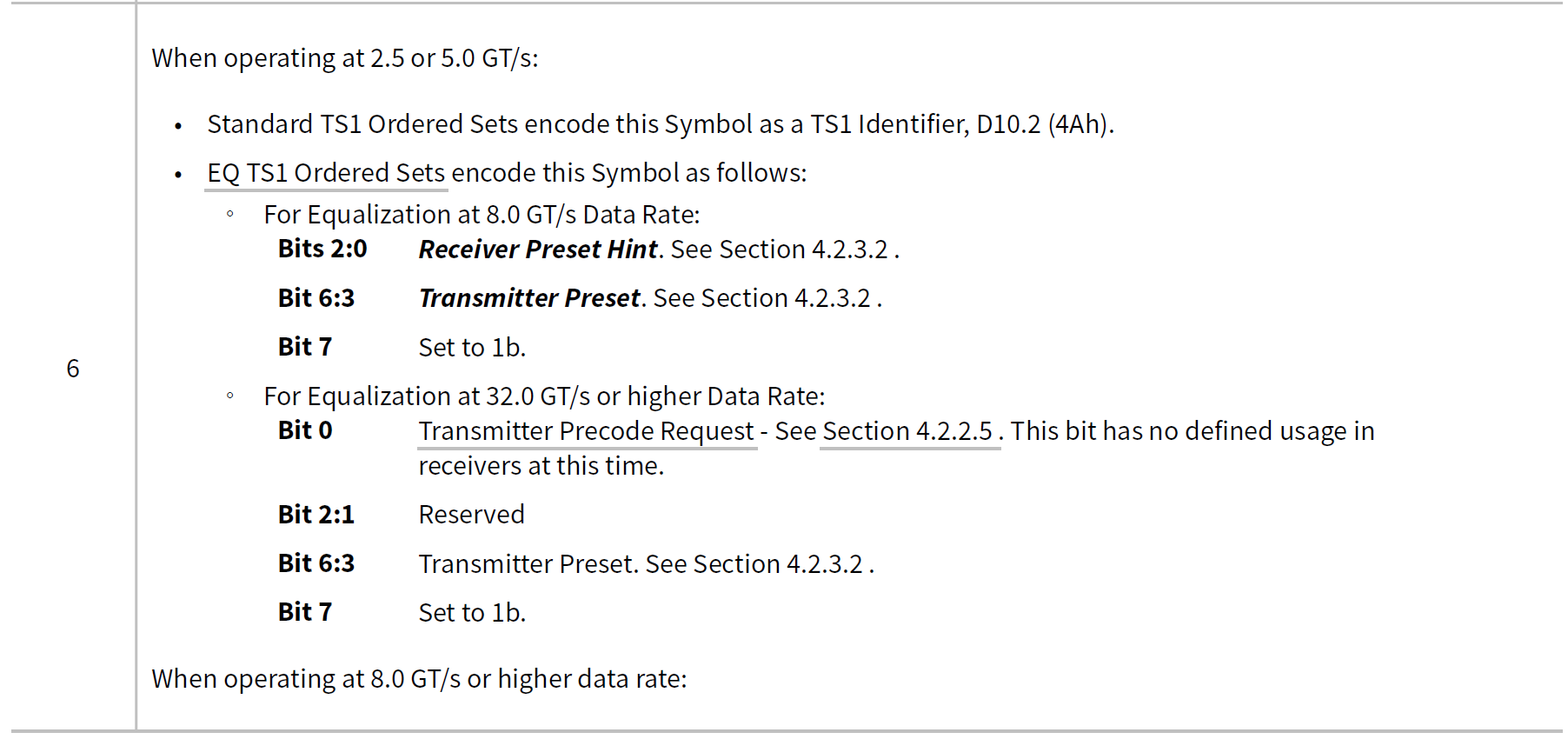

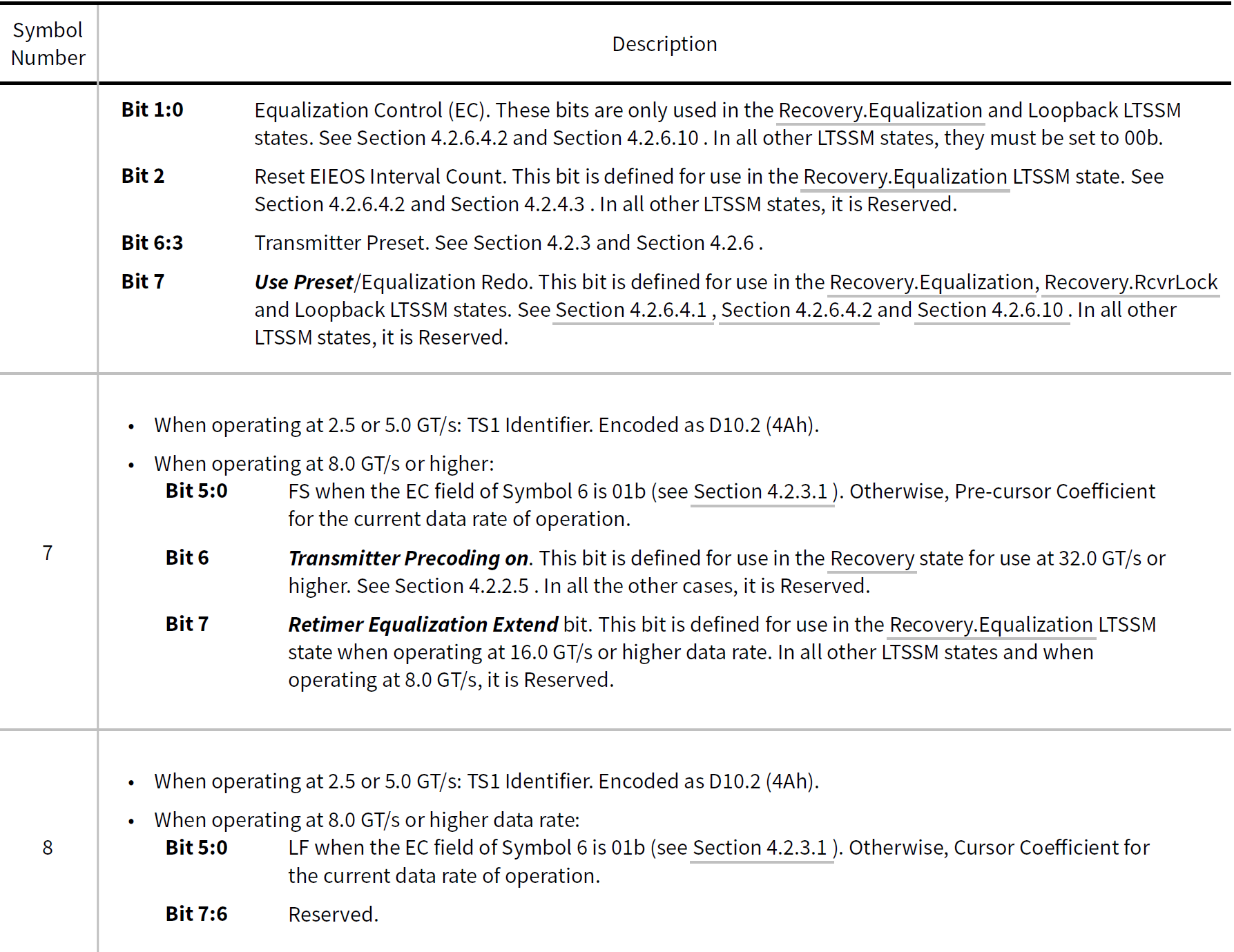

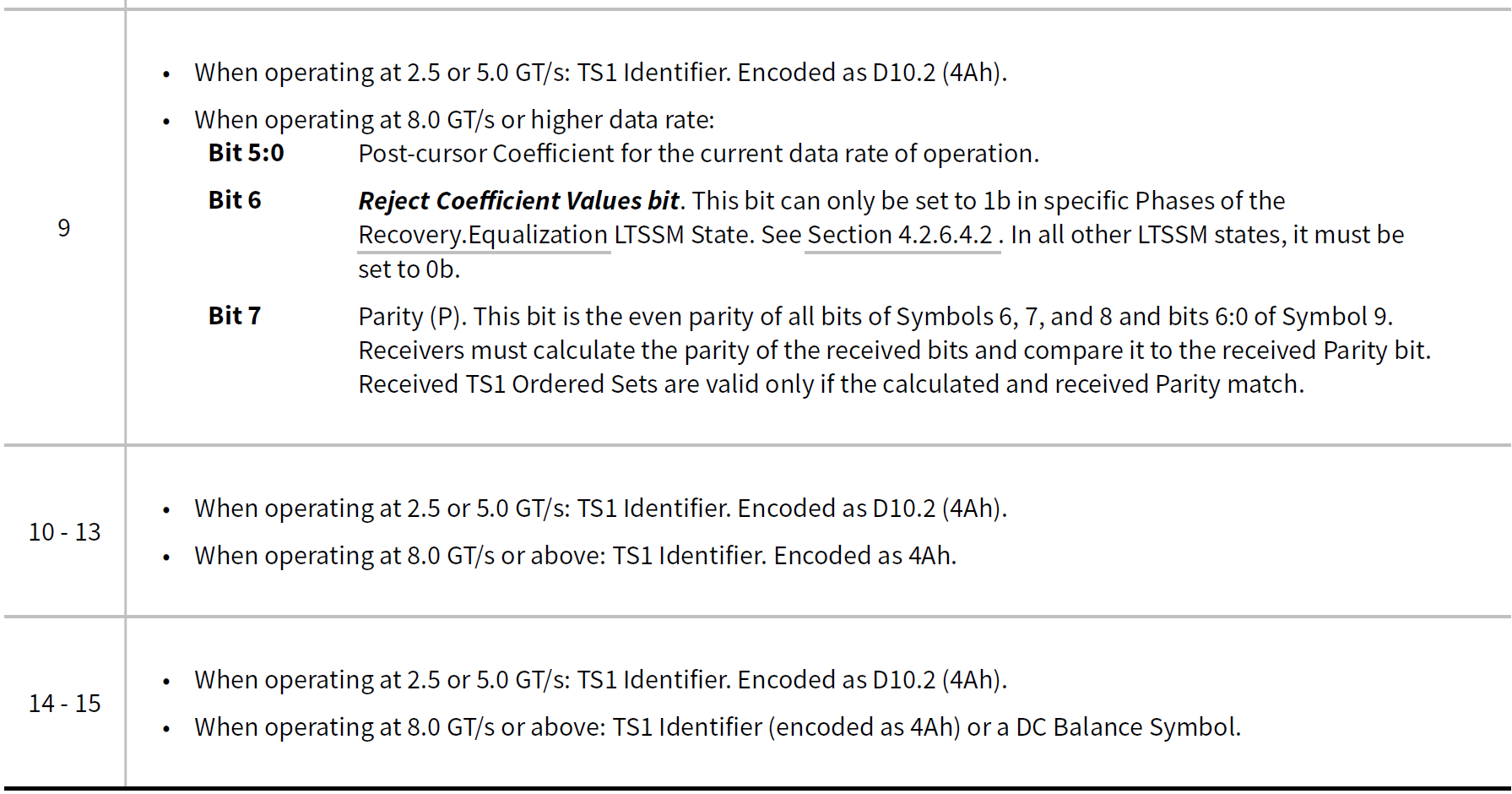

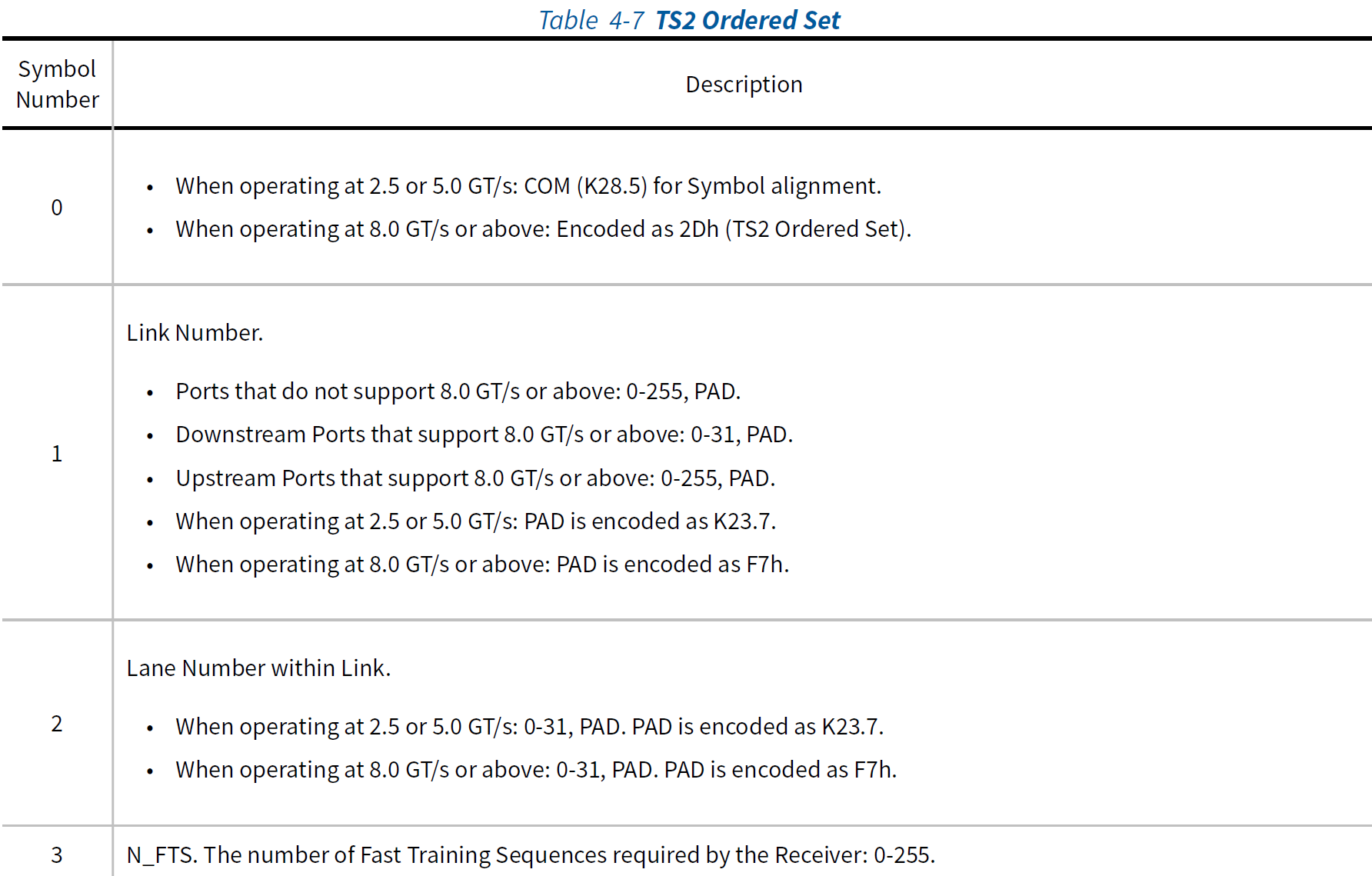

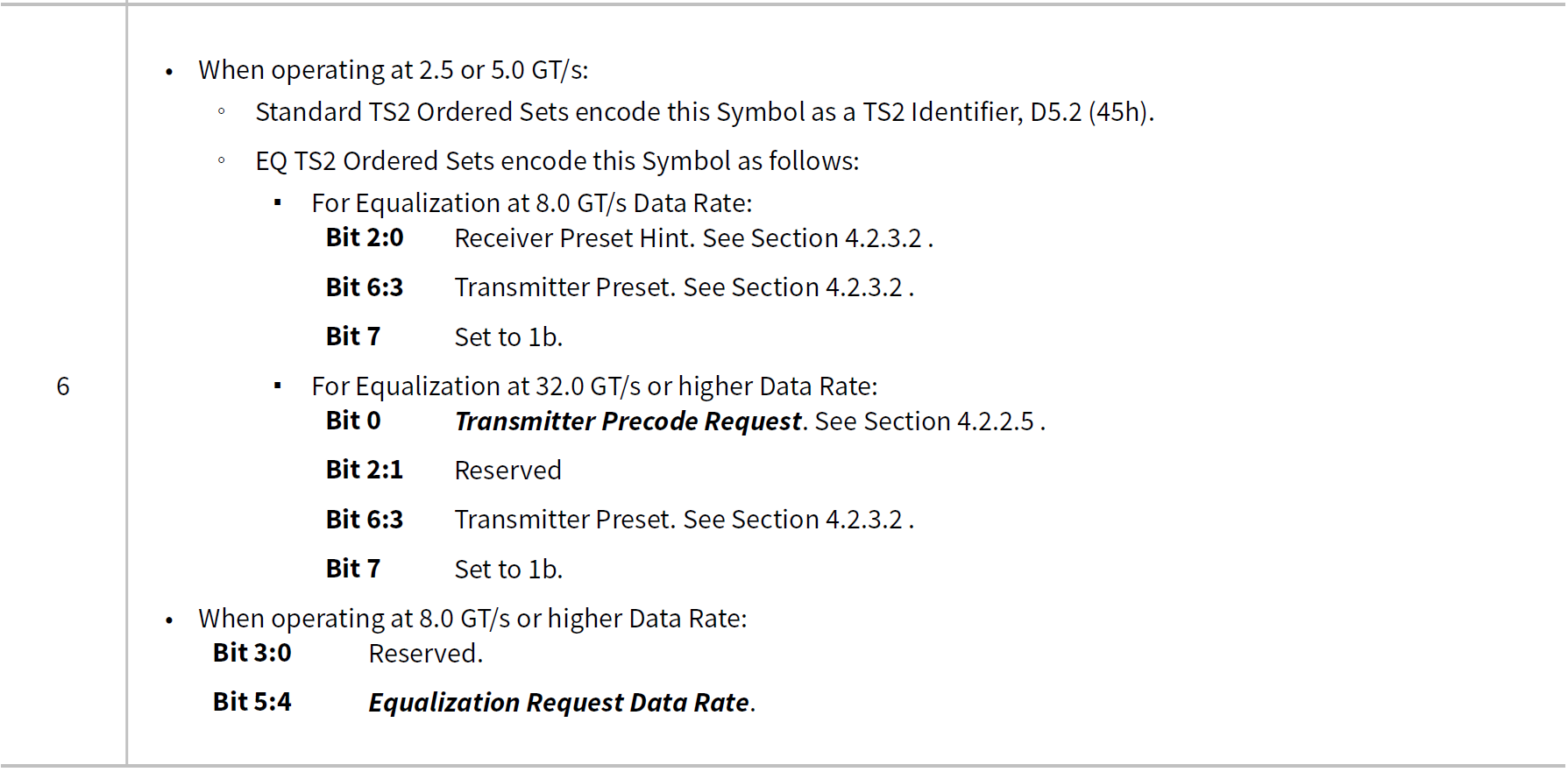

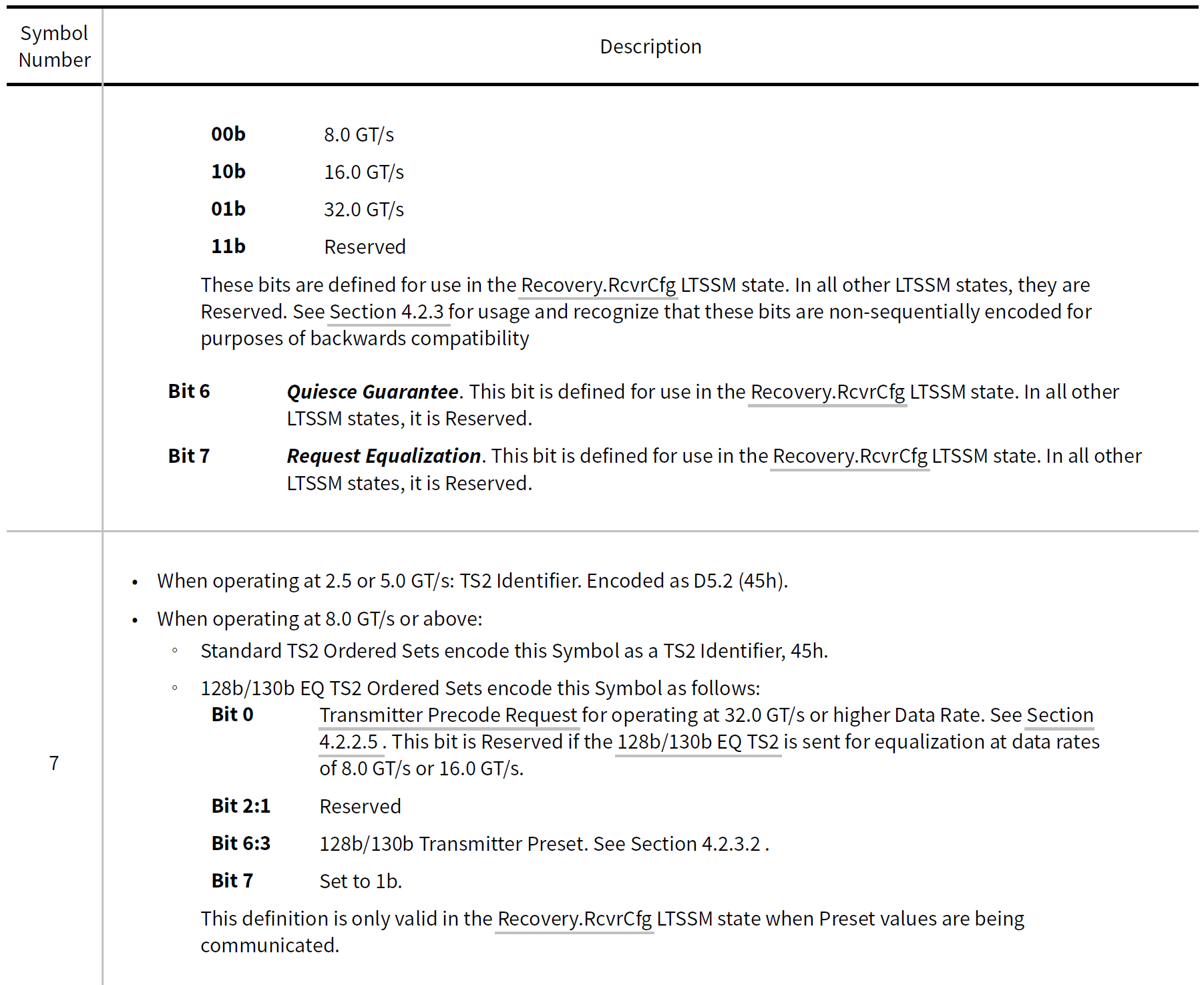

当支持8.0GT/s或更高的数据速率时,使用8b/10b编码的TS1(或TS2)有序集(即2.5或5.0GT/s数据速率)可以是标准TS1(或TS2)有序集(即,对于TS1有序集,Symbol6是D10.2,对于TS2有序集,是D5.2)或EQTS1有序集(或EQTS2有序集)(即,Symbol 6的bit 7是1b)。传输EQ TS1有序集的能力是特定于实现的。支持8.0GT/s或更高数据速率的端口必须接受LTSSM 状态中的TS1(或TS2)类型,除非明确要求查找特定类型。不支持8.0GT/s数据速率的端口允许(但不是必需)接受EQTS1(或TS2)有序集。

当支持16.0 GT/s和更高数据速率时,使用128b/130b编码(即8.0GT/s或更高数据速率)的TS2可以是标准TS2有序集(即Symbol 7为45h)或128b/130b EQTS2(即,Symbol 7的bit 7为1b)。除非明确要求查找特定类型,否则支持16.0GT/s或更高数据速率的端口必须在LTSSM状态中接受任-TS2类型。允许(但不是必需)不支持16.0GT/s数据速率的端口接受128b/130b EQ TS2有序集。

使用8b/10b编码时,仅当Symbol6与先前的TS1或TS2有序集的Symbol 6相匹配时,才将TS1或TS2有序集视为连续(传输过程中不能Symbol6的值不能随意改动)。

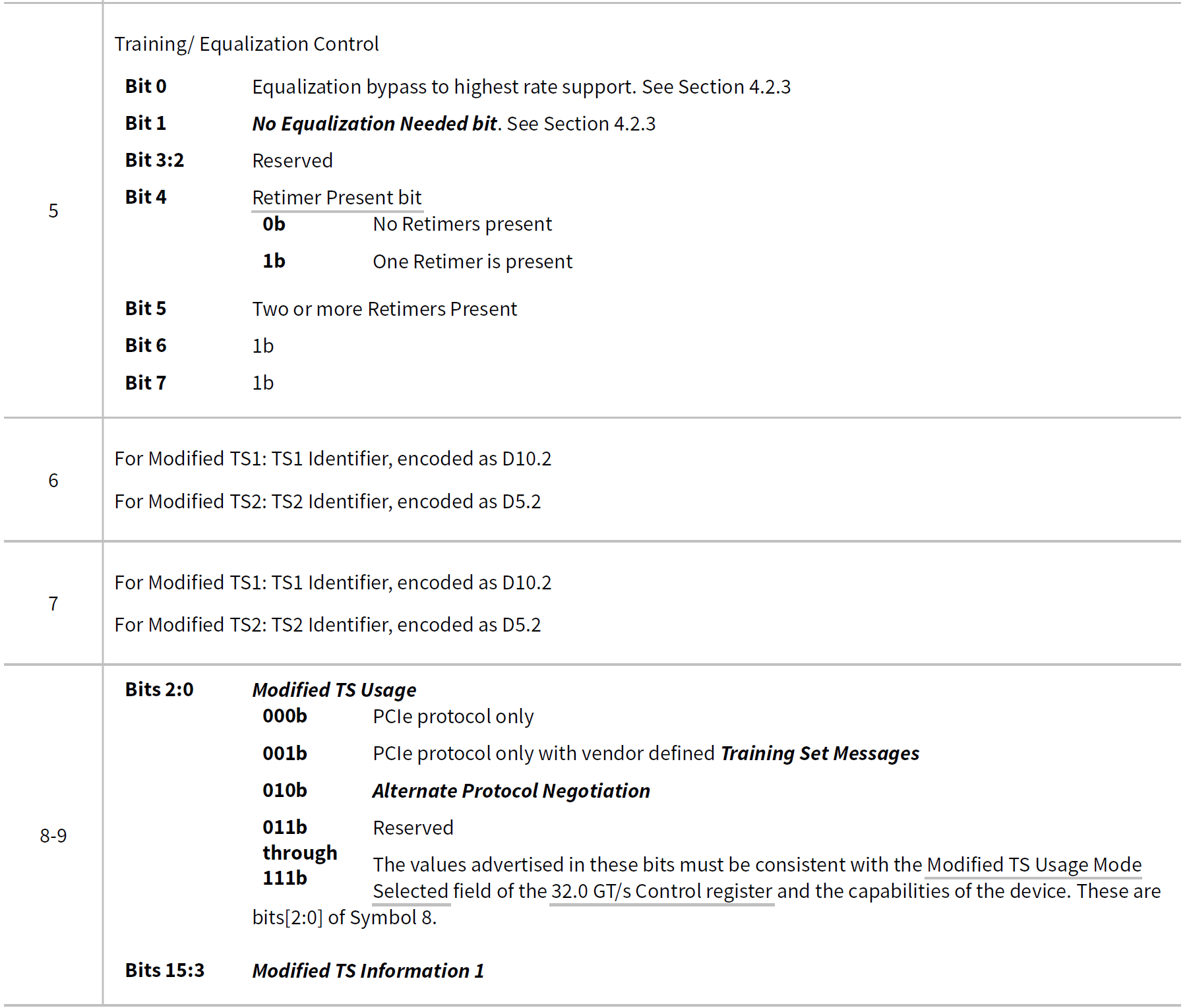

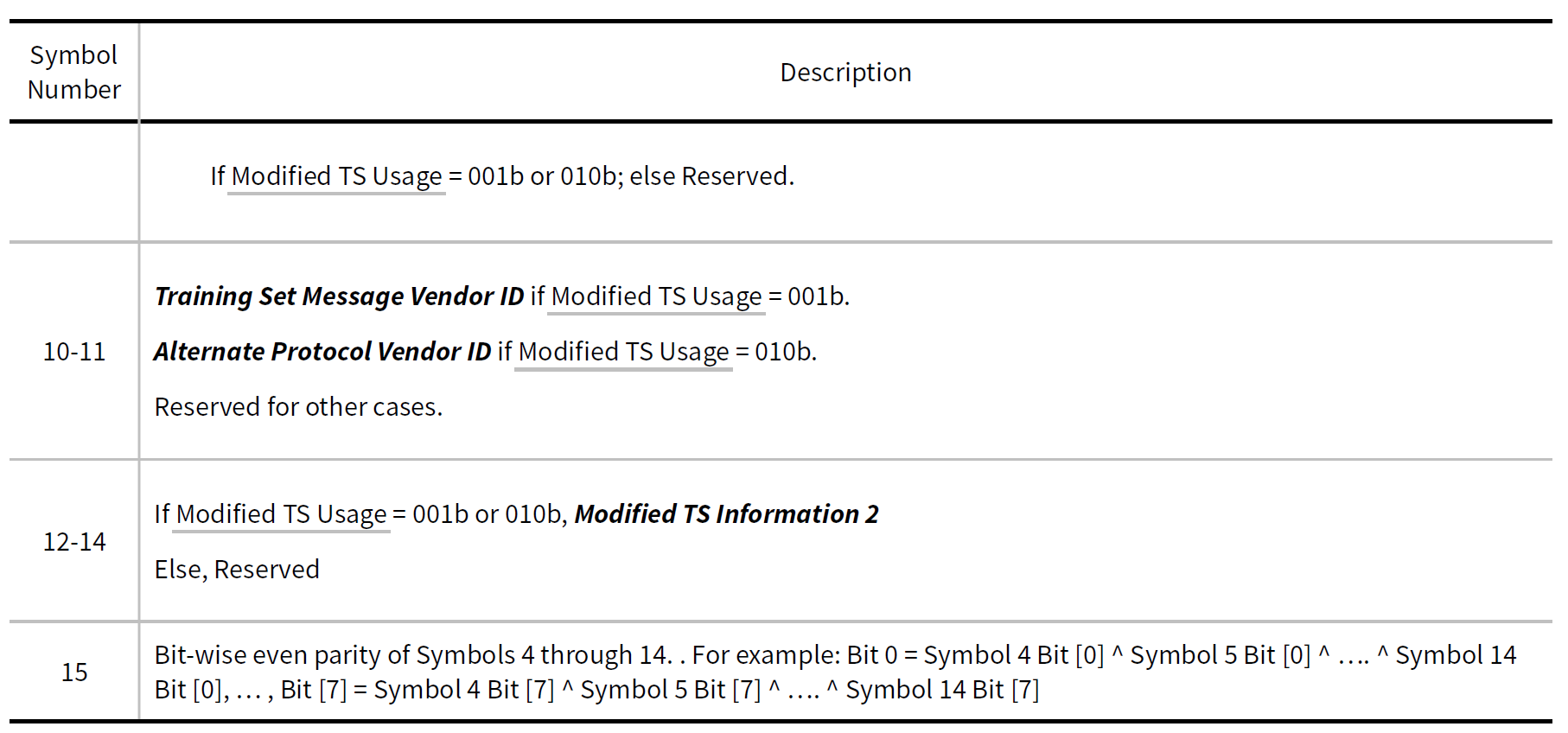

打算协商备用协议或传递一个Training Set Message的组件必须在Configuration.Lanenum.Wait, Configuration.Lanenum.Accept和Configuration.Complete 子状态中使用 Modified TS1/TS2 Ordered Set,而不是TS1/TS2 Ordered Set。为了可以发送 Modified TS1/TS2Ordered Set,组件必须在Polling.Active,Polling.Configuration, TS1/TS2 Ordered Set 中将TS1和TS2有序集的 Enhanced Link behavior Control字段设置为11b,Configuration.Linkwidth.Start和Configuration.Linkwidth.Accept子状态,并执行LinkUp=0b时过渡到Configuration.Lanenum.Wait 子状态中概述的步骤。如果链路伙伴不支持 Modified TS1/TS2 Ordered Set,则从Configuration.LaneNum.Wait 开始,标准TS应停止在Enhanced Link behavior Control 字段中发送11b并切换到适当的编码。

当使用8b/10b编码时,仅当所有Symbol与先前Modified TS1或 Modified TS2 Ordered Set的对应符号匹配且Symbol 15中的奇偶校验与期望值匹配时,才将Modified TS1或Modified TS2 Ordered Set 视为连续。在链路的所有通道上的每个Modified TS1/TS2Ordered Set中,Symbol 8-14必须相同。

当使用128b/130b编码时,仅当Symbol 6-9与先前的TS1或TS2有序集的Symbol 6-9匹配时,才将TS1或TS2有序集视为连续,并按如下所述处理保留位。

TS1和TS2中保留位的处理规则如下:

- 发送端的保留位为0。

- 对于接收端:

-

不得根据接收到的保留位的值确定TS1或TS2有序集是否无效。

-

如果保留位包含在奇偶校验计算中,则必须使用接收到的保留位的值进行奇偶校验计算。

-

可以选择比较在TS1或TS2有序集中被明确要求相同的符号中的保留位的接收值,以确定它们是否连续。

-

不得根据接收到的任何保留位的值采取任何功能性动作。

-

当使用128b/130b编码时,要求发送器跟踪TS1和TS2有序集在链路上(加扰之后)传输的比特流的连续DC平衡。正在运行的DC平衡是已发送的1s数与已发送的Os数之差。每个Lane必须独立跟踪其运行的DC平衡,并且必须能够跟踪任一方向上至少511位的差。所使用的任何计数器都必须在其极限处饱和(而不是翻滚),并在达到极限后继续跟踪减少量。例如,如果检测到513的差异,则可以跟踪511位差异的计数器将在511饱和,如果将来将其减小2,则计数器将变为509。

通过两个事件将运行中的DC平衡设置为0:1)变送器退出电气空闲状态;2)在数据块之后传输EIEOS。

对于每个发送的TS1或TS2有序集,发送器必须评估其DC平衡,并发送为Symbol 14和Symbol 15定义的用于DC平衡的Symbol 之一,如以下算法所定义。如果需要减少1的数量,则发送DC平衡符号20h(对于Symbol 14)和08h(对于Symbol 15)。如果需要减少0,则发送DC平衡Symbol DFh(用于Symbol 14)和F7h(用于Symbol 15)。如果不需要更改,则发送适当的TS1或TS2标识符符号。为Symbol 14或Symbol 15传输的任何DC平衡符号都会绕过加扰,而TS1和TS2标识符则遵循标准加扰规则。必须使用以下算法来控制DC平衡:

- 如果在TS有序集的Symbol 11的末尾,运行中的DC平衡>31,则发送Symbol 14为DFh和Symbol15为F7h的TS有序集以减少0的数量,或者Symbol 14为20h和Symbol 15为08h的TS有序集以减少1的数量。

- 否则,如果在TS有序集的Symbol 11的末尾正在运行的DC平衡>15,则发送Symbol 15为F7h的TS以减少0的数目,或发送Symbol 15为08h的TS以减少1的数目。Symbol 14传输正常的加扰的TS标识符。

- 否则,Symbol 14和Symbol 15都传输正常的加扰的TS标识符。

当确定TS1或TS2有序集有效时,允许但不要求接收者检查Symbol 14和Symbol 15的下列值:解扰后的适当TS标识符符号,或在对Symbol 14进行解扰之前有效的DC平衡符号DFh或20h,或在对Symbol 15进行解扰之前将有效的DC平衡符号F7h或08h。

如果接收方在Symbol 14中收到DC balance pattern,则该pattern 可能会被加扰(并预编码)。因此,如果接收器正在执行此可选检查,则它必须保持解扰器并接收用于检查Symbol 15的预编码,该符号可以加扰(并预编码)或DC balance pattern。

IMPLEMENTATION NOTE

Sync Header and DC Balance

Block Sync Header 以及TS1和TS2有序集的第一个符号不会影响运行中的DC平衡,因为它们具有相等的1和0。

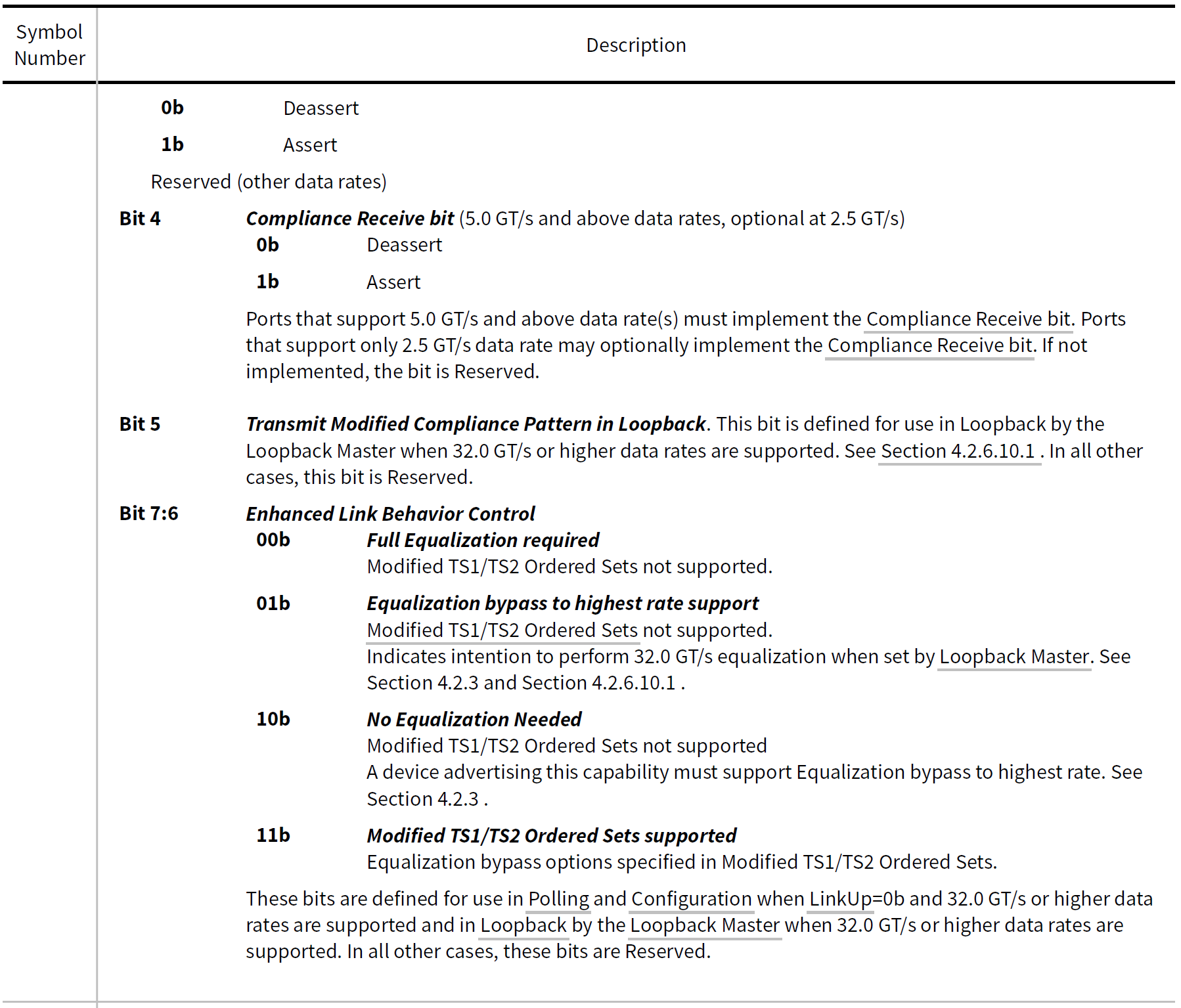

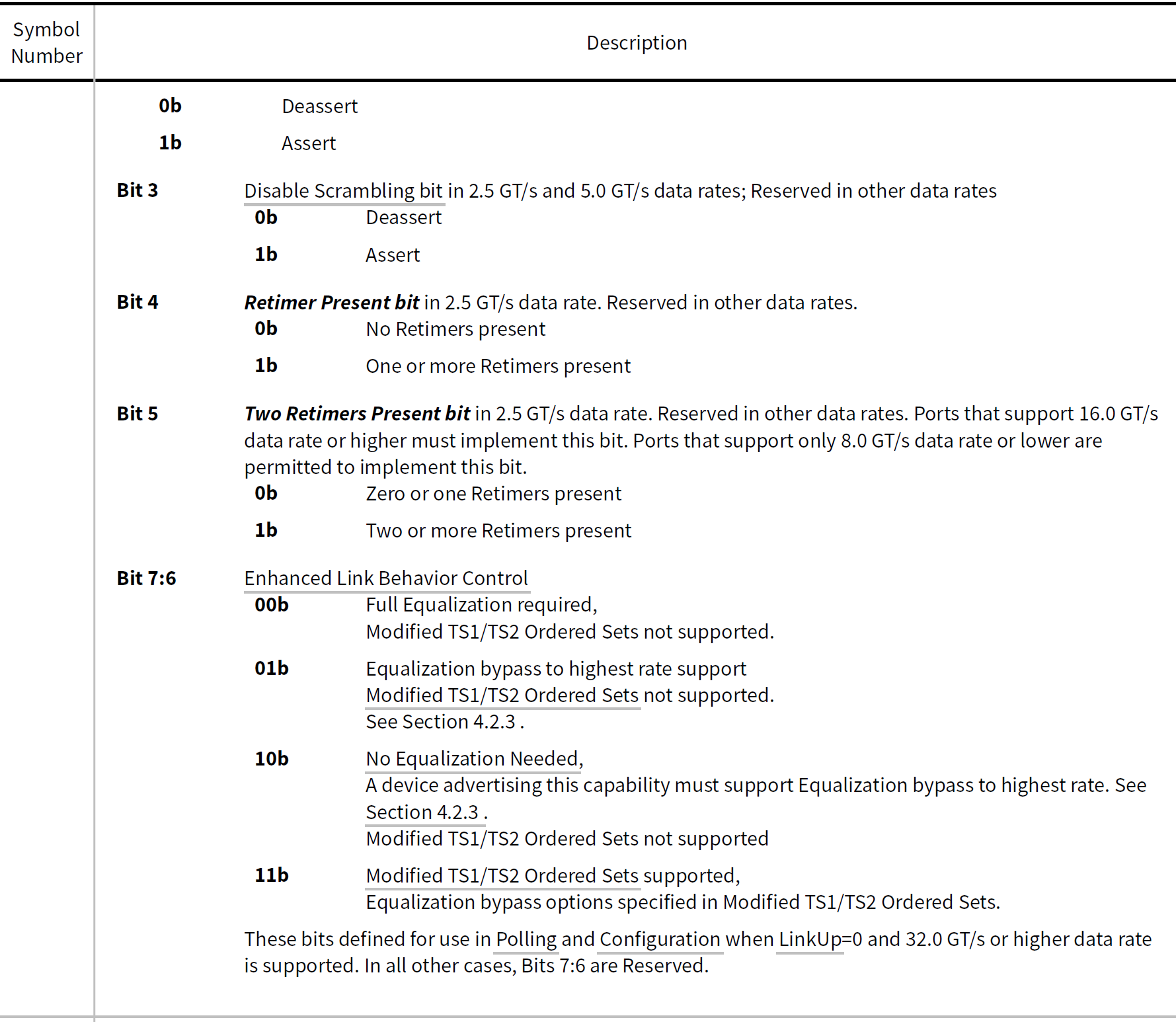

Hot Reset, Disable Link 和 Enable Loopback的控制字段是互斥的,一次只能设置其中一个,并在已配置的所有Lane(LO中的所有Lane)上传输这些字段。如果同时设置了Hot Reset,Disable Link和Enable Loopback,则链路行为不确定。

通过上游端口或下游端口发送时,TS1有序集的Retimer Equalization Extend 字段始终设置为0b。Retimer 按照Section 4.3.7.2中的说明将其设置为1b。

扩展到多个符号上的 Modified TS1/TS2 Ordered Set 中的字段使用little endian格式,该格式使用这些多个符号上的所有位。例如,Modified TS1/TS2 Ordered Set的Symbol 8和9总共16位。Modified TS Usage 字段位于Symbol 8的bit[2:0]中,Modified TS Usage 字段的bit0位于Symbol 8的bit 0中,Modified TS Usage字段的bit 1位于Symbol 8的bit 1中,Modified TS Usage字段的bit 2位于Symbol8的bit2中。类似地,Modified TS Information 1字段的13位的bit 12被放置在Symbol9的bit7中,其中 Modified TS Information 1的bit 0被放置在Symbol 8的bit3中。

4.2.4.2 Alternate Protocol Negotiation

除了跳过均衡外,还可以在 LinkUp=0∼b时的Configuration.Lanenum.Wait, Configuration.Lanenum.Accept 和 Configuration.Complete 子状态期间在8b/10b编码中通过交换 Modified TS1/TS2 Ordered 协商备用协议(Alternate Protocol)。

PCle PHY 可以在128b/130b编码支持备用协议。备用协议是使用PCle PHY层定义的一种non-PCle协议。在备用协议模式下,可以选择在运行PCle协议之外运行一种或多种备用协议。Ordered Set块与SKP Ordered Set插入的规则以及Ordered Set和 Data Blocks 之间的过渡一起使用。但是,可以根据备用协议的规则修改数据块的内容。

IMPLEMENTATION NOTE

Alternate Protocols should have an EDS Token Equivalent

EDS Tok在PCI Express中用于指示从数据块到有序集块的切换。此附加的“冗余”信息可确保2比特的block header 中的随机位错误不会被错误地解释为数据流的末尾。这是PCI Express使用的一种机制,可实现4单位的无误数据错误汉明距离。

备用协议应具有等效的机制。

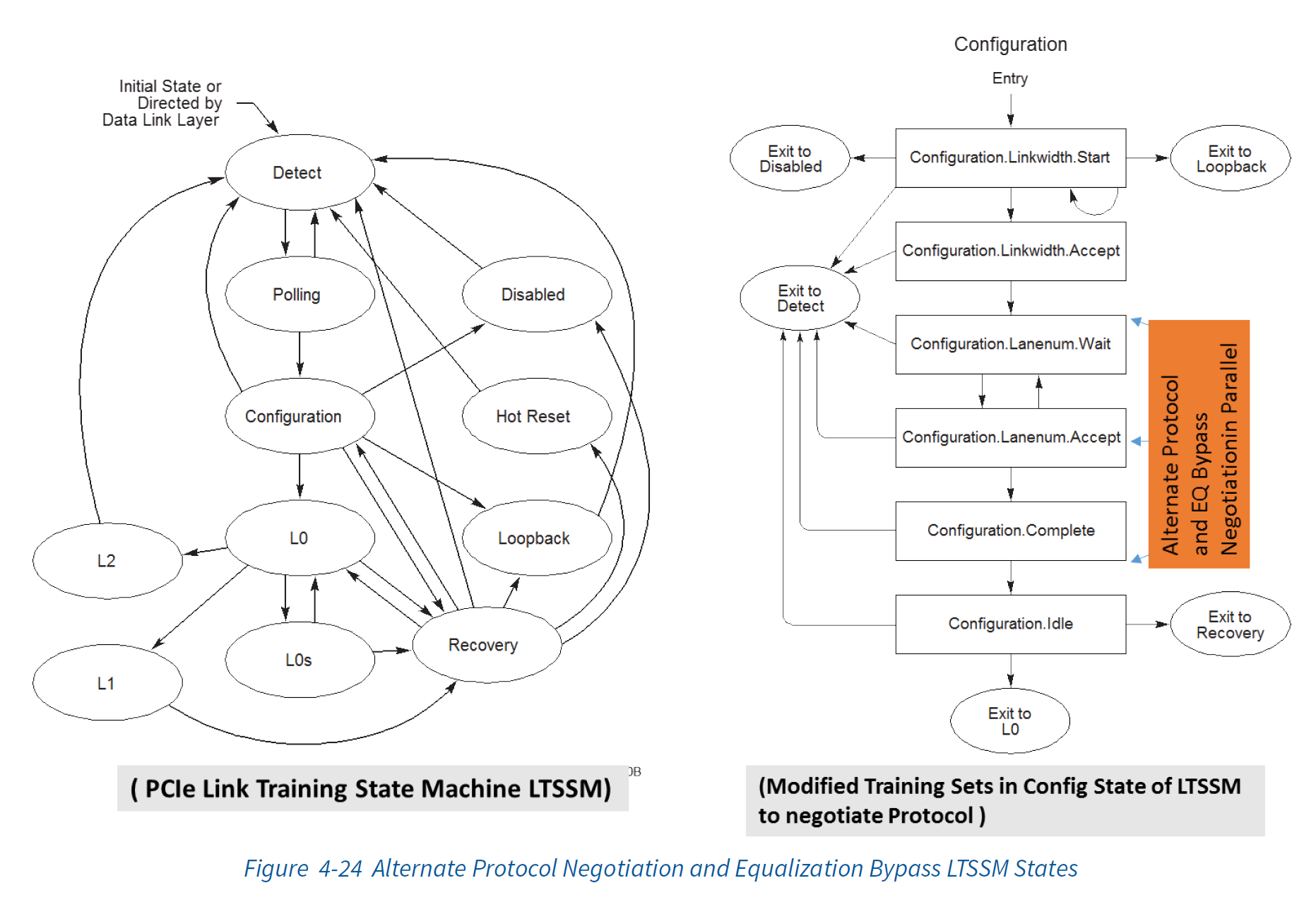

下图表示发生备用协议和均衡旁路协商的状态:

当端口处于LinkUp=0的Configuration.Lanenum.Wait、Configuration.Lanenum.Accept和Configuration.Complete 子状态时,下游端☐根据Modified TS Usage Mode Selected 字段的值来管理 Alternate Protocol Negotiation和Training Set Message。

上游端口必须通过传输000b的Modified TS Usage 值来响应不受支持的Modified TS Usage。

如果 Modified TS Usage Mode Selected 值为:

000b

没有备用协议协商或训练集消息发生。该链路将用作PCI Express链接。

001b

Training Set Message 被启用。Modified TS Information 1和 Modified TS Information 2 字段携带由 Training Set Message Vendor ID字段定义的特定于供应商的消息。

010b

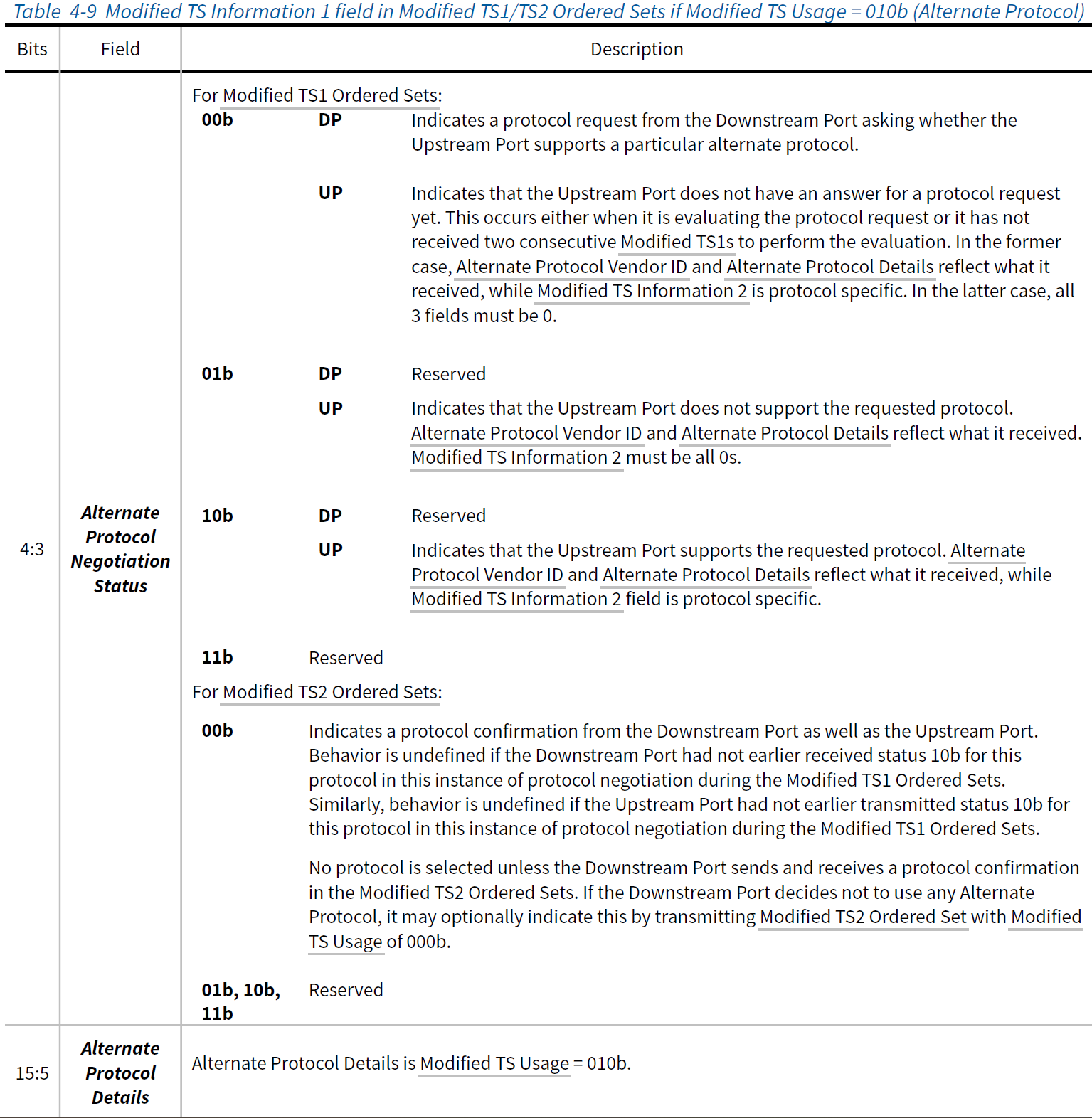

Alternate Protocol Negotiation 被启用。Modified TS Information 1和 Modified TS Information 2 字段携带由 Alternate Protocol Vendor ID字段定义的备用协议详细信息。协议请求或响应与Alternate Protocol Detail 和Alternate Protocol Vendor ID 确定的协议相关联。协议请求或响应与Alternate Protocol Vendor ID 字段定义的协议相关联。

Alternate Protocol Negotiation Status 字段指示协商协议的进度。

others

Reserved

支持 Alternate Protocol Negotiation的下游端口在首次进入 Configuration.Lanenum.Wait, LinkUp =0且 Modified TS Usage Mode Selected字段为010b时,将启动协商过程。开始协商包括发送Modified TS Usage = 010b的Modified TS1/TS2 Ordered Set。

如果 Modified TS Usage =001b,则 Modified TS Information 1和 Modified TS Information 2 包含训练集消息的详细信息。

备用协议协商必须与通道编号协商同时进行。DP负责确保在过渡到Configuration.Complete子状态之前,他们就备用协议协商达成共识。如果备用协议协商未达成共识,则允许回退到PCle协议。在成功协商备用协议后,链路将以2.5GT/s的速率切换到LO,之后将数据速率切换至更高的数据速率,并在需要时执行均衡,并以所需的最高数据速率进入LO。在执行均衡后,以最高数据速率发送SDS有序集后,数据块将携带替代协议,并且链路将处于替代协议的控制之下。

4.2.4.3 Electrical Idle Sequences

除非另有规定,否则发送器进入电气空闲前,必须始终发送Electrical Idle Ordered Set Sequence(EIOSQ)。如果当前数据速率为2.5 GT/s、8.0 GT/s、16.0 GT/s或32.0 GT/s,则定义为一个EIOS;如果当前数据速率为5.0 GT/s,则定义为两个连续EIOS。

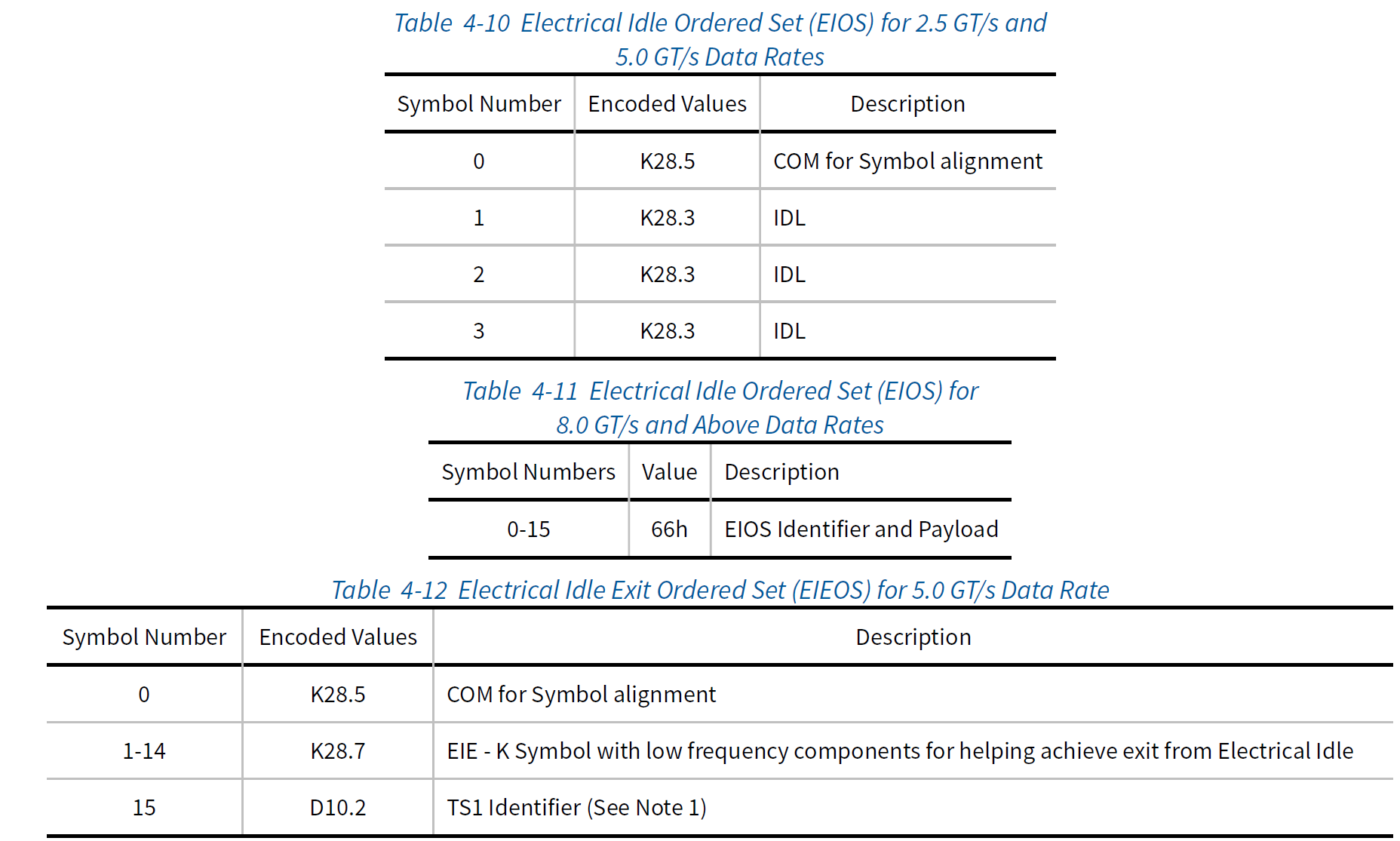

使用8b/10b编码时,EIOS是K28.5(COM),后跟三个K28.3(IDL)符号。发送器必须发送EIOS的所有符号。当收到COM和三个IDL符号中的两个时,就认为收到EIOS。当使用128b/130b编码时,EIOS是一个有序集块,如Table 4-11所定义。如果要在其后发送其他EIOS,则发送端必须发送EIOS的所有符号。否则,发送器必须发送EIOS的Symbol 0-13,但允许在Symbol 14或Symbol 15中的任何地方终止EIOS,之后链路过渡到电气空闲状态。当有序集块的Symbol 0-3与EIOS的定义匹配时,则认为已接收到EIOS。

IMPLEMENTATION NOTE

Truncation of EIOS Ordered Set

最后的EIOS的截断可帮助实现以下实现:发送器可能终止于内部时钟边界,由于128b/130b编码,该内部时钟边界可能无法与符号边界对齐。截断是可以的,因为接收方只需查看前四个符号即可得出它是EIOS的结论。

传输完最后一个电气空闲有序集的最后一个符号后,发送器必须处于TTx-IDLE-SET-TO-IDLE指定的有效电气空闲状态(见Table 8-7)。

仅当以2.5 GT/s以外的速度运行时,才会发送EIEOS。它是周期性发送的低频的pattern,有助于确保接收机的电空闲出口电路可以检测到电空闲的退出。当使用128b/130b编码时,它也可用于块对齐,如Section 4.2.2.2.1所述。

数据速率为32.0GT/s及以上时电气空闲退出有序集序列(EIEOSQ)包括两个连续的EIEOS,数据速率为5.0GT/s,8.0 GT/s和16.0GT/s时为一个EIEOS。必须将两个以32.0GT/s的速度运行的EIEOS背对背并不能中断,才能被认为是连续的并形成一个EIEOSQ。不管EIEOSQ的长度如何,在EIEOS上仍然会发生块对齐。

当在5GT/s下运行,EIEOSQ(Table 4-2)的规则如下:

-

进入LTSSM的Configuration.Linkwidth.Start状态后,在发送第一个TS1有序集之前会发送EIEOS。

-

进入LTSSM的Recovery.RcvrLock状态后,在发送第一个TS1有序集之前会发送 EIEOS。

-

在LTSSM的Configuration.Linkwidth.Start,Recovery.RcvrLock和Recovery.RcvrCfg状态中每发送32个TS1或TS2有序集之后。在以下情况下,TS1/TS2计数会设置为0:

-

发送了一个EIEOS。

-

在LTSSM的Recovery.RcvrCfg状态收到第一个TS2序列。

-

-

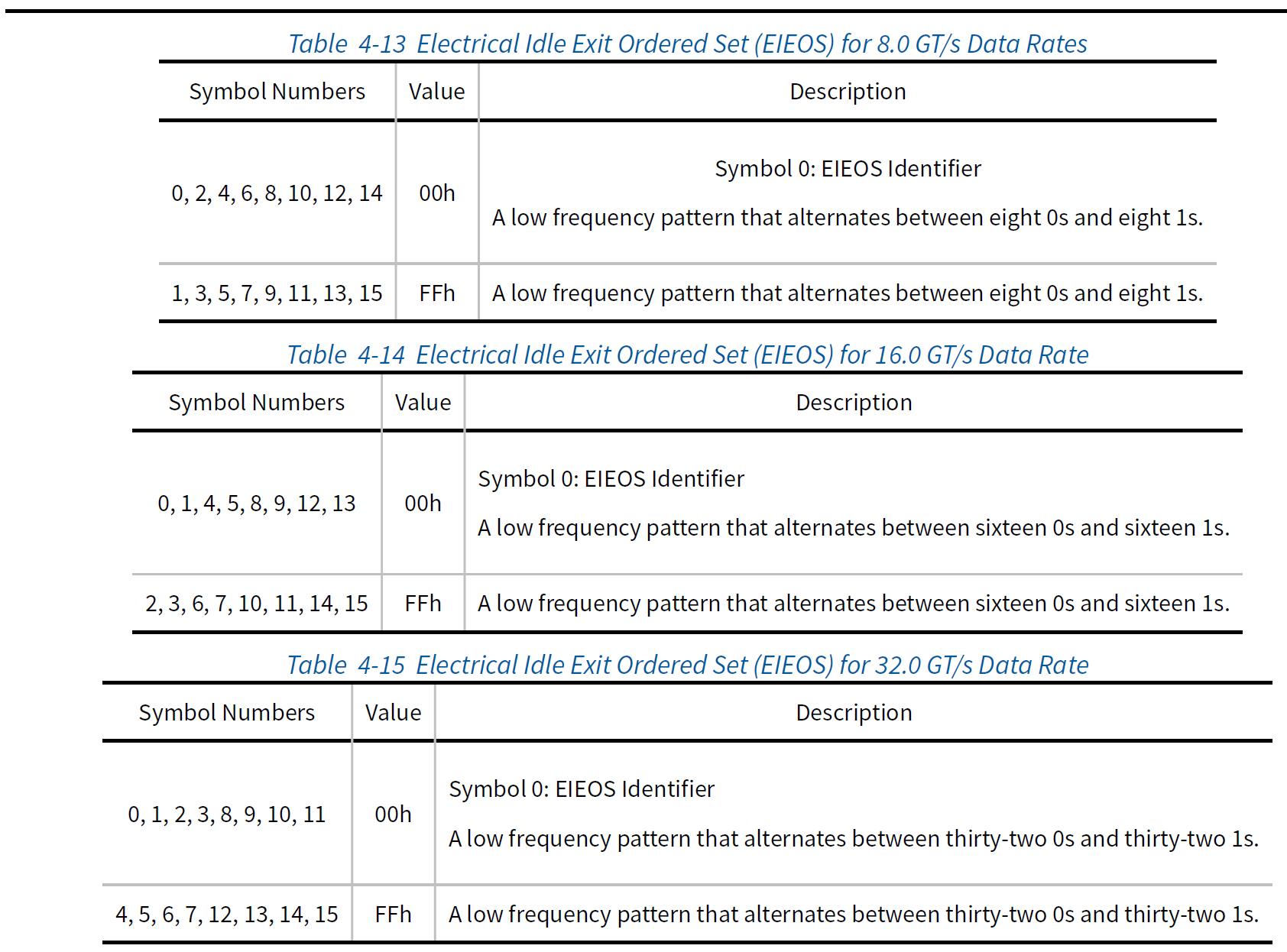

当采用128b/130b编码时,EIEOSQ (Table 4-13到Table 4-15和 Figure 4-25)的规则如下:

-

进入LTSSM的Configuration.Linkwidth.Start 状态后,在发送第一个TS1有序集之前会发送EIEOS。

-

进入LTSSM的Recovery.RcvrLock状态后,在发送第一个TS1有序集之前会发送EIEOS。

-

在结束数据流且不发送EIOS且未进入LTSSM的Recovery.RcvrLock子状态时,紧随EDS Framing Token之后会发送EIEOS。

-

所有需要传输TS1或TS2有序集的LTSSM状态下,每32个TS1或TS2有序集发送之后。在以下情况下,TS1/TS2计数会设置为0:

-

发送了一个EIEOS。

、 -

在LTSSM的Recovery.RcvrCfg状态收到第一个TS2序列。

-

在LTSSM的Configuration.Complete 状态收到第一个TS2序列。

-

下游端口处于LTSSM的Recovery.Equalization状态的Phase

2,且在任意Lane上收到的两个连续的TS1有序集中的Reset EIEOS Interval Count 字段设置为1。 -

上游端口处于LTSSM的Recovery.Equalization 状态的Phase 3,且在任意Lane上收到的两个连续的TS1有序集中的Reset EIEOS Interval Count 字段设置为1。

-

-

在LTSSM的Recovery.Equalization 状态下每发送65,536个TS1有序集之后,如果Reset EIEOS

Interval Count阻止了该间隔的发送,则将在此状态下发送。允许实现通过在加扰LFSR匹配其种子值时在两个TS1有序集中发送EIEOS来满足此要求。 -

作为相关部分中所述的FTS Ordered Set、Compliance Pattern 或Modified Compliance

pattern的一部分发送。

Example:LTSSM以5.0 GT/s的数据速率从LO切换到Recovery.RcvrLock。它先传输一个EIEOS,然后传输TS1有序集。它发送32个TS1有序集,之后发送第二个EIEOS。随后,它再发送两个TS1有序集,并进入Recovery.RcvrCfg,在传输30个TS2有序集后,接着传输第三个EIEOS。当收到TS2有序集时,它将在Recovery.RcvrCfg中再发送31个TS2有序集(在前30个TS2有序集之后)。由于它接收到第一个TS2有序集,因此它将EIEOS interval count清为0,并在继续向Recovery.ldle 转换之前继续发送另外16个TS2有序集。因此,由于EIEOS interval count 已重置为0b,因此在最后47个TS2有序集中间未发送EIEOS。LTSSM从 Recovery.Idle 切换到Configuration.Linkwidth.Start 并传输EIEOS,此后它开始传输TS1有序集。

以2.5GT/s以外的速度运行时,允许实现不依赖电空闲检测电路的输出,除非在某些LTSSM状态期间接收EIEOS,或在Rx LOs或Polling.Compliance 期间在接收器处接收到由四个连续EIE符号(见 Section 4.2.4.6)预先提供的FTS。

4.2.4.4 Inferring Electrical Idle

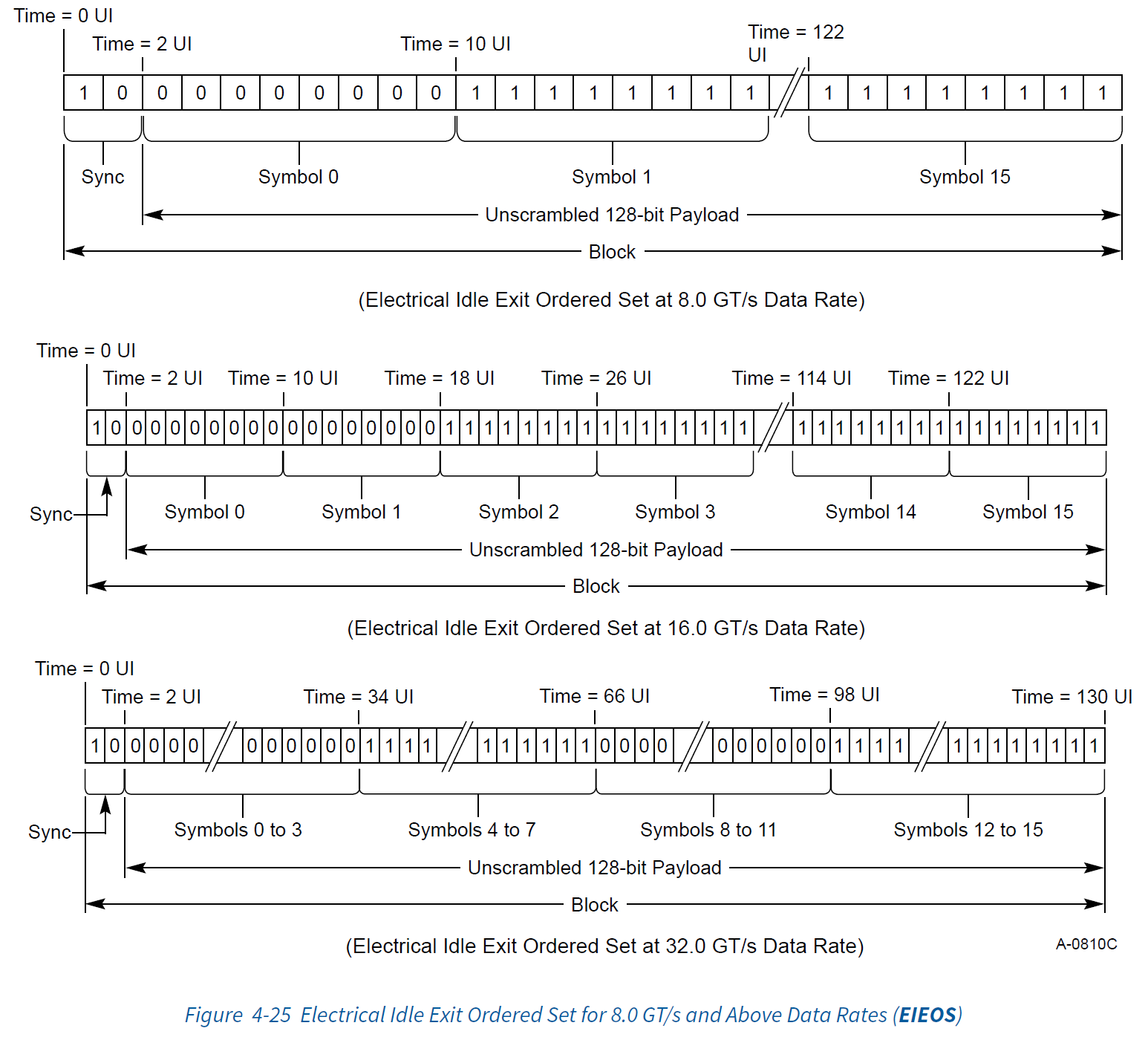

允许设备在所有操作速度下推断电气空闲状态,而不是使用模拟电路检测电气空闲状态。Table 4-16总结了推断各种子状态下的电气空闲的条件。

注56,57,58:Flow Control Update DLLP是本规范中定义的UpdateFC或[MR-IOV]中定义的MRUpdateFC。

不得基于对电气空闲条件的推断来确定电气空闲出口条件。考虑到电路面积因素,允许选择为每个LTSSM实现一个公共的超时计数器,并在LTSSM控制的每个Lane的公共计数器确定的公共超时窗口内查找电气空闲推断条件,而不用为每条Lane设置超时计数器。

IMPLEMENTATION NOTE

Inference of Electrical Idle

在LO状态下,期望在 128μs窗口中接收到一定数量的流控制更新DLLP。同样在LO中,预计将平均以2.5 GT/s和5.0 GT/s的数据速率每发送1538个符号,并以8.0GT/s的数据速率平均发送375个块。为简化起见,允许使用这些指示器中的一个(或两个)来推断电气空闲。因此,可以将在任何 128μs窗口中不存在流控制更新DLLP或SKP有序集的情况推断为电气空闲。通过成功的速度协商,在Recovery.RcvrCfg以及Recovery.Speed中,接收方应连续接收TS1或TS2有序集,但EIEOS和SKP有序集除外。因此,对于实现推断机制的组件,必须在上述指定的间隔内不存在TS1或TS2有序集。如果设备以success_speed_negotiation =0b 进入Recovery.Speed,则设备可能无法接收符号。因此,电空闲推断是在没有电气空闲退出的情况下完成的。在非2.5GT/s的数据速率下,只有在收到EIEOS时才能保证电空闲退出。因此,该窗口设置为16000UI,用于以5.0GT/s和8.0GT/s的数据速率检测从电气空闲退出。在2.5GT/s的数据速率下,必须在收到每个符号后检测到电气空闲出口。因此,在2000UI窗口中没有电空闲出口就构成了电气空闲条件。

4.2.4.5 Lane Polarity Inversion

在Polling过程中,接收器将TS1和TS2有序集的Symbol 6-15视为通道极性反转的指示符(D+和D-被交换)。如果发生通道极性反转,则收到的TS1的Symbol 6-15的值为D21.5,而不是预期的 D10.2。 同样,如果发生通道极性反转,则TS2有序集的Symbol 6-15为D26.5,而不是预期的D5.2。

如果检测到通道反转,则接收器必须反转接收到的数据。发送器绝不能反转发送的数据。所有通道上的所有PCI Express接收器都需要独立支持通道极性反转。

4.2.4.6 Fast Training Sequence (FTS)

快速训练序列(FTS,Fast Training Sequence)是从LOs过渡到LO时用于比特锁定和符号锁定的机制。接收器使用FTS来检测从电气空闲状态的退出,并将接收器的bit and Symbol receive circuitry与输入数据对齐。有关LOs和LO的说明,请参见Section 4.2.5。

对于2.5GT/s和5GT/s速率:

一个FTS包含一个K28.5(COM)符号,然后是三个K28.1符号。组件可以请求的FTS(NTS)的最大数量为255,提供4255*10UI的时间用于bite锁定。如果数据速率为5.0GT/s,则在发送第一个FTS之前以有效信号电平发送四个连续的EIE符号。这些符号将帮助接收器检测到从电气空闲状态退出。由于退出电气空闲状态需要在其第一个FTS之前加上额外的EIE符号,因此该实现不能保证在发送器引脚上的信号在允许的时间内达到合适的电平(见Table 4-18),因此接收器至少可以接收有效信号电平下的四个EIE符号。在传输第一个FTS之前,实现不得传输八个以上的EIE符号。允许组件在不同的速率下通告不同的N_FTS 速率。在5.0GT/s的速度下,组件可以选择通告合适的N_FTS值,因为它将接收到四个EIE符号。如果Link Control寄存器的Extended Synch字段被设置,则必须发送4096个FTS,以便为外部链路监视工具提供足够的时间来实现比特同步和帧同步。为了满足Section 4.2.7中的定义,必须在FTS之间调度和传输SKP有序集,但在第一个N_FTS FTS期间不能传输SKP有序集。最后一个FTS传输后,始终发送单个SKP有序集。请注意,有可能可以背对背传输两个SKP有序集(一个SKP有序集表示4096个FTS的完成,而一个SKP有序集则进行了调度和传输以满足Section 4.2.7中描述的定义)。

注:N_FTS表示FTS的个数,在TS1和TS2序列的Symbol3中通告。

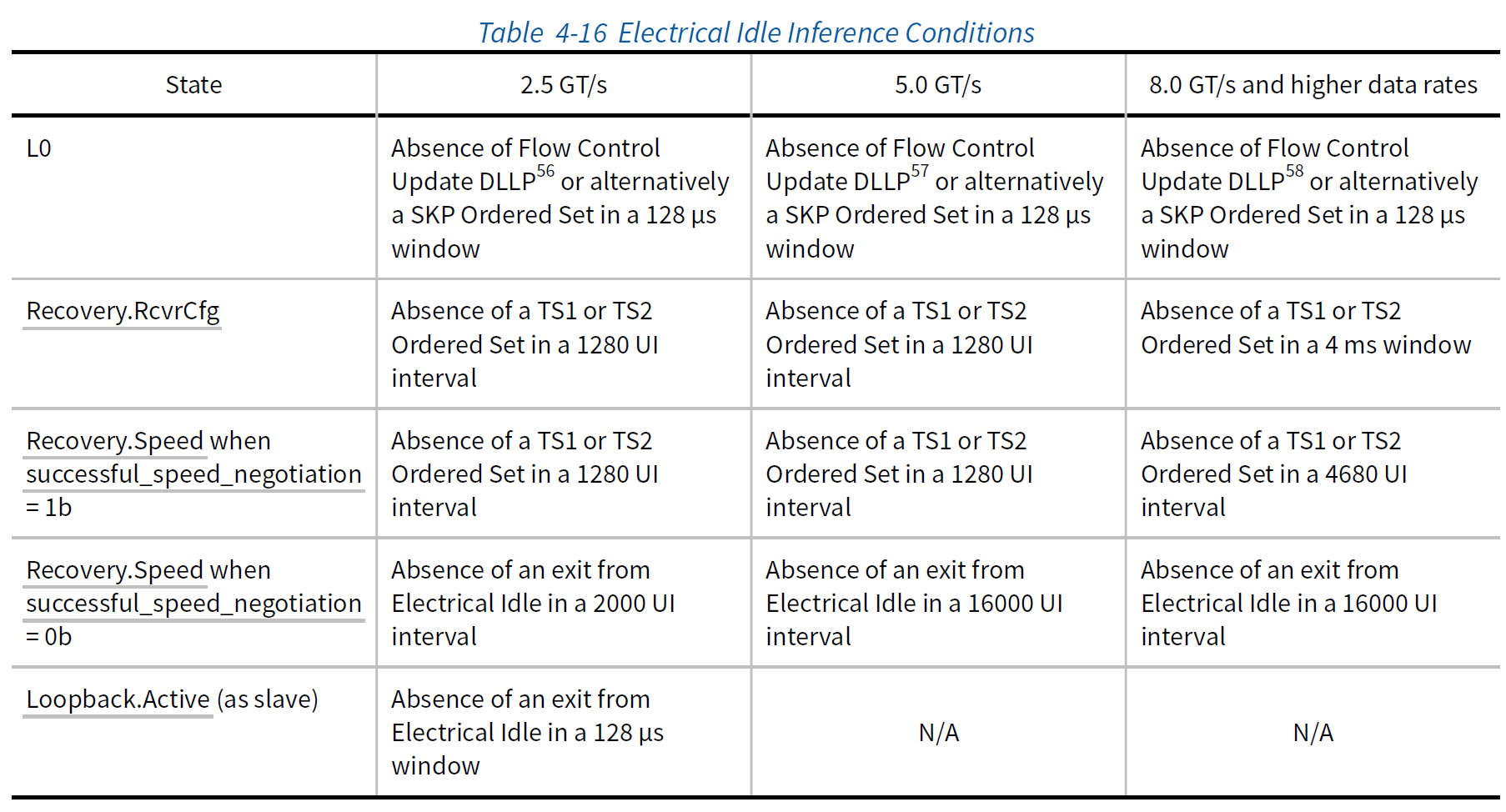

·对于8GT/s和以上速率:

单个FTS是一个130位不加扰的有序集块,如Table 4-17所示。组件可以请求的FTS(NTS)的最大数量为255,提供 130255UI(如果包括周期性 EIEOS,则为 130263UI)的时间用于比特锁定。允许组件在不同的速度下通告不同的 NT值。从LOs 退出时,发送器首先发送一个EIEOSQ,该块将帮助接收器检测到由于其低频成分而退出电气空闲的情况。在第一个EIEOSQ之后,发送器必须发送所需数量的FTS(设置Link Control寄存器的Extended Synch字段时为4096;否则为NN_FTS),每32个FTS之后发送一次EIEOSQ。FTS序列将使接收器获得比特锁定(并且可以选择进行块对齐)。设置Extended Synch字段后,要根据 Section 4.2.7描述的规则,在FTS和EIEOSQ之间调度传输SKP有序集。如果有的话,FTS序列的最后一个FTS有序集(如果N_FTS等于零,则不发送FTS有序集)后跟最后一个EIEOSQ,它将帮助接收器实现块对齐。如果 NTS 是32的倍数,则即使在最后一个FTS有序集之后的数据速率低于32.0GT/s的情况下,实现也可以背对背发送两个EIEOS。EIEOS重置发送器和接收器中的加扰器。在最终的EIEOSQ之后,将发送SDS有序集,以帮助接收器执行de-skew并指示从有序集到数据流的过渡。在发送SDS有序集之后,必须发送一个数据块。

IMPLEMENTATION NOTE

Scrambling LFSR During FTS Transmission in 128b/130b Encoding

由于加扰器在最后一个EIEOS上重置,并且FTS序列中的任何有序集都没有被加扰,因此在接收FTS期间,实现是否选择推进加扰器不重要。

N_FTS定义了从LOs切换到LO时必须发送的FTS的数量。在2.5GT/s的数据速率下,组件可以请求的用于Symbol Lock的时间对应于16ns(N_FTS设置为0b和一个SKP有序集)~4μs(N_FTS设置为255),当设置Extended Synch字段时,需要发送4096个FTS,导致bit lock时间为64μs。对于8.0GT/s和更高的数据速率,将Extended Synch字段设置为1时,要求发送器发送4096个FTS有序集块。请注意,组件报告的N_FTS值可能会更改;例如,由于软件修改了Common Clock Configuration字段(Section 7.5.3.7)的值。

如果在接收器获得bit lock、Symbol lock 或Block alignment 以及 Lane-to-Lane de-skew 之前,N_FTS时间已用完,则接收器必须切换到Recovery状态。该过程在LTSSM的Section 4.2.5中有详细说明。

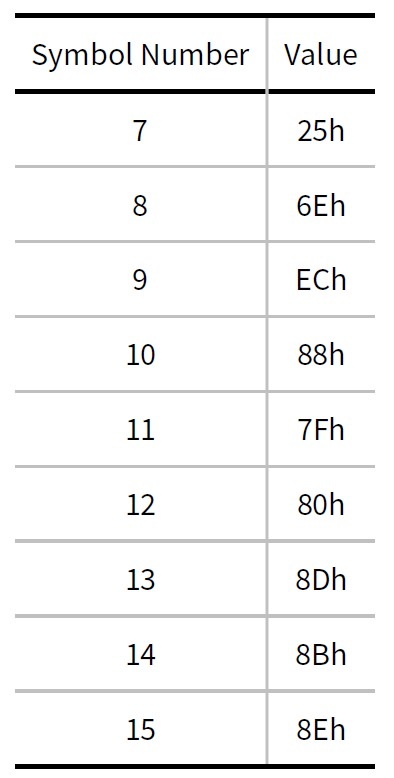

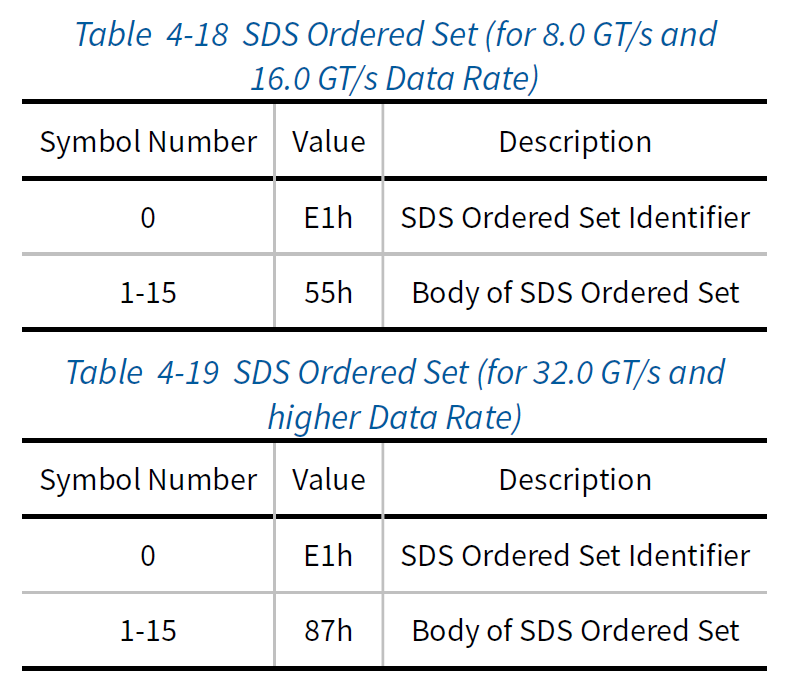

4.2.4.7 Start of Data Stream Ordered Set

Table 4-18和Table 4-19中描述的Start of Data Stream(SDS)有序集仅针对128b/130b编码定义。它在Configuration.Idle, Recovery.Idle 和Tx_LOs.FTS等LTSSM状态中使用,以定义从有序集块到数据流的过渡,并且允许Loopback Masters 按照 Section 4.2.2.6中的描述进行传输。不得在其他时间传输该有序集。在处于非环回状态时,SDS有序集之后的块必须是数据块,并且该数据块的第一个符号是数据流的第一个符号。

4.2.4.8 Link Error Recovery

-

如果在8b/10b编码下发生 Link Errors:

- 包括8b/10b解码错误,Framing Errors, loss of Symbol lock, Elasticity Buffer Overflow/Underflow,以及 loss of Lane-to-Lane de-skew。

- 必须检查8b/10b解码错误,并在指定的LTSSM状态下触发 Receiver Error(请参见Table4-20),这是与端口相关的reported error(请参见Section 6.2)。任何其它 Framing Error、Loss of Symbol Lock、Lane Deskew Error 和 Elasticity Buffer Overflow/Underflow 触发的Receiver Error都是可选择实现的。

-

如果在128b/130b编码下发生 LinkErrors:

- 包括 Framing Errors、loss of Block Alignment、Elasticity Buffer Overflow/Underflow 或者 loss of Lane-to-Lane de-skew。

- 必须检查 Framing Errors,并在指定的LTSSM状态下触发 Receiver Error(请参见Table4-20),这是与端口相关的reported error(请参见 Section 6.2)。任何其它Block Alignment、Elasticity Buffer Overflow/Underflow 和 loss of Lane-to-Lane de-skew 触发的Receiver Error都是可选择实现的。

-

在一个已配置完成且进入LO状态的链路上,可以通过指示链路切换到Recovery状态,这个功能需要在物理层之上的层中实现(如Section3.6所述)。

- 注意:链路错误也可能导致物理层启动从LO到Recovery的转换。

-

发生链路错误时,除LO以外的所有LTSSM状态都会执行Link Error Recovery(根据上下文,除Detect、Hot Reset、Disabled 外)。

-

当使用8b/10b编码进行操作时,非LO的LTSSM状态中发生的链路错误一定不会导致物理层启动LTSSM状态转换。

-

当使用128b/130b编码进行操作且不处理数据流时,非LO的LTSSM状态中发生的链路错误一定不会导致物理层启动LTSSM状态转换。

-

-

使用8b/10b编码进行操作时,如果Lane检测到实现特定数量的8b/10b错误,则必须尽快检验或重新建立符号锁定。检验和重新建立符号锁定的方法是特定于实现的。

4.2.4.9 Reset

Section 6.6从系统角度描述了复位。

4.2.4.9.1 Fundamental Reset

当Fundamental Reset 有效时:

- 接收器终端负载要满足 ZRX-HIGH-IMP-DC-POS和ZRX-HIGH-IMP-DC-NEG(请参阅Table 8-10)。

- 发送器只需要满足ITx-SHORT(Table 8-7)。

- 发送器维持一个常量的DC共模电压。

当Fundamental Reset释放后:

- 该端口的LTSSM完成初始化(参阅Section 4.2.5和 Section 6.6.1)。

4.2.4.9.2 Hot Reset

Hot Reset的规范在Section 4.2.5.11定义。

4.2.4.10 Link Data Rate Negotiation

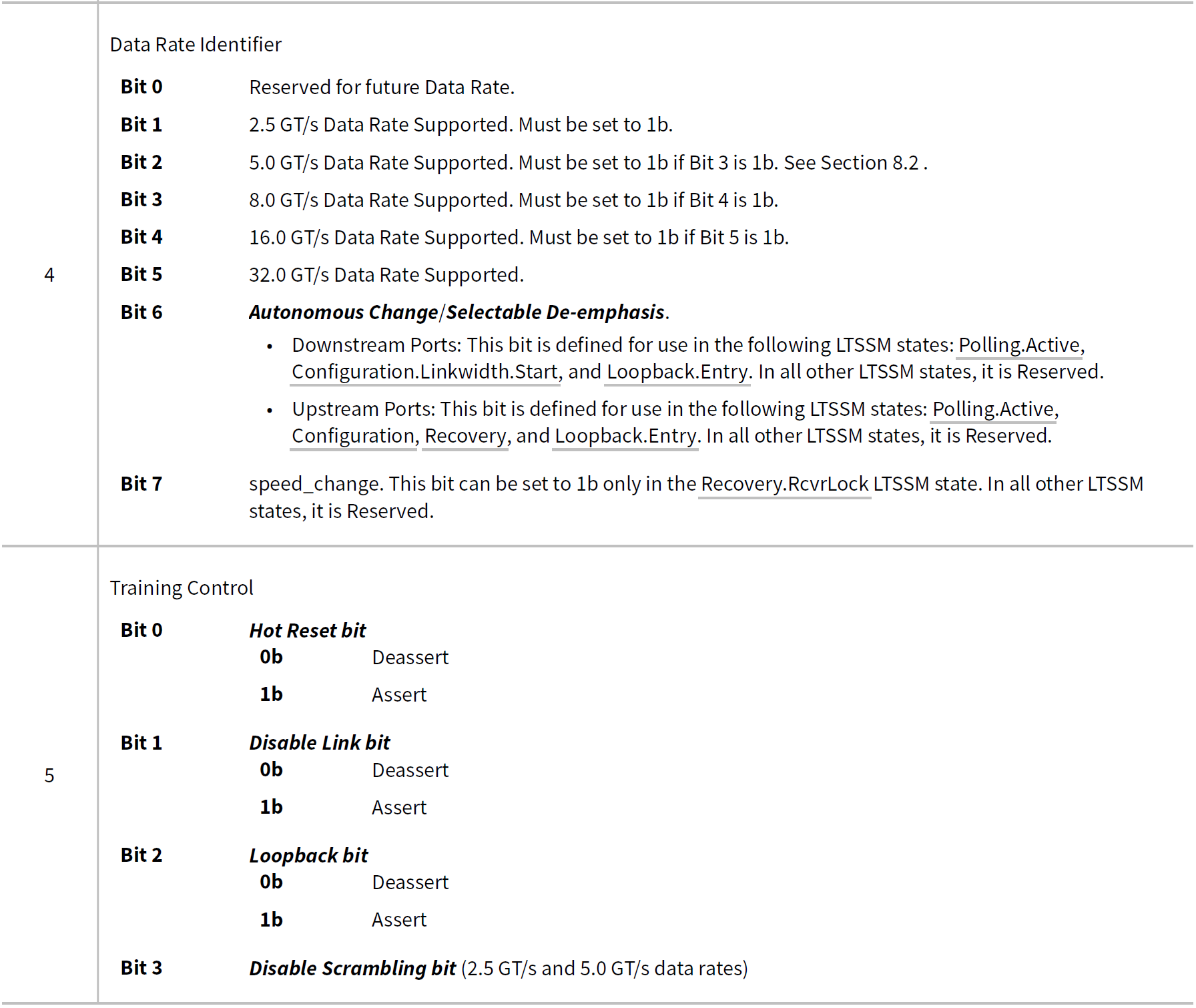

要求所有设备在每个通道上以2.5GT/s的数据速率开始链路初始化。TS1和TS2(请参阅Section 4.2.4.1)中的Symbol 4用于通告所有支持的数据速率。链路最初以2.5GT/s的数据速率训练到LO,此后通过进入Recovery状态来切换数据速率。

4.2.4.11 Link Width and Lane Sequence Negotiation

PCI Express 链路必须由并行的1、2、4、8、12、16或32通道组成,分别称为x1,x2,x4,x8,x12,x16和x32链路。链路中的所有通道必须同时基于相同的频率传输数据,并且通道之间的时滞不得超过LTx-SKEw(Table 8-10)。协商过程有很多步骤。

协商为有效链路的每个通道建立Link number和 Lane number值;每个不属于有效链路的通道都将退出协商,以成为分离的链路或保持在电气空闲状态。

在Link width和Lane number 协商期间,两个通信端口必须满足Table 8-10中 LRx-skEw指定的最大的Lane-to-Lane skew值。

可选的链路协商行为包括通道反转,可变宽度的链路,将端口拆分为多个链路以及交叉链路的配置。

其他规范可能会施加其他规则和限制,而这些规则和限制必须由那些符合这些其他规范的组件来理解;本规范的目的是理解各种组件功能的互操作性。

4.2.4.11.1 Required and Optional Port Behavior

- xN端口需要有组成xN链路和x1链路(其中N可以是32、16、12、8、4、2和1)的能力。

- 设计人员必须以允许这些组件满足上述要求的方式连接两个不同组件之间的端口。如果组件之间的端口连接方式与组件的端口说明/数据表中定义的预期用途不一致,则行为未定义。

- xN端口组成N到1之间的任何链路宽度的能力是可选的。

- 比如一个x16端口,该端口只能配置为一个链路,但是链路的宽度可以配置为x12,x8,x4,x2以及所需的x16和x1。

- 一个端口拆分成多个链路的功能是可选的。

- 比如一个x16端口,该端口可能能够配置两个x8链接,四个x4链接或16个x1链接。

- 通道反转功能是可选的。

- 如果实现,则必须对多通道链路的给定端口的发送器和接收器都进行通道反转。

- 通道反转的示例为下游端口的Lane N-1连接到上游端口的Lane 0,其中下游或上游设备可以颠倒通道顺序以配置xN 链接。

交叉链路功能是可选的。在这种情况下,连接到下游端口的下游端口或连接到上游端口的上游端口是交叉链接。

当前和将来的机械特性和/或形状因数规格可能需要实现上面列出的一些可选功能。组件设计者必须阅读他们正在设计的组件所使用的系统的规格,以确保符合这些规格。

4.2.4.12 Lane-to-Lane De-skew

在将数据和控制传送到数据链路层之前,接收器必须补偿多通道链路中所有通道之间允许的skew(请参见 Table 8-7和Table 8-10)。

当使用8b/10b编码时,Lane-to-Lane de-skew机制可以使用以下一项或多项来实现:

- The COM Symbol of a received TS1 or TS2 Ordered Set

- The COM Symbol of a received Electrical Idle Exit Ordered Set

- The COM Symbol of the first received SKP Ordered Set after an FTS sequence

- The COM Symbol of a received SKP Ordered Set during a training sequence when not using SRIS

使用128b/130b编码时,Lane-to-Lane de-skew机制可以使用以下一项或多项来实现:

- A received SDS Ordered Set

- A received Electrical Idle Exit Ordered Set

- A received SKP Ordered Set

也可以采用其他de-skew机制。Lane-to-Lane de-skew必须在LTSSM的 Configuration、Recovery、和LOs状态执行。

IMPLEMENTATION NOTE

Unambiguous Lane-to-Lane De-Skew:

接收器必须能够消除的2.5 GT/s的max skew为20ns。标准的SKP有序集(即没有通过Retimer添加或删除的SKP符号)的长度为4个符号,即16ns,速率为2.5GT/s。通常,SKP有序集的传输使得它们间隔良好,并且不需要特别注意将它们的skew,即,它们提供了明确的机制。如果传输了背对背的SKP有序集,则仅查找SKP有序集的COM出现在同一时间的每个通道上的实现可能会失败。当退出LOs时,发送器可以在快速训练序列的最后一个FTS有序集合之后发送背对背的SKP有序集合。必须在LOs中实现De-skew,因此在这种情况下执行De-skew时,实现必须理解背靠背的SKP有序集。

Section 4.2.4.12中明确机制的例外会发生,因为可能会发送背对背有序集,即,当使用128b/130b编码退出LOs时,可能会背对背发送EIEOS。在这种情况下,EIEOS仍可用于de-skew,但是,执行de-skew时,实现必须包含背靠背EIEOS。

当以16.0 GT/s或更高的数据速率运行时,发送器可以在训练序列结束时发送背对背的SKP有序集,例如TS2有序集,SKP有序集,SKP有序集,SDS有序集。建议在这种情况下选择使用SKP有序集进行de-skew的实现,以认识到背对背SKP有序集是不同的,即标准SKP有序集和控制SKP有序集。

4.2.4.13 Lane vs. Link Training

链路初始化过程将端口的未关联通道构建为链路的关联通道以构造链路。为了使通道正确配置为所需的链路,TS1和TS2有序集必须在所有通道上将适当的字段(Symbol3、4和5)设置为相同的值。

Configuration 状态完成后会形成链路。

如果Port实现了可以配置成多条链路的功能,则可以观察到以下情况:

- 每个单独的链路,都需要单独的LTSSM。

- LTSSM规则只用于配置一个链路。在多条链路的情况下,以串行或并行方式配置链路的决定是特定于实现的。

4.2.5 Link Training and Status State Machine (LTSSM) Descriptions

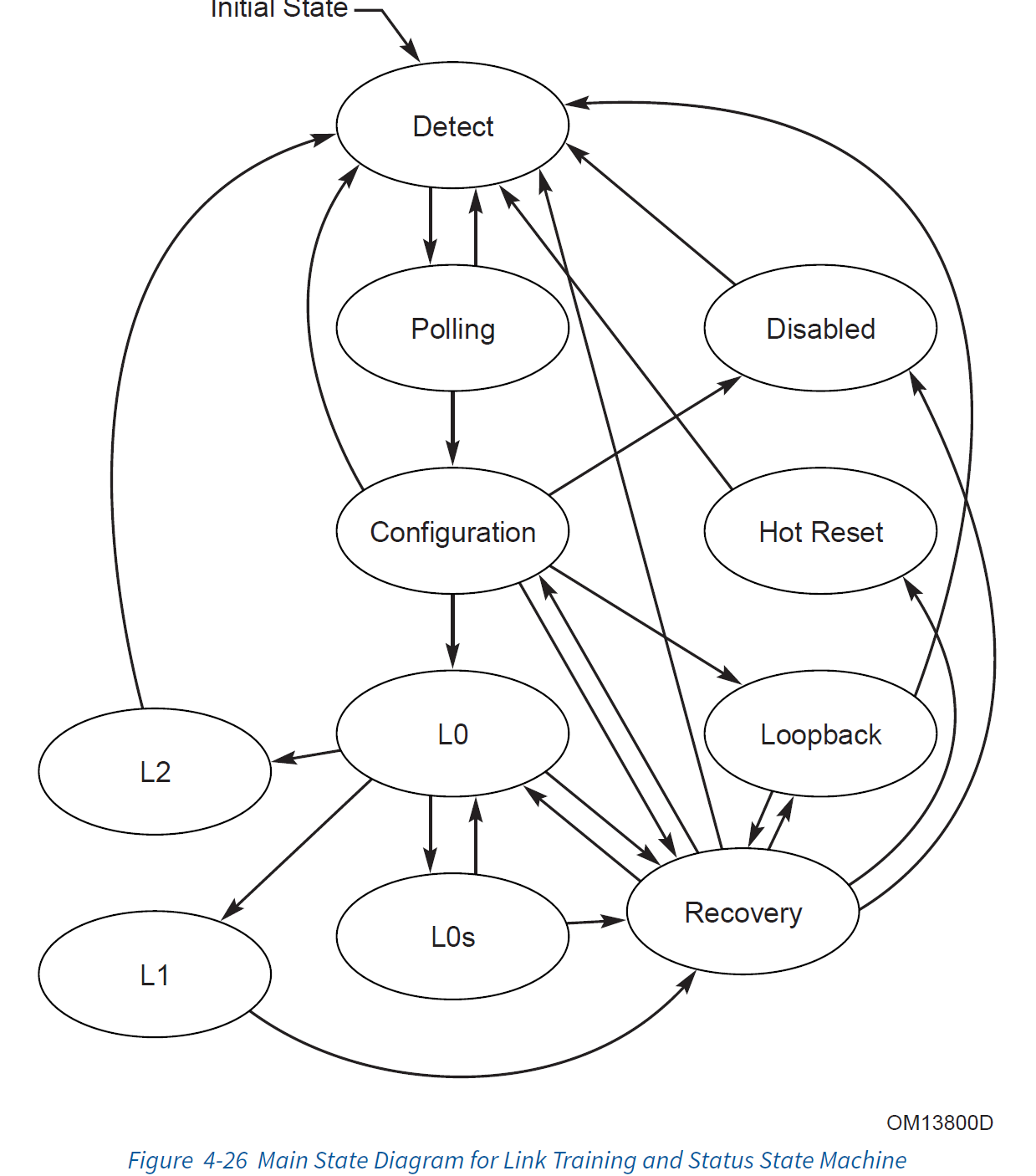

LTSSM状态如Figure 4-26所示。这些状态将在以下各节中介绍。

除非另有明确说明,否则为LTSSM指定的所有超时值均为负0秒加50%。Fundamental Reset后,所有超时值必须设置为指定的值。Fundamental Reset后,所有计数器值必须设置为指定值。

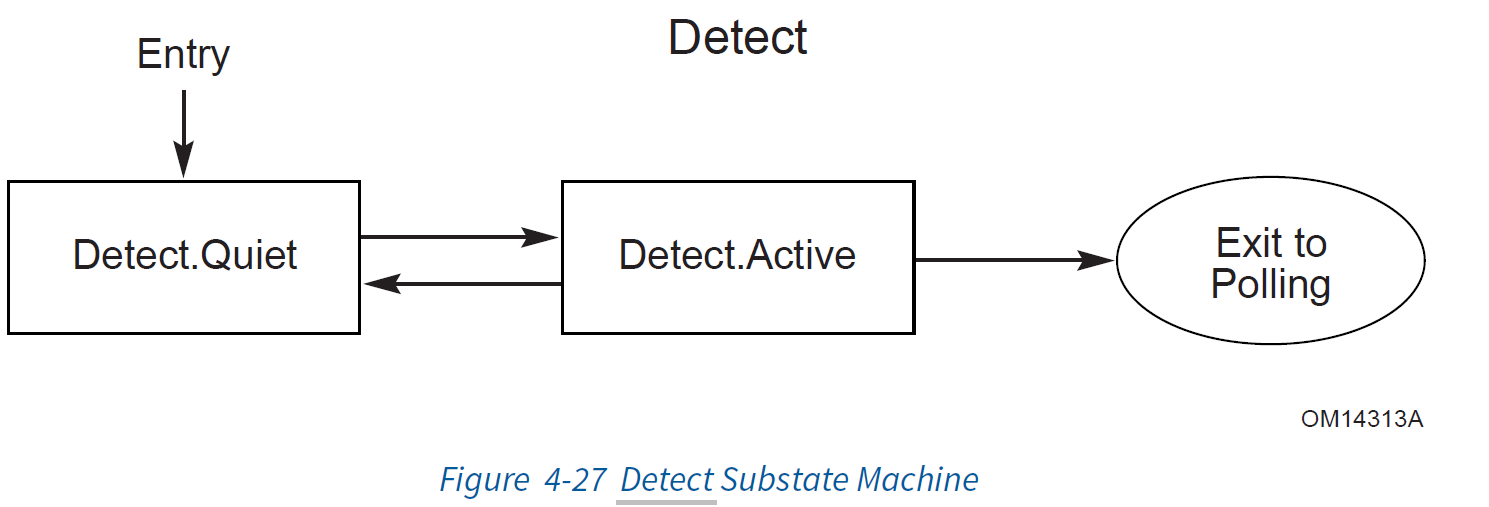

4.2.5.1 Detect Overview

该状态的功能是检测远端设备是否存在。可以从任何状态直接定向到该状态。

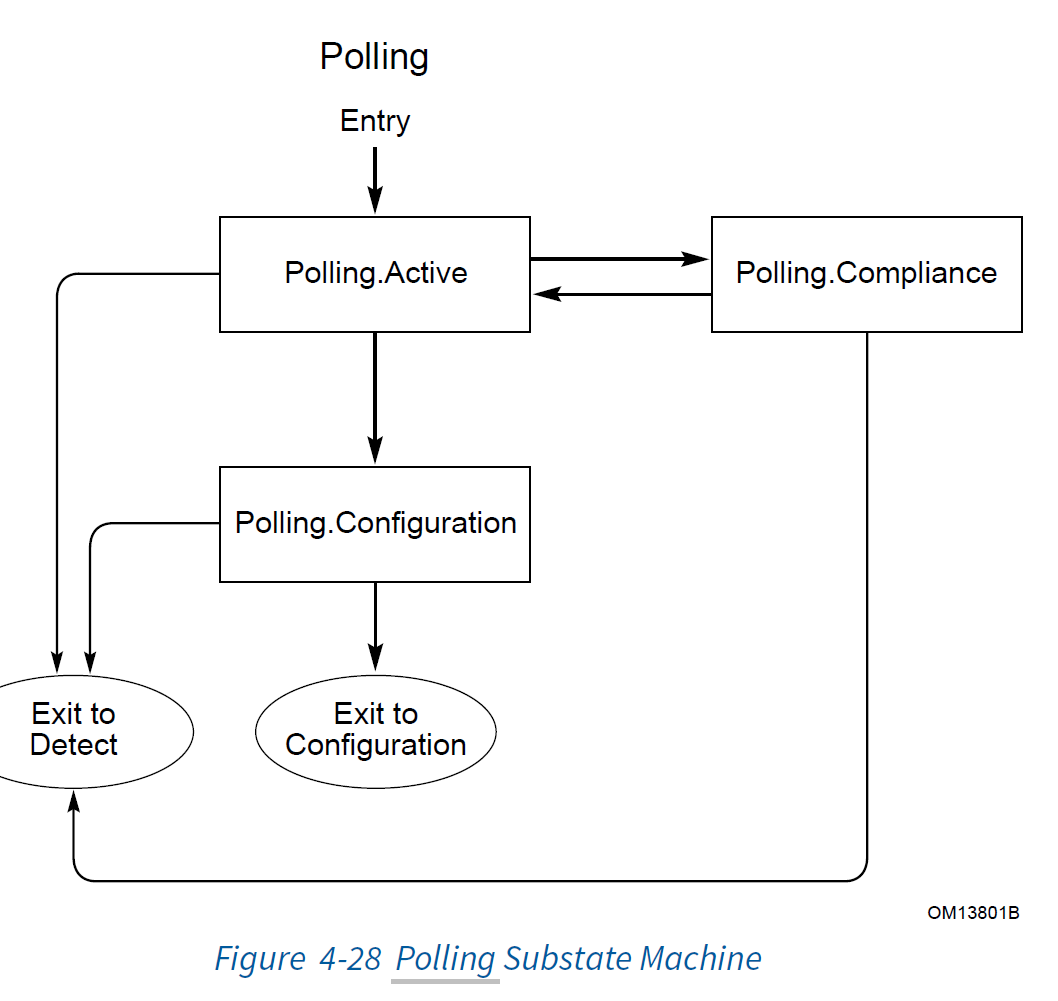

4.2.5.2 Polling Overview

LTSSM在Polling 状态发送训练有序集并响应接收到的训练有序集。在这个状态下,完成比特锁定和符号锁定,并配置通道极性。

Polling 状态包括 Polling.Compliance(请参阅 Section 4.2.6.2.2)。此状态旨在与测试设备一起使用,用于评估被测设备中的发送器和互连是否符合Table 8-6、Table 8-7和Table 8-10中的电压和时序规范。

Polling.Compliance 状态还包括一个简化的互操作性测试方案,该方案旨在使用各种各样的测试和测量设备(即码型发生器,示波器,BERT等)来执行测试过程。在Polling.Active状态发送Compliance Receive 字段被置为1的TS1序列(注意,Loopback字段不能置为1)可以使状态机转移到Polling.Compliance 状态。设置Compliance Receive的方法是特定于实现的。还包括将数据速率更改为由最高的公共发送和接收数据速率标识符(TS1的符号4)指示的速率的措施,以使此行为可扩展到各种数据速率。

IMPLEMENTATION NOTE

Use of Polling.Compliance

Polling.Compliance是针对一致性测试环境而设计的,在正常操作期间不会进入,并且不能由任何原因禁用。由特定的物理系统环境,或配置寄存器可以导致进入Polling.Compliance状态,如Section 4.2.6.2.1所述。导致发送器输出一致性码型的任何其他机制都是特定于实现的,并且超出了本规范的范围。

4.2.5.3 Configuration Overview

在Configuration状态,发送器和接收器均以协商的数据速率发送和接收数据。通过Lane 宽度协商形成链路。同时,还要执行Lane-to-Lane de-skew过程,如果允许的话加扰过程被禁用,N_FTS被设置,也可能进入Disable 或Loopback状态。

4.2.5.4 Recovery Overview

在Recovery状态,发送器和接收器都使用已配置的链路和通道号以及支持的数据速率发送和接收数据。Recovery允许已配置的链路根据需要调整数据速率,重新建立bit lock、Symbol lock或 Block alignment、Lane-to-Lane de-skew。Recovery还用于设置新的N_FTS值,并进入Loopback、Disabled、Hot Reset和Configuration 状态。

4.2.5.5 LO Overview

LO状态是正常的数据传输状态。所有的低功耗状态都需要从这个状态开始。

4.2.5.6 LOs Overview

LOs是一个省电状态。当使用具有独立扩频时钟(SSC)的独立参考时钟工作时(请参见Section 4.2.7),不支持LOs,并且不得在Capability寄存器中通告支持LOs。有关SSC的定义,请参见Section 4.3.7.3。

LO允许链路快速进入省电状态并从省电状态中恢复,而无需经过Recovery状态。

当收到一个EIOS后链路进入LOs。

从LOs退出然后进入到LO需要重新建立bit lock、Symbol lock或Block alignment、Lane-toLane de-skew。

一个端口发送器和接收器的链路不必都进入LOs。

4.2.5.7 L1 Overview

L1是一个省电状态。

L1状态比LO节省了更多的功耗,但增加了恢复延迟。

L1的进入是在数据链路层参与下完成的,在接收到EIOS之后发生。

4.2.5.8 L2 Overview

L2可以更节省功耗。在这个状态,发送器和接收器的电源几乎全部关掉,主电源和时钟是不能保证的,但是辅助电源还在正常工作。

当系统支持Beacon时,支持唤醒功能的上游端口必须能够发送Beacon;下游端口必须能够接收Beacon;这就是称为Beacon 的唤醒信号。

进入L2需要数据链路层的参与,在接收到EIOS之后发生。

4.2.5.9 Disabled Overview

Disabled 状态的功能是:允许禁用已配置的链路直到定向或电气空闲(例如,由热插拔导致)退出。

链路中发送的TS1和TS2有序集中Training Control字段的bit 1(Disable Link)会导致进入Disabled状态。

在上层逻辑的参与下,链路可以进入Disabled状态。链路也可以通过接收两个连续的TS1有序集并将其Disable Link置位来进入Disabled 状态(请参阅 Section 4.2.6.3.1和 Section 4.2.6.4.5)。

4.2.5.10 Loopback Overview

Loopback状态的目的旨在用于测试和故障隔离。规范仅定义了进入和退出行为,所有其他详细信息是特定于实现的。Loopback 可以基于每个通道或已配置的链路进行操作。

发起Loopback请求的叫做Loopback Master。

环回数据的叫做Loopback Slave。

设置TS1和TS2的Loopback字段会导致进入Loopback状态。

Loopback Master 怎么实现进入Loopback状态是基于特定实现的。

Loopback Slave 收到两个loopback字段设置为1的TS1或TS2就进入Loopback状态。

IMPLEMENTATION NOTE

Use of Loopback

一旦处于Loopback状态,只要遵循编码规则,Master就可以发送任意码型的符号。一旦进入Loopback状态,数据加扰的概念就不再相关了。发出的内容将回环回来。数据链路层用来通知物理层进入环回状态的机制和/或接口是组件实现特定的,不在本规范的范围之内。

4.2.5.11 Hot Reset Overvview

设置TS1和TS2的Hot Reset字段会导致进入Hot Reset状态。

链路进入Hot Reset的方式由上层逻辑决定。链路只要收到两个Hot Reset字段设置为1的TS1或TS2序列就会进入Hot Reset状态。

4.2.6 Link Training and Status State Rules

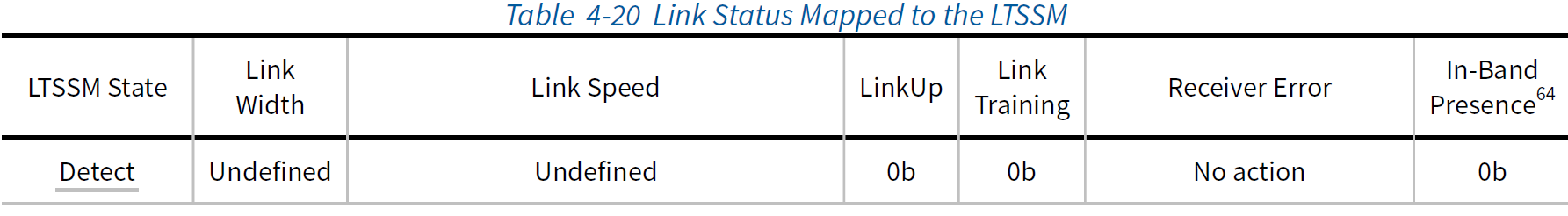

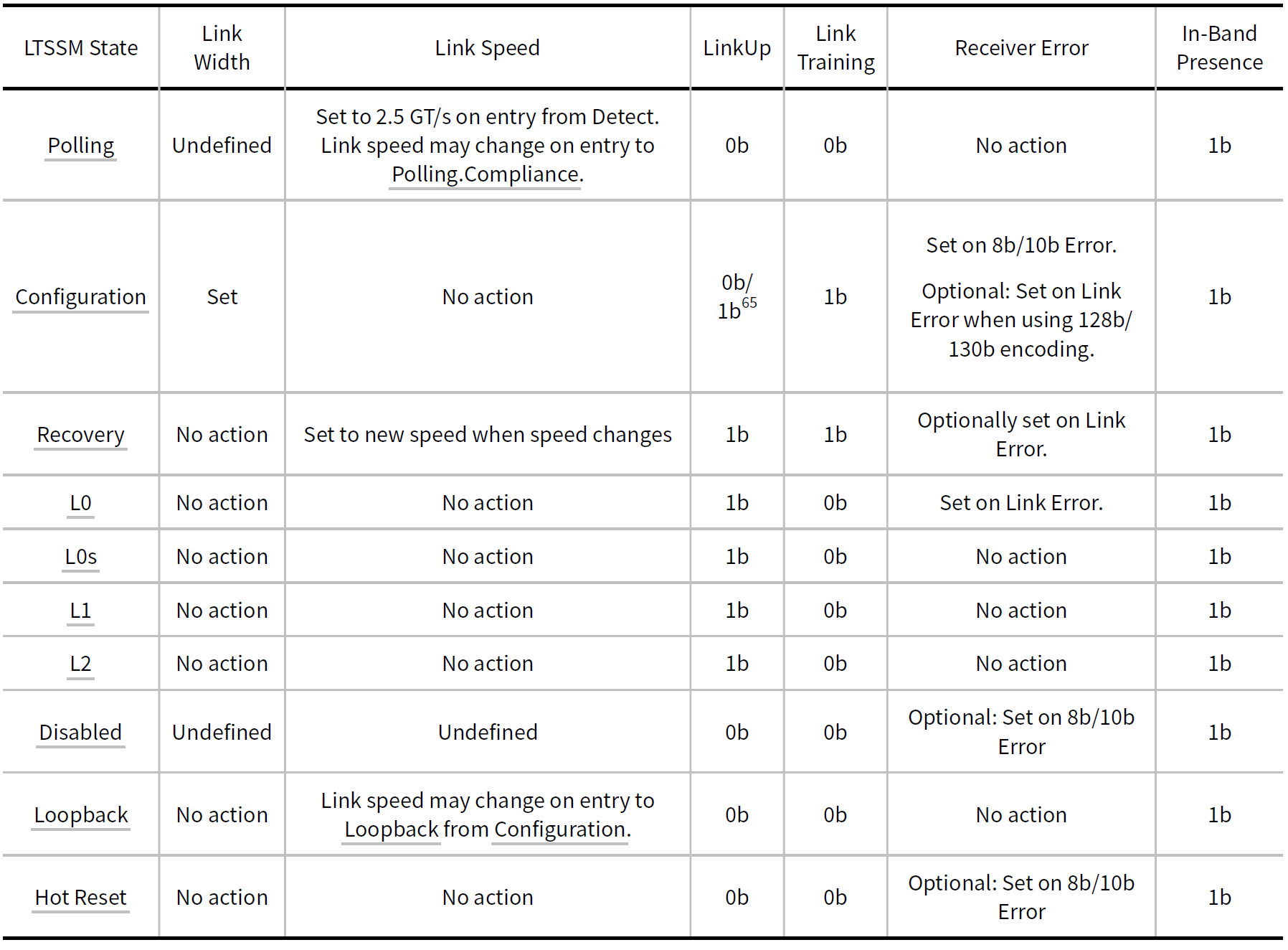

Table 4-20说明了如何在整个LTSSM中处理链路状态信息(有关更多信息,请参见Section 3.2中的LinkUp;Section 7.5.3.8中的Link Speed、Link Width、和LinkTraining;Section 6.2 中的 Receiver Error;以及 Section 6.7中的 In-Band Presence)。当以8b/10b 编码运行时,在Table 4-20中允许接收器将错误报告为Receiver Error时,接收器还可以选择在Lane Error Status 寄存器中报告8b/10b错误。

IMPLEMENTATION NOTE

Receiver Errors During Configuration and Recovery States

在Configuration 状态或Recovery 状态中设置 Receiver Errors的功能旨在允许报告在这两个状态中数据交换时发生的链路错误。例如,如果在接收TLP时LTSSM从LO切换到Recovery状态,则可以报告LTSSM切换之后发生的链路错误。

注意:

-

In-Band是指:没有边带信号用于计算链路另一端上电设备的存在。

-

LinkUp:如果通过Detect->Polling->Configuration,则LinkUp始终为0,一直到链路初始化完成才为1;如果从任何其他状态进入Configuration状态,则LinkUp始终为1。

LTSSM状态机转移图如Figure 4-26所示。

Figure 4-26 Main State Diagram for Link Training and Status State Machine

4.2.6.1 Detect

检测状态的目的是检测远端设备是否存在。Detect子状态的状态机如Figure 4-27所示。

以下各节介绍LTSSM各个子状态的规则。

4.2.6.1.1 Detect.Quiet

- Detect.Quiet 子状态下,发送器应该处于电气空闲状态。

- 此时DC共模电压不需要满足规范定义的0~3.6V的要求。

- 这个状态只支持2.5GT/s下的工作频率。如果从别的LTSSM状态跳入这个状态之前的工作频率不是数据速率为2.5GT/s下的工作频率,则LTSSM需要至少停在此状态1ms,等工作频率切换为2.5GT/s下的频率。

- Note:这不影响在TS1和TS2中通告的data rate。

- 所有接收器都必须在进入此子状态后的1ms内满足2.5 GT/s下的ZGT-pc规范的要求(请参见Table 8-10)。LTSSM必须保持在此子状态,直到满足2.5GT/s下的ZRx-Dc规范为止。

- 此状态下LinkUp=0b。这意味着不管从哪个状态跳转到该状态,都要Link Down。

- 此状态下Link Status 2 寄存器的 Equalization 8.0 GT/s Phase 1 Successful、Equalization 8.0 GT/s Phase 2 Successful、Equalization 8.0GT/s Phase 3 Successful 和 Equalization 8.0 GT/s Complete 字段都为0。16.0GT/s Status寄存器的 Equalization 16.0 GT/s Phase 1 Successful、Equalization 16.0 GT/s Phase 2 Successful、Equalization16.0 GT/s Phase 3 Successful 和 Equalization 16.0 GT/s Complete 字段都为0。32.0 GT/s Status 寄存器的 Equalization 32.0 GT/s Phase 1 Successful, Equalization 32.0 GT/s Phase 2Successful、Equalization 32.0 GT/s Phase 3 Successful 和 Equalization 32.0 GT/s Complete字段都为0。

- use_modified_TS1_TS2_Ordered_Set变量复位为0

- 变量 directed_speed_change 清0;变量 upconfigure_capable清0;变量idle_to_rlock_transitioned清00h;变量select_deemphasis的值:对上游端口来说跟具体平台有关,对下游端口来说与Link Status 2寄存器的 Selectable Preset/De-emphasis 字段一致;变量equalization_done_8GT_data_rate、equalization_done_16GT_data_rate、equalization_done_32GT_data_rate清0。变量perform_equalization_for_loopback清0。

- 请注意,由于这些变量是PCle 2.0规范定义的,因此PCe 2.0之前的设备将不会实现这些变量,并且将始终采用以下处理方式,即让directed_speed_change和 upconfigure_capable 变量始终为0b,且idle_to_rlock_transitioned 变量始终设置为FFh。

- 异常情况下(比如设备未连接),LTSSM需要在此状态停留12ms,然后跳转到Detect.Active状态;正常情况下(比如设备连接上),当任意Lane检测到电气空闲退出就跳转到Detect.Active状态。

4.2.6.1.2 Detect.Active

- 在Detect.Active状态,发送器在所有未配置的Lane上执行 Receiver Detection过程,用于检测对端是否连接了一个设备(关于Receiver Detection 电路原理的信息,参阅Section 8.4.5.7)。

- 如果在所有已配置的Lane上检测到Receiver存在则LTSSM状态机跳转到Polling状态。

- 如果有任一个Lane上没有检测到Receiver则 LTSSM状态机跳转回 Detect.Quiet状态。

- 如果有的Lane检测到Receiver 而有的Lane没有检测到,则需要:

- 1.等12ms。

- 2.发送器需要重新在所有未配置的Lane上检测 Receiver,

- 如果这次检测的结果与第一次检测的结果相同,状态机就切换到Polling状态。

- 那些未检测到Receiver的Lane 必须:

- 1.如果逻辑中实现了多个LTSSM状态机,则这些未检测到Receiver的Lane也可以交由别的LTSSM来检测,这是一种实现方法。

- 2.所有没有与可选的新的LTSSM关联上的Lane进入电气空闲状态。(注:不需要驱动共模电压来满足LO期间的DC直流共模和电气空闲(VTx-CM-DC-ACTIVE-IDLE-DELTA)规范之间的绝对增量规范(请参见 Table 8-6)。

- (1)在LTSSM转换回Detect之后,必须立即将这些Lane与此LTSSM重新关联。

- (2)切换到电气空闲之前,无需发送 EIOS。

- 那些未检测到Receiver的Lane 必须:

- 如果这次检测的结果与第一次检测的结果相同,状态机就切换到Polling状态。

否则状态机跳入Detect.Quiet状态。

4.2.6.2 Polling

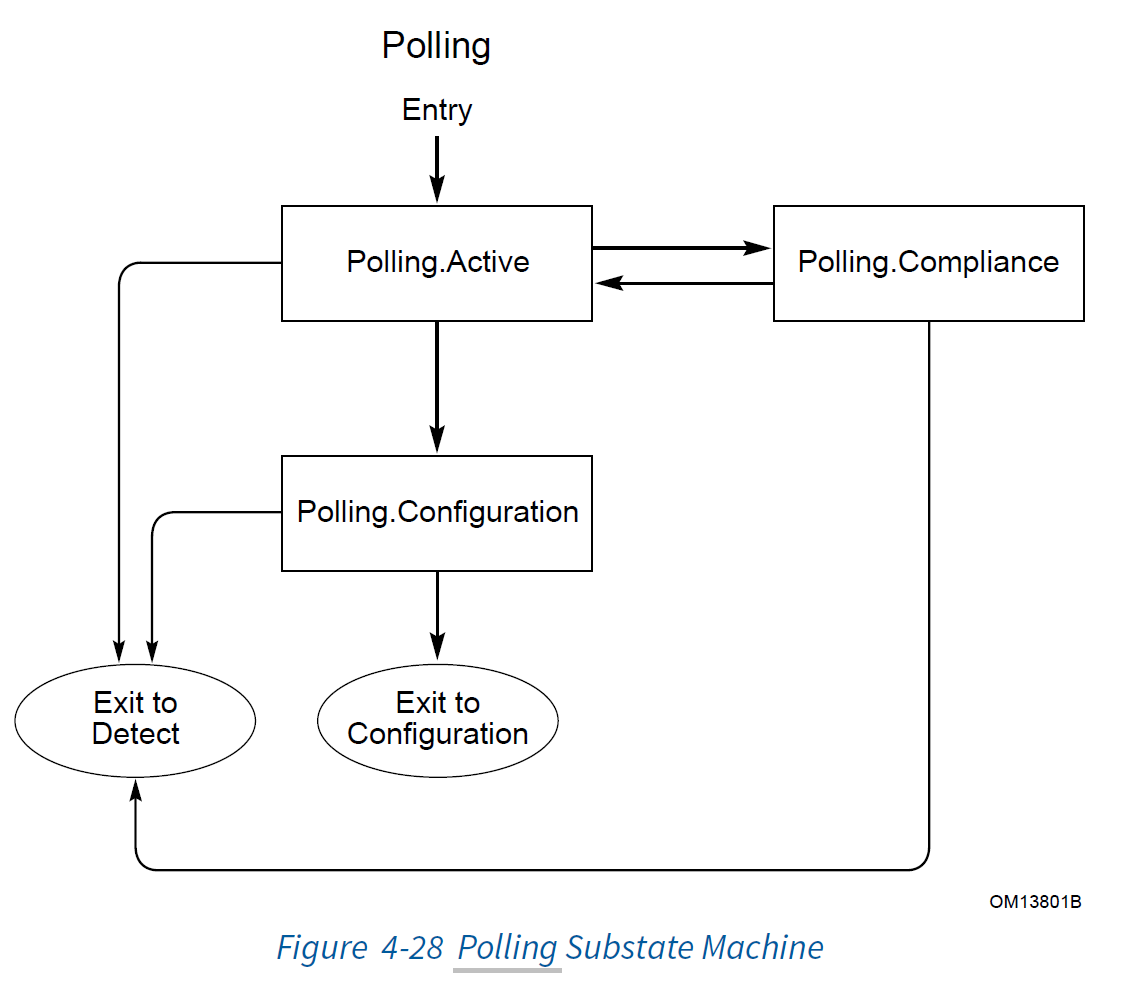

Polling 状态的子状态机如Figure 4-28所示。

LTSSM在Polling 状态两侧设备交换TS1和TS2训练序列,用于完成比特锁定、符号锁定和配置通道极性。同时,还在TS1和TS2训练序列中携带了两端设备能支持的data rate。

4.2.6.2.1 Polling.Active

Detect状态完成之后(即设备检测完成),LTSSM状态机就跳转到该状态。

-

在Polling.Active状态下,发送器在所有Detect期间检测到Receiver的Lane 上发送Lane number和Link number 设置为PAD 的TS1 Ordered Set。

- 发送的TS1的Data Rate Identifier 字段需要携带本设备能支持的data rate。

- 发送器在退出电气空闲和发送TS1序列之前设置好其TX的共模电压。

- 发送器需要在进入此状态的192ns之内以满足Transmit Margin(Link Control 2)字段定义的默认电压电平驱动数据。这个发送电压电平要一直持续到进入Polling.Compliance 状态或 Recovery.RcvrLock状态。

-

此状态下,如果把Link Control 2寄存器的Enter Compliance字段设置为1,则状态机跳转到Polling.Compliance状态;如果在Polling.Active之前就把Link Control 2寄存器的Enter Compliance

字段设置为1,则发送器不发送TS1序列,直接进入Polling.Compliance状态(这应该也符合测试的一般流程)。 -

如果至少发送了1024个TS1并且所有检测到有Receiver存在的Lane都收到满足以下条件的8个连续的训练序列(TS1、TS2或其补码),则LTSSM状态机就跳转到Polling.Configuration状态。

-

TS1序列,其Lane number和Link number字段设置为PAD,且Compliance Receive 字段为0b。

-

TS1序列,其Lane number和Link number字段设置为PAD,且Loopback字段为0b。

-

TS2序列,其Lane number和Link number字段设置为PAD。

-

-

否则,在24ms超时后LTSSM状态机会按下述方式跳转。

- 如果下面两个条件都满足就跳转到Polling.Configuration 状态:

任意在Detect期间检测到有Receiver存在的Lane 上至少发送了1024个TS1并且收到满足以下条件的8个连续的训练序列。

-

TS1序列,其Lane number和Link number字段设置为PAD,且Compliance Receive 字段为0b。

-

TS1序列,其Lane number和Link number字段设置为PAD,且Loopback字段为0b。

-

TS2序列,其Lane number和Link number字段设置为PAD。

从进入Polling.Active状态起,至少在一组predetermined set of Lanes 上至少都检测到一次从电气空闲状态退出。

Note:设置这个条件的目的是让发送器和接收器不会因为一个或多个坏的Lane而导致状态机无法正常运行。这使得状态机可以继续在Polling.Configuration中进行其他训练。这个功能是特定于实现的。请注意,直到1.1规范之前,predetermined set of Lanes的数目还是等于检测到Receiver的通道的总数。

Note:从进入Polling.Active状态起,收到八个连续的TS1或TS2有序集的任何Lane都应至少检测到一次从电气空闲退出。

如果满足下面两个条件任意一个就跳转到Polling.Compliance状态:

从进入Polling.Active状态起,之前定义好的predetermined set of Lanes 中不是所有Lane都检测到电气空闲退出,就会跳转到Polling.Compliance状态。

这些Lane中任意一条Lane上收到了8个连续的Lane number和Link number字段设置为PAD,Compliance Receive 字段为1b,且Loopback字段设置为0b的TS1序列,就跳转到Polling.Compliance状态。

Note:如果在所有Lane上都连接一个被动测试负载,则设备将进入Polling.Compliance。

- 如果Polling.Configuration和 Polling.Compliance的条件都没满足就跳转到Detect状态。

这里有个术语predetermined set of Lanes(预定通道组):它有这样的背景,比如说x8链路上有5条Lane是好的,但是我们却不能用这5条Lane来工作,只能使用的模式为x4、x2和x1,所以需要提前配置好要使用哪些Lane,丢弃哪些Lane,predetermined set of Lanes的目的就在此。

Synopsys PCle IP示例Polling.Active状态交换的TS1序列为:

RX侧:TS1(BC->F7->F7->FF->0E(rate)->00->4a->4a->4a->4a->4a->4a->4a->4a->4a->4a)

TX侧:TS1(BC->F7->F7->80->0E(rate)->00->4a->4a->4a->4a->4a->4a->4a->4a->4a->4a)

4.2.6.2.2 Polling.Compliance

-

Link Control 2 寄存器的Transmit Margin字段为1就会进入此状态,并且在192ns内作用到发送侧封装的PIN上。这个字段需要在LTSSM状态机处于此状态的整个过程中都有效。

-

使用以下算法在从Polling.Active到Polling.Compliance的转换中确定用于传输的一致性码型的数据速率和去加重级别。

- 如果端口仅能够以2.5 GT/s的数据速率进行传输,则用于传输的一致性码型的数据速率为2.5GT/s,去加重级别为-3.5dB。-

否则,如果端口由于在Polling.Active 中检测到八个连续的Compliance Receive 字段为1的TS1有序集而进入Polling.Compliance 状态,则数据速率为交换的TS1序列集中携带的Data Rate Identifiers字段支持的公共数据速率中最高的速率。select_deemphasis 变量必须TS1有序集中的Selectable De-emphasis字段的值。如果公共数据速率为8.0 GT/s 或更高,则将每个通道上的select_preset变量设置为TS1有序集的Symbol6中通告的发送器的preset值,并且该值必须由发送器使用(使用接收器的TS1中通告的preset值是可选实现的)。如果公共数据速率为8.0GT/s或更高,则任何未接收到带有发送器preset值的TS1有序集的通道可以选择使用任何受支持的发送器preset值。

-

Link Control 2 寄存器的Transmit Margin字段为1,则使用Link Control 2的 Target Link Speed 字段支持的值作为一致性码型的数据速率。如果数据速率为5GT/s,则select_deemphasis变量等于Link Control 2的Compliance Preset/De-emphasis 字段的值等于0001b。如果数据速率为8GT/s或更高,则select_deemphasis变量等于Link Control 2的Compliance Preset/De-emphasis字段的值,这也是此时发送器的工作状态。

-

-

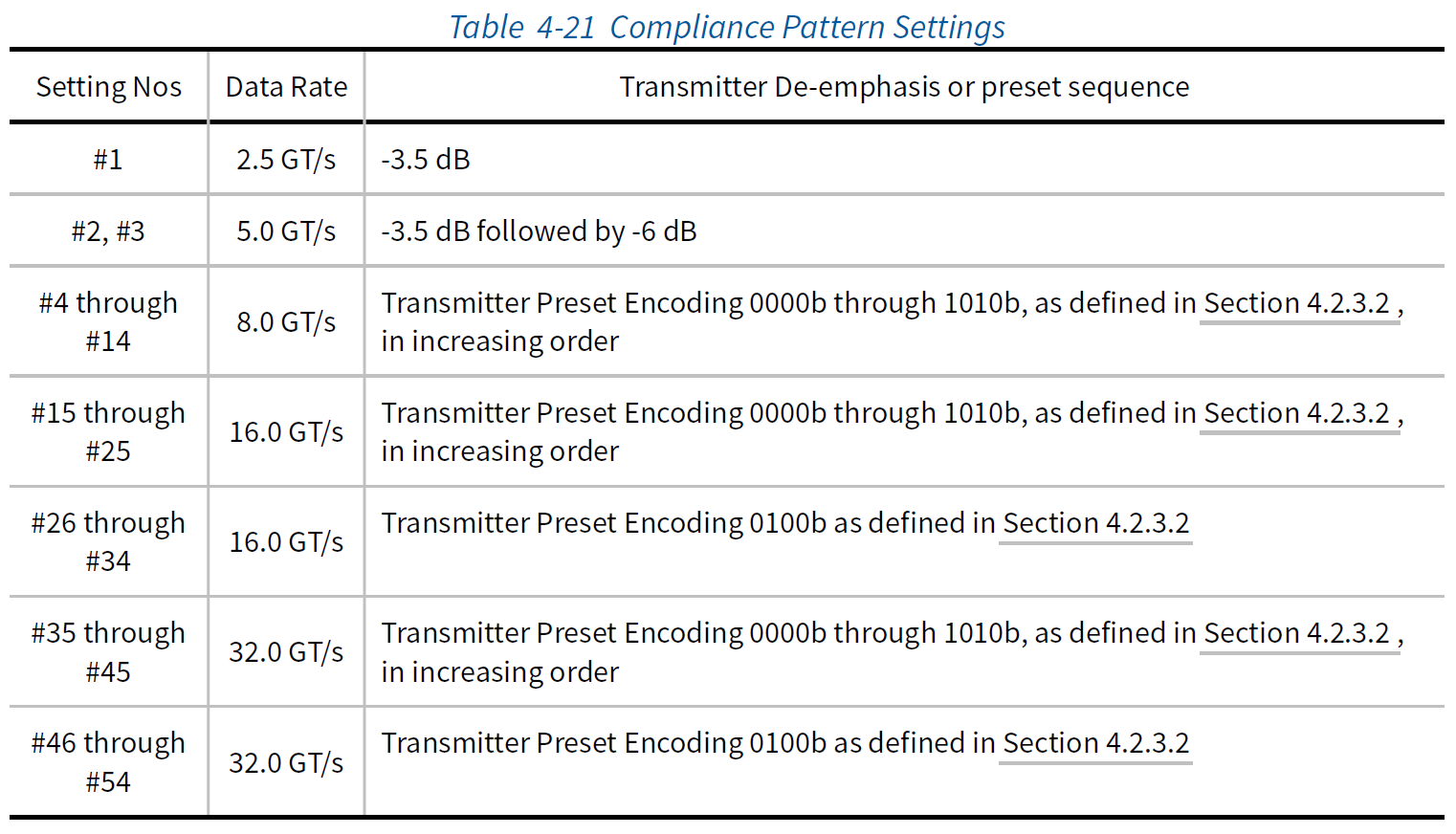

其他情况(应该指的就是接测试负载的场景吧),data rate、preset和de-emphasis级别的定义如下,它取决于组件支持的最大数据速率和在此条件下进入Polling.Compliance的次数,如Table 4-21描述:

Table 4-21 Compliance Pattern Settings

随后按上述顺序重复进入Polling.Compliance状态。例如,导致端口以5.0GT/s的数据速率和-6dB的去加重级别传输一致性码型的过程为:Polling.Active,Polling.Compliance (2.5 GT/s 和-3.5 dB), Polling.Active, Polling.Compliance (5.0 GT/s 和-3.5dB),Polling.Active, Polling.Compliance (5.0 GT/s和-6 dB)。即逐个试上面的Setting,找到一个合适的设置,一致性测试负载也是按照这个思路执行测试的。

如果端口支持16.0 GT/s或更高的数据速率,或当端口以8.0GT/s或更高的数据速率(请参见Table 8-10)工作时其接收器不满足2.5 GT/s的ZRx-pc规范,则必须在Polling.Configuration 状态下将该序列设置为Setting#1。允许所有端口在

Polling.Configuration 状态下将序列设置为Setting#1。

IMPLEMENTATION NOTE

Compliance Load Board Usage to Generate Compliance Patterns

可以设想,一致性负载(基)板可以在差分对的一个支路上以350mv峰峰值发送约1ms的100mhz信号,以使设备达到到期望的速度和去加重水平。被测设备需要根据其支持的最大数据速率,依次在以下设置中循环,以便每次从Polling.Active进入Polling.Compliance。从第一个进入Polling.Compliance的条目的第一个设置开始如Table 4-21中定义的基本复位所示。

-

如果一致性码型的数据速率不是2.5GT/s,并且在进入Polling.Compliance之前在Polling.Active中发送了TS1有序集,则发送器在进入电气空闲之前会发送一个EIOS或两个连续的EIOS。如果一致性码型的数据速率不是2.5GT/s,并且在进入Polling.Compliance 之前未在Polling.Active中发送TS1有序集,则发送器必须进入电气空闲状态,而不发送任何EIOS。在电气空闲期间,数据速率将更改为新的速率并保持稳定。在操作频率为5.0GT/s的情况下,则如果select_deemphasis变量为1b,则de-emphasis/preset级别必须设置为-3.5dB,否则必须将其设置为-6dB。如果操作频率为8.0GT/s,则必须将发送器的preset值设置为select_preset变量中的值。电气空闲周期大于1ms,但不超过2ms。

-

data rate和de-emphasis/preset级别确定之后,在Polling Compliance期间的行为要符合以下规则:

- 如果由于发送TS1序列或设置Link Control 2的 Enter Compliance 和 Enter Modified Compliance 字段导致状态机进入Polling.Compliance状态,则发送器就要以上述定义好的速率在所有检测到有Receiver存在的Lane上发送 error status Symbol设置为0的Modified Compliance Pattern (Section 4.2.9)。

- 如果数据速率是2.5 GT/s或5.0 GT/s,则特定的通道接收器通过查找任何出现的Modified Compliance Pattern,然后将其自己的Modified Compliance Pattern的error status Symbol的Pattern Lock(第1位)置为1来表示成功锁定输入的Modified Compliance Pattern。

- error status Symbols 不可在锁定过程中使用,因为它们在任何给定时刻均未定义。

- 将上面出现的Modified Compliance Pattern定义为以下8b/10b符号序列:K28.5,D21.5,K28.5和D10.2或每个单独符号的补码。

- 被测设备必须在其接收器封装引脚上收到Modified Compliance Pattern后1ms内成功锁定到输入的Modified Compliance Pattern,必须将其在发送器封装引脚上发送的Modified Compliance Pattern的 Pattern Lock 设置为1。

- 如果数据速率为8.0GT/s或更高:在进入此子状态时,Error_Status字段设置为00h。如Section4.2.2.2.1所述,每个通道在实现块对齐时都独立设置Pattern Lock字段。Pattern Lock之后,将数据块中接收到的符号与空闲数据符号(00h)进行比较,并且每个不匹配的符号都会使Receiver Error Count字段增加1。Receiver Error Count的饱和值为127(其他不匹配的符号不会更改 Receiver Error Count)。每个通道的Pattern Lock和 Receiver Error Count 信息作为在该通道的Modified Compliance Pattern 中传输的SKP有序集的一部分进行传输。有关更多信息,请参见Section 4.2.7。被测设备必须在其接收器封装引脚上收到Modified Compliance Pattern后的4ms内,将其发送的SKP有序集中的Pattern Lock设置为1。

- 如果数据速率是2.5 GT/s或5.0 GT/s,则特定的通道接收器通过查找任何出现的Modified Compliance Pattern,然后将其自己的Modified Compliance Pattern的error status Symbol的Pattern Lock(第1位)置为1来表示成功锁定输入的Modified Compliance Pattern。

- 如果由于发送TS1序列或设置Link Control 2的 Enter Compliance 和 Enter Modified Compliance 字段导致状态机进入Polling.Compliance状态,则发送器就要以上述定义好的速率在所有检测到有Receiver存在的Lane上发送 error status Symbol设置为0的Modified Compliance Pattern (Section 4.2.9)。

-

在Section 4.2.2.4中定义的加扰可以用于收到的 Modified Compliance Pattern。例如,为每个通道设置加扰的LFSR种子,在EIEOS初始化 LFSR,而SKP有序集不推进LFSR。

-

如果数据速率是2.5 GT/s或5.0GT/s,则一一旦特定通道指示它已锁定到输入的Modified Compliance Pattern,则每次发生接收器错误时,该通道的Receiver Error Count都会增加。

-

error status Symbols使用低7位作为Receiver Error Count字段,如果计数达到127,则该字段将始终停留在全1。

-

如果使用8b/10b编码,则接收器不得对处于此子状态时将接收的10位模式做出任何措施。

-

-

如果 Link Control 2 寄存器中的Enter Compliance为0b,则下一个状态定向到Detect。

-

否则,如果在进入Polling.Compliance 时将 EnterCompliance设置为1b,则在满足以下任何条件的情况下,下一个状态为Polling.Active:

-

Link Control 2 寄存器中的 Enter Compliance位更改为0b。

-

该端口是上游端口,并且在任何通道上都接收到EIOS。当此条件为真时,Enter Compliance位将重置为0b。

-

如果发送器以2.5 GT/s以外的数据速率发送数据,或者在进入Polling.Compliance时将Link Control 2寄存器中的Enter Compliance 位设置为1b,则发送器将发送八个连续的EIOS并在进入进入电空闲状态之前先转换到Polling.Active。在电气空闲期间,数据速率更改为2.5GT/s并稳定下来,去加重级别设置为-3.5dB。电气空闲周期大于1ms,但不得超过2ms。

Note:发送多个EIOS可以提供足够的鲁棒性,以便在使用配置寄存器机制进入时,另一个端口检测到至少一个EIOS并退出Polling.Compliance 子状态。

否则,如果由于Link Control 2寄存器的 Enter Compliance设置为1b并且Link Control 2寄存器的Enter Modified Compliance 设置为0b,从而导致端口进入了Polling.Compliance,则:

a.发送器以上面定义的data rate和de-emphasis/preset等级在所有检测到有Receiver存在的Lane上发送一致性码型。

b.如果下面任意条件满足,则状态机跳转到Polling.Active:

1.在进入Polling.Compliance 之前 Link Control 2的Enter Compliance字段从1b变为0b。

2.该端口是一个上游端口,Link Control 2的Enter Compliance字段为1b,并且已在任何通道上检测到EIOS。当此条件为真时,Enter Compliance位重置为0b。

发送器发送八个连续的EIOS,并在切换到Polling.Active之前进入电空闲状态。在电气空闲期间,数据速率更改为2.5GT/s并保持稳定。电气空闲时间段大于1ms,但不得超过2ms。

注意:发送多个EIOS可以提供足够的鲁棒性,以便在使用配置寄存器机制进入时,另一个端口检测到至少一个EIOS 并退出Polling。

否则,

a. 发送器在Detect期间以上面确定的数据速率和去加重/预设级别在检测到有接收器存在的通道上发送以下码型:

-

For Settings #1 to #25, and #35 to #45: Compliance pattern on all Lanes.

-

For Setting #26, #46:Jitter Measurement Pattern on all Lanes.

-

For Setting #27,#47: Jitter Measurement Pattern on Lanes 0/8/16/24 and Compliance pattern on all other Lanes.

-

For Setting #28, #48: Jitter Measurement Pattern on Lanes 1/9/17/25 and Compliance pattern on all other Lanes.

-

For Setting #29, #49: Jitter Measurement Pattern on Lanes 2/10/18/26 and Compliance pattern on all other Lanes.

-

For Setting #30, #50: Jitter Measurement Pattern on Lanes 3/11/19/27 and Compliance patter on all other Lanes.

-

For Setting #31, #51: Jitter Measurement Pattern on Lanes 4/12/20/28 and Compliance pattern on all other Lanes.

-

For Setting #32, #52: Jitter Measurement Pattern on Lanes 5/13/21/29 and Compliance pattern on all other Lanes.

-

For Setting #33, #53: Jitter Measurement Pattern on Lanes 6/14/22/30 and Compliance pattern on all other Lanes.

-

For Setting #34, #54:Jitter Measurement Pattern on Lanes 7/15/23/31 and Compliance pattern on all other Lanes.

b.如果在Detect期间检测到有接收器存在的任何通道的接收器检测到电气空闲退出,则下一个状态为Polling.Active。如果发送器以2.5 GT/s以外的数据速率发送,则发送器将发送八个连续的EIOS,并进入电空闲状态,然后再转换为Polling.Active。在电气空闲期间,数据速率更改为2.5GT/s并保持稳定。电气空闲时间段大于1ms,但不得超过2ms。

4.2.6.2.3 Polling.Configuration

-

如果有需要,接收器在这个状态完成通道极性翻转(Section 4.2.4.5)。

-

进入该状态后,必须将Link Control 2寄存器的Transmit Margin字段置为000b。

-

如果有需要,按Section 4.2.6.2.2的描述更新发送器的Polling.Compliance过程的配置。

-

发送器会在所有检测到有Receiver存在的Lane 上发送 Link number和 Lane number为PAD的TS2序列集。

- 发送的TS2的Data Rate Identifier字段需要携带本设备能支持的data rate。

-

如果在任意检测到有Receiver存在的的Lane上收到8个Link number 和Lane number为PAD的TS2有序集,且在收到一个这样的TS2之后发送完16个TS2有序集,则状态机跳转到Configuration状态。

-

否则,在经过48ms超时后状态机跳转到Detect状态。

以下给出了Synopsys PCle IP在该状态下的代码,用于帮助理解。

从波形上看Polling.Configuration 状态交换的序列为:

RX侧:

TS1(BC−>F7−>F7−>FF−>0E(rate)−>00−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a)TS1(BC->F7->F7->FF->0E(rate)->00->4a->4a->4a->4a->4a->4a->4a->4a->4a->4a->4a->4a->4a->4a->4a)TS1(BC−>F7−>F7−>FF−>0E(rate)−>00−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a)

TS2(BC−>F7−>F7−>FF−>0E(rate)−>00−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45)TS2(BC->F7->F7->FF->0E(rate)->00->45->45->45->45->45->45->45->45->45->45->45->45->45->45)TS2(BC−>F7−>F7−>FF−>0E(rate)−>00−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45)

TX侧:

TS1(BC−>F7−>F7−>80−>0E(rate)−>00−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a)TS1(BC->F7->F7->80->0E(rate)->00->4a->4a->4a->4a->4a->4a->4a->4a->4a->4a->4a->4a->4a->4a)TS1(BC−>F7−>F7−>80−>0E(rate)−>00−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a−>4a)

TS2(BC−>F7−>F7−>80−>0E(rate)>00−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45)TS2(BC->F7->F7->80->0E(rate)>00->45->45->45->45->45->45->45->45->45->45->45->45->45->45->45)TS2(BC−>F7−>F7−>80−>0E(rate)>00−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45−>45)

4.2.6.2.4 Polling.Speed

如果设备仅在2.5GT/s下工作,则此状态永远不会达到;这个状态本来的目的是用于切换到Recovery状态改变 data rate。

IMPLEMENTATION NOTE

Support for Higher Data Rates than 2.5 GT/s

链路最初将以2.5GT/s的数据速率训练到LO状态,即使双方都能够以大于2.5GT/s的数据速率进行操作。支持的更高数据速率在TS有序集中通告。对方的速度能力是在Configuration.Complete 子状态期间注册的。基于最高支持的共用数据速率,任何一方都可以通过切换到Recovery状态来启动从LO状态开始的速度切换。

Synopsys在实现时已经没有这个状态了。

4.2.6.3 Configuration

Figure 4-29 Configuration Substate Machine

这个状态完成链路速率协商、链路宽度协商、通道编号以及lane-to-lane de-skew。RC(DSP)设备发起协商过程。

4.2.6.3.1 Configuration.Linkwidth.Start

4.2.6.3.1.1 Downstream Lanes

-

在Configuration.Linkwidth.Start子状态,DSP的上层逻辑可以通过在所有检测到Receiver的Lane 上发送Disable Link字段设置为1的TS1和TS2有序集让LTSSM状态机切换到Disabled状态。

-

在Configuration.Linkwidth.Start子状态,端口的上层逻辑可以通过在所有检测到Receiver的Lane上发送Loopback字段设置为1的TS1和TS2有序集让LTSSM状态机切换到Loopback状态,此时发送器作为Loopback Master。

-

如果支持crosslink,在所有传输TS1有序集的通道接收到两个连续的TS1有序集且其Disable Link字段被声明为1,则下一个状态为Disabled状态。

-

如果下述其中一个条件满足,则下个状态为Loopback状态:

- 发送TS1有序集的所有Lane也在接收TS1有序集,收到的两个连续的TS1有序集的Loopback字段被置 1b。

- 任意发送TS1有序集的Lane收到了两个连续的Loopback字段置1b的TS1有序集且Enhanced Link Behavior Control 字段被设置为1b。

- 请注意,接收到Loopback字段置1的有序集的设备将成为Loopback Slave。

-

如果LinkUp为0b或LTSSM未启动链路宽度的配置,则发送器在所有有效的Downstream Lanes上发送Link number设置为某值且Lane number设置为PAD的TS1有序集。此外,如果upconfigure_capable为1b且LTSSM未启动链路宽度的配置,则LTSSM在进入Recovery检测到电气空闲退出且连续收到两个Link number设置为某值且Lane number 设置为PAD的TS1有序集之后,在所有无效的Lanes上发送Link number设置为某值且Lane number设置为PAD的TS1有序集。

-

从Polling转换到此子状态时,在Detect站柜台检测到接收器的任何通道均被视为有效通道。

-

从Recovery转换到此子状态时,在之前的Configuration.Complete 完成配置的通道被视为有效通道。

-

TS1有序集的Data Rate Identifier 字段必须通告端口支持的所有数据速率,包括它不打算使用的数据速率。

-

-

如果LinkUp为1b且LTSSM启动了链路宽度的配置,则一开始它会在当前有效的一组Lane上发送Link number和Lane number都设置为PAD的TS1有序集;然后无效的Lane会变成有效的Lane;然后这些Lane会在进入Recovery检测到电气空闲退出且连续收到两个Link number设置为某值且Lane number 设置为PAD的TS1有序集。LTSSM会在发送了TS1序列集又收到两个Link number和Lane number都设置为PAD的TS1有序集或1ms超时的Lanes上发送Link number设置为某值且Lane number 设置为PAD的TS1有序集。

-

在任何无效的通道变为有效后,发送器必须等待其TX共模电压建立完成,然后才能退出电空闲并发送TS1有序集。

-

对于仅能够作为唯一链路的通道组,Link number是可以不同的。

-

Note:Link number 分配的一个示例是有八个Downstream Lane的链路,当连接到一个组件时,这些通道可以协商成一个x8端口,而当连接到两个不同组件时,则可以协商成两个x4端口。Downstream Lane在其中四个Lane上发送Link number为N的TS1有序集,而在其他四个Lane上发送Link number为N+1的TS1有序集。

-

-

如果有任何Lane首先收到至少一个或多个Link number 和Lane number都设置为PAD的TS1有序集,则如果接下来在这些Downstream Lanes 上又收到了两个连续的Link number设置为某值且 Lane number 设置为PAD的TS1有序集,且此Link number与其之前发送的一致,则状态机立马切换到Configuration.Linkwidth.Accept状态。

- 如果不支持交叉链路,则首先Link number和Lane number都设置为PAD的TS1有序集的条件始终为true。

-

否则:如果LinkUp为0b并且支持交叉链路,则所有检测到Receiver的Downstream Lane 先发送16-32个Link number为non-PAD且Lane number为PAD的TS1序列集;然后,如果上述任一个Downstream Lane收到了两个连续的Link number不是PAD且Lane number为PAD的TS1序列集,就把Downstream Lane 指定为Upstream Lane 并且指定一个随机的交叉链路超时时间(参看Table8-7的Tcrosslink)。同样,状态机也跳转为Upstream Lane的Configuration.Linkwidth.Start。

-

Note:支持交叉链接(crosslink)指的是双方都可以尝试充当Downstream Port。这个解决方案是使两个Port都作为Upstream Port,然后设置一个随机超时时间,直到链路的一侧变为Downstream Port,而另一侧仍为Upstream Port。即使连接两个相同的设备,此超时也必须是随机的,以最终打破任何可能的死锁。

-

如果支持交叉链路,则只有在未因接收TS2有序集而中断的情况下,接收序列为TS1的有序集(其Link number为PAD,后跟与发送的Link number 相匹配的非PAD的Link number)才有效。

-

IMPLEMENTATION NOTE

Crosslink Initialization

如果下游通道同时连接到下游通道(交叉链路)和上游通道,则具有下游通道的端口可以继续使用本节中所述的单个LTSSM,也可以分为多个LTSSM。

- 如果上述规则都没满足,则在24ms超时后状态机跳转到Detect状态。

4.2.6.3.1.2 Upstream Lanes

-

在Configuration.Linkwidth.Start子状态,如果支持crosslink Port,则上层逻辑可以把TS1序列中把Disable Link字段设置为1,下个状态切换到Disabled。

-

在Configuration.Linkwidth.Start子状态,端口的上层逻辑可以通过把TS1和TS2序列中的Loopback字段设置为1让LTSSM状态机切换到Loopback状态,此时发送器作为Loopback Master。

-

在发送TS1序列集后又接收到两个连续的Disable Link字段设置为1的TS1序列集的任意Lane后,下个状态切换到Disabled状态。

- 如果支持crosslink,只有在所有正在发送TS1有序集的通道接收到两个连续的Disable Link字段设置为1的TS1有序集后,下一个状态切换到Disabled状态。

-

如果下述其中一个条件满足,则下个状态为Loopback状态:

-

发送TS1有序集的所有Lane也在接收TS1有序集,收到的两个连续的TS1有序集的Loopback字段被置1b。

-

任意发送TS1有序集的Lane收到了两个连续的Loopback字段置1b的TS1有序集且Enhanced Link Behavior Control字段被设置为1b。

-

请注意,接收到Loopback字段置1的有序集的设备将成为Loopback Slave。

-

-

发送器在所有有效的Upstream Lanes 上发送 Link number和Lane number 设置为PAD的TS1有序集;然后无效的Lane开始配置其链路宽度;并且如果upconfigure_capable设置为1b,则这些无效的Lane中的每一个都会在进入Recovery状态检测到从电气空闲退出,并且随后在此子状态下接收到两个Link number和Lane number 设置为PAD的TS1有序集。

-

从Polling转换到此子状态时,在Detect站柜台检测到接收器的任何通道均被视为有效通道。

-

从Recovery转换到此子状态时,在之前的Configuration.Complete完成配置的通道被视为有效通道。

-

从Recovery转换到此子状态时,如果转换不是由LTSSM超时引起的,如果发送器因自主原因更改链路宽度,则发送器必须将其在Configuration 状态下发送的TS1有序集中的Autonomous Change 字段设置为1b。

-

TS1有序集的Data Rate Identifier 字段必须通告端口支持的所有数据速率,包括它不打算使用的数据速率。

-

-

如果任-Lane接收到两个连续的Link number 设置为non-PAD且 Lane

number设置为PAD的TS1有序集,就在所有检测到Receiver的Lane 上发送 Link number 设置为某值且Lane number设置为PAD的TS1有序集,而在剩余Lane上必须发送Link number 和 Lane number设置为PAD的TS1有序集。如果满足下述条件中任意一个,则状态机跳转到Configuration.Linkwidth.Accept:-

如果LTSSM正在启动链路宽度配置,则它将在所有想要由无效变为有效的Lane上等待直到接收到两个连续的Link number设置为non-PAD且Lane number 设置为PAD的TS1有序集;或者在进入此子状态1ms后,在发送Link number设置为某值且Lane number设置为PAD的TS1有序集之前任意Lane上收到两个连续的Link number设置为non-PAD且Lane number 设置为PAD的TS1有序集。

-

建议在任何有可能在TS1有序集中接收到错误,或者丢失128b/130b块对齐的多通道链路;在使用8b/10b编码时,将上面列出的评估延迟额外两个或多个TS1有序集,或者在使用128b/130b编码时,将上述评估延迟额外34个或更多TS1有序集,但不能超过1ms,以免过早配置出更小的链路。

- 激活任何无效的通道后,发送器必须等待其TX共模电压建立,然后退出电空闲并发送TS1有序集。

-

-

可选的,如果LinkUp为0b并且支持交叉链路,则检测到Receiver的所有Upstream Lanes必须首先发送16-32个Link number 和Lane number设置为PAD的TS1有序集,然后如果任意上述Lane首先收到了两个连续的Link number和Lane number设置为PAD的TS1有序集,然后:

-

发送器继续发送Link number和Lane number 设置为PAD的TS1有序集。

-

如果任-Lane接收到两个连续的Link number 设置为non-PAD且Lane

number设置为PAD的TS1有序集,就在所有检测到Receiver的Lane上发送Link number 设置为某值且Lane number 设置为PAD的TS1有序集,而在剩余Lane上必须发送Link number和Lane number设置为PAD的TS1有序集。之后状态机跳转到Configuration.Linkwidth.Accept。- 建议在任何有可能在TS1有序集中接收到错误,或者丢失128b/130b块对齐的多通道链路;在使用8b/10b编码时,将上面列出的评估延迟额外两个或多个TS1有序集,或者在使用128b/130b编码时,将上述评估延迟额外34个或更多TS1有序集,但不能超过1ms,以免过早配置出更小的链路。

-

否则,在Tcrosslink超时后,将发送16-32个Link number和Lane number设置为PAD的TS2有序集。上游通道变为下游通道,且下一个状态为下游通道的Configuration.Linkwidth.Start。

- Note:对于交叉链路来说,此可选行为是必需的,在这种行为中,两个端口可能从上游端口开始,而其中一个最终将会成为下游端口。

-

-

如果上述规则都没满足,则在24ms超时后状态机跳转到Detect状态。

4.2.6.3.2 Configuration.Linkwidth.Accept

4.2.6.3.2.1 Downstream Lanes

- 如果配置的链路由至少一组通道组成,且这些通道接收到两个连续的具有相同Link number的TS1有序集(此Link number为non-PAD且与下游通道发送的相等),则Downstream Lane 就发送具有相同 Link number 且Lane number 设置为non-Pad 的TS1序列集。然后下一个状态跳转到Configuration.Lanenum.Wait。

- 分配的non-PAD Lane number必须在0到n-1之间,并顺序分配给接收相同 Link number的同一通道组,并且未接收TS1有序集的Downstream Lanes也不得破坏此初始链路编号。任何剩余的通道都必须传输 Link number 和 Lane number 设置为PAD的TS1有序集。

- 建议在任何有可能在TS1有序集中接收到错误,或者丢失128b/130b块对齐的多通道链路;在使用8b/10b编码时,将上面列出的评估延迟额外两个或多个TS1有序集,或者在使用128b/130b编码时,将上述评估延迟额外34个或更多TS1有序集,但不能超过1ms,以免过早配置出更小的链路。

- 如果满足以下所有条件,则use_modified_TS1_TS2_Ordered_Set 变量必须设置为1b:

LinkUp=0b;\text {LinkUp=0b;}LinkUp=0b;

自进入Polling 状态以来,该组件在处于Polling和Configuration状态时在TS1和TS2有序集的Symbol 5中的Enhanced Link Behavior Control 字段中发送了Modified TS1/TS2 Ordered Sets supported值(11b),并在轮询和配置状态下传输了TS2有序集。

在当前已配置的链路的所有通道上收到的八个连续的TS2有序集导致从Polling.Configuration到Configuration状态的转换,在Symbol5中的Enhanced Link Behavior Control字段中具有 Modified TS1/TS2 Ordered Sets supported (11b)。在接收的八个连续的TS2有序集中,32.0 GT/s data rate is supported字段设置为1b。

- 如果2ms超时,或者链路不能配置,或者所有Lane都收到两个连续的Link number和Lane

number设置为PAD的TS1有序集,下个状态就跳转到Detect状态。

4.2.6.3.2.2 Upstream Lanes

- 如果配置的链路可以由那些发送过non-PAD Link number且正在接受两个连续的Link number不变且Lane number为non-PAD 的TS1序列集的Lane组成,若没有通道反转,则在这些Lane 上发送 Link number和Lane number与接收值一致的TS1序列集,若存在通道反转,则在这些Lane上发送Link number与接收值一致且Lane number与接收值不同的TS1序列集。然后下一个状态跳转到Configuration.Lanenum.Wait。

- 新分配的Lane number必须在0到 m-1 的范围内,且必须按顺序分配给接收non-PAD Lane number的那些连续分组的通道(即,那些未接收任何TS1有序集的通道会破坏这个连续分组,它们不能包含在此分组内)。 m-1 必须等于或小于接收到的最大Lane number,即n-1。其余Lane必须传输 Link number和Lane number设置为PAD的TS1有序集。

- 建议在任何有可能在TS1有序集中接收到错误,或者丢失128b/130b块对齐的多通道链路;在使用8b/10b编码时,将上面列出的评估延迟额外两个或多个TS1有序集,或者在使用128b/130b编码时,将上述评估延迟额外34个或更多TS1有序集,但不能超过1ms,以免过早配置出更小的链路。

- 如果满足以下所有条件,则use_modified_TS1_TS2_Ordered_Set变量必须设置为1b:

LinkUp=0b;\text {LinkUp=0b;}LinkUp=0b;

自进入Polling状态以来,该组件在处于Polling和Configuration 状态时在TS1和TS2有序集的Symbol 5中的Enhanced Link Behavior Control 字段中发送了Modified TS1/TS2 Ordered Sets supported值(11b),并在轮询和配置状态下传输了TS2有序集。

在当前已配置的链路的所有通道上收到的八个连续的TS2有序集导致从Polling.Configuration到Configuration 状态的转换,在Symbol5中的Enhanced Link Behavior Control字段中具有 Modified TS1/TS2 Ordered Sets supported (11b)。在接收的八个连续的TS2有序集中,32.0 GT/s data rate is supported 字段设置为1b。

- 如果2ms超时,或者链路不能配置,或者所有Lane都收到两个连续的Link number和Lane

number设置为PAD的TS1有序集,下个状态就跳转到Detect状态。

IMPLEMENTATION NOTE

Example Cases

Notable examples related to the configuration of Downstream Lanes:

-

一个可以分为两个x4链路的x8的Downstream Port,它将两个不同的Link number发送给两个x4的Upstream Port∘Upstream Port通过选择两个Link number来同时响应。Downstream Port 必须选择其中一组配置为链路,而其余的则留给另外一个LTSSM进行配置(这会在Configuration.Complete中发生)。

-

一个可以分为两个x8链路的x16的Downstream Port连接到一个可以配置成x12、或x8和x4链路的x12的Upstream Port 上。在Configuration.Linkwidth.Start状态,Upstream Port在所有12个Lane上返回相同的Link number。然后,Downstream Port将发送相同的Link number 给Upstream Port,并在可以形成x8链路的八个Lane中发送Lane number,其余四个Lane 发送Link number和Lane number 设置为PAD的TS1有序集。

-

一个x8的Downstream Port,其中只有七个通道正在接收具有相同Link number的TS1有序集,而第八个通道位于这些通道的中间或相邻位置,它没有收到TS1有序集。在这种情况下,第八通道被视为与其他七个通道相同,x8通道的通道编号过程应如上所述进行。

Notable examples related to the configuration of Upstream Lanes:

- 一个x8的Upstream Port是由反向编号的Lane number表示的。如果上游端口支持通道反转,则Upstream Port会将相同的Lane number 发送回 Downstream Port。否则,相反的Lane number将发送回Downstream Port,以选择性地确定通道顺序或退出Configuration状态。

通道反转必须是Upstream Port支持的功能,Downstream Port不会实现此功能。具体来说,Upstream Port的通道反转大概是这种场景:默认的Upstream Port的通道编号(0到n-1)对应正在发送的Upstream Port的通道编号(n-1到0)。

- 一个x8的Upstream Port在其Lane 0上未收到TS1有序集,则:

a. 在Upstream Port只支持一个x8或x1链路并且还支持通道反转的情况下,Upstream Port将会只把接收到的Lane 7分配给Lane 0,其它七个Lane发送Link number和Lane number为PAD的TS1序列集。

b. 在Upstream Port只支持一个x8或x1链路并且不支持通道反转的情况下,不会形成任何链路并且链路会在2ms超时后进入Detect状态。

- 一个可以分成两个x4链路的x8的Upstream crosslink Port连接到两个具有相同Link nuber的x4的Downstream Port,并且每个x4的Downstream Port 同时显示分别编号为0到3的Lane number。Upstream Port 必须选择这些Lane number中的一组来配置为链路,而让另一组通过Configuration状态。

4.2.6.3.3 Configuration.Lanenum.Accept

4.2.6.3.3.1 Downstream Lanes

- 如果Downstream Lanes收到了两个连续的与其发送的non-PAD Link number和non-PAD Lane number相匹配的TS1序列集(如果支持通道反转,则收发的Lane number要翻转),则下个状态会跳转到Configuration.Complete 状态。注意:允许用 Retimer来延迟进入Configuration.Complete,此过程在Section 4.3.8中描述:

如果当前的Configuration是从Recovery状态转换而来的,则按照下述规则更新Link Status 寄存器的 Link Bandwidth Management Status 和 Link Autonomous Bandwidth Status 字段:

a.如果带宽变化是因Downstream Port 由可靠因素发出的,则Link Bandwidth Management Status=1b。

b. 否则,如果带宽变化不是因Downstream Port发起的且接收到的两个连续的TS1有序集的Autonomous Change字段为0,则Link Bandwidth Management Status=1b。

c. 否则,Link Autonomous Bandwidth Status=1b。

反转的通道号严格定义为Downstream Lane 0收到的TS1序列集中携带的Lane number 为 n-1, Downstream Lane n-1e的s1序集中携带的Lane number为0。

建议在任何有可能在TS1有序集中接收到错误,或者丢失128b/130b块对齐的多通道链路;在使用8b/10b编码时,将上面列出的评估延迟额外两个或多个TS1有序集,或者在使用128b/130b编码时,将上述评估延迟额外34个或更多TS1有序集,但不能超过1ms,以免过早配置出更小的链路。

如果链路可以由那些收到了两个连续的与其发送的non-PAD Link number 和 non-PAD Lane number 相匹配的TS1序列集的Lane组成,则在这些Lane上发送具有相同Link number 以及新的Lane number的TS1序列集,并且下个状态会转换到Configuration.Lanenum.Wait 状态。

新分配的Lane number必须在0到 m-1 的范围内,且必须按顺序分配给接收non-PAD Lane number的那些连续分组的通道(即,那些未接收任何TS1有序集的通道会破坏这个连续分组,它们不能包含在此分组内)。m-1必须等于或小于接收到的最大Lane number,即 n-1∘ 其余Lane 必须传输 Link number和Lane number设置为PAD的TS1有序集。

建议在任何有可能在TS1有序集中接收到错误,或者丢失128b/130b块对齐的多通道链路;在使用8b/10b编码时,将上面列出的评估延迟额外两个或多个TS1有序集,或者在使用128b/130b编码时,将上述评估延迟额外34个或更多TS1有序集,但不能超过1ms,以免过早配置出更小的链路。

如果无法配置链路,或者在所有Lane上收到两个连续的Link number与Lane number为PAD的TS1序列集,则状态机跳转到Detect状态。

4.2.6.3.3.2 Upstream Lanes

如果Upstream Lanes 收到了两个连续的与其发送的non-PAD Link number 和 non-PAD Lane number 相匹配的TS1序列集,则下个状态会跳转到Configuration.Complete状态。注意:允许用Retimer来延迟进入Configuration.Complete,此过程在Section 4.3.8中描述。

如果链路可以由那些收到了两个连续的与其发送的non-PAD Link number和 non-PAD Lane number 相匹配的TS1序列集的Lane组成,则在这些Lane上发送具有相同Link number 以及新的Lane number的TS1序列集,并且下个状态会转换到Configuration.Lanenum.Wait状态。

新分配的Lane number必须在0到m-1的范围内,且必须按顺序分配给接收non-PAD Lane number的那些连续分组的通道(即,那些未接收任何TS1有序集的通道会破坏这个连续分组,它们不能包含在此分组内)。m-1必须等于或小于接收到的最大Lane number,即n-1。其余Lane必须传输 Link number和Lane number 设置为PAD的TS1有序集。

建议在任何有可能在TS1有序集中接收到错误,或者丢失128b/130b块对齐的多通道链路;在使用8b/10b编码时,将上面列出的评估延迟额外两个或多个TS1有序集,或者在使用128b/130b编码时,将上述评估延迟额外34个或更多TS1有序集,但不能超过1ms,以免过早配置出更小的链路。

如果无法配置链路,或者在所有Lane上收到两个连续的Link number与Lane number为PAD的TS1序列集,则状态机跳转到Detect状态。

4.2.6.3.4 Configuration.Lanenum.Wait

4.2.6.3.4.1 Downstream Lanes

如果检测到Receiver的Lane收到两个连续的Lane number与刚进入Configuration.Lanenum.Wait时收到的Lane值不同的TS1序列集,并且不是所有Lane的Link number都设置为PAD或者在所有Lane上收到了两个连续的Lane number与Link number 与其之前发送的一致的TS1序列集,则下个状态跳转到Configuration.Lanenum.Accept。

在转换到Configuration.Lanenum.Accept之前,允许 Upstream Lanes 延迟1ms。目的是为了防止收到的错误或在通道之间的skew影响最终配置的链路宽度。

上述条件隐含两个点:一个是两个Port要链路宽度协商完成,一个是在转换到Configuration.Lanenum.Accept时 Lane number 发生了改变。

为了允许两个端口以协商的链路宽度为基础,要求接收与Lane首次进入Configuration.Lanenum.Wait时不同的任何Lane Number的条件是必要的。语句“任何一个Lane都接收两个连续的TS1有序集,其Lane Number与Lane 首次进入Configuration.Lanenum.Wait 时的Lane Number 不同”的确切含义要求Lane Number 必须与最近的在切换到Configuration.Lanenum.Accept之前进入Configuration.Lanenum.Wait时的改变值。

如果2ms超时,或者所有Lane都收到两个连续的Link number 和Lane number 设置为PAD的TS1有序集,下个状态就跳转到Detect状态。

4.2.6.3.4.2 Upstream Lanes

如果满足下述两个条件中的一个,状态机就跳转到Configuration.Lanenum.Accept。

a. 如果任意Lane收到两个连续的Lane number与刚进入Configuration.Lanenum.Wait时收到的Lane值不同的TS1序列集,并且不是所有Lane的Link number都设置为 PAD0

b.如果任意Lane收到两个连续的TS2序列。

如果2ms超时,或者所有Lane都收到两个连续的Link number和Lane number 设置为PAD的TS1有序集,下个状态就跳转到Detect状态

4.2.6.3.5 Configuration.Complete

4.2.6.3.5.1 Downstream Lanes

在此子状态下,Downstream Lane 会发送与收到的TS1序列集中Link number和Lane number一致的TS2序列集。

可以把TS2有序集的Upconfigure Capability字段置为1,表示此Port 可以在此分配的 Lane0 上支持x1链路,并且在LinkUp=1的时候可以向上配置(up-configuring)链路。通告这个能力是个可选择实现的功能。

Upconfigure Capability 可以在 LinkUp=1 的时候重新进入Configuration状态以协商是否要upsize或downsize链路宽度。

在此子状态退出时必须要为LOs设置好N_FTS值。

当使用8b/10b编码时,在此子状态退出时必须完成Lane-to-Lane de-skew。

如果传输的TS2序列集中的Disable Scrambling字段有效,则禁用加扰功能。

在所有配置的Lane 上发送 Disable Scrambling置1的训练序列的Port本身也需要禁用加扰。加扰功能只能在8b/10b 编码的时候可以被禁用。

如果在发送TS2序列集的所有Lane上收到了8个有相同Link number和Lane number 且 Data Rate Identifiers 字段相同(Link Upconfigure Capability也相同)的TS2序列集,并且在收到一个TS2序列集之后发送完16个TS2序列集,状态机就立马跳转到Configuration.Idle 状态。当数据速率为2.5 GT/s时,将Link Capabilities 2寄存器的 Retimer Presence Detect Supported 字段设置为1b的实现也必须接收八个连续的Retimer Present字段相同的TS2有序集。当数据速率为2.5GT/s时,将Link Capabilities 2寄存器的Two Retimers Presence Detect Supported字段设置为1b的实现也必须接收八个连续的Retimer Present 字段相同的TS2有序集。

如果数据速率为2.5GT/s:

如果Link Capabilities 2 寄存器的 Retimer Presence Detect Supported 字段设置为1b,并且任何已配置通道在八个连续接收的Retimer Present字段设置为1b的TS2有序集,则必须在Link Status 2寄存器中将Retimer Presence Detected字段设置为1b,否则设置为0b。

如果Link Capabilities 2寄存器的Two Retimer Presence Detect Supported 字段设置为1b,并且任何已配置通道在八个连续接收的Two Retimer Present字段设置为1b的TS2有序集,则必须在Link Status 2寄存器中将Two Retimer Presence Detected字段设置为1b,否则设置为0b。

如果设备支持大于2.5GT/s的data rate,它必须记录下载所有Lane 上收到的Data Rate Identifiers。这可能会覆盖之前记录的data rate值。定义了一个用于在Recovery状态切换data rate的变量 changed_speed_recovery,该变量在此子状态下设置为0b。

如果设备发送的TS2有序集中携带的Link Upconfigure Capability字段为1,并且收到了8个连续的Link Upconfigure Capability字段为1的TS2序列集,则upconfigure_capable 变量设置为1,否则设置为0。

所有未经配置的剩余的Lane不再与LTSSM有任何关系,他们必须做如下处理:

1)如果支持多个LTSSM,则可以用新的LTSSM来处理。

2)或者,所有没有与新的LTSSM关联的其他Lane进入电气空闲状态。建议保留这些通道的Receiver terminations。如果未将其保留,则必须在LTSSM进入Recovery.RcvrCfg时将其打开,直到达到Configuration.Complete子状态(如果upconfigure_capable 设置为1b以允许潜在的链路宽度的upconfiguration)。在通过LO进行初始链路训练期间,任何不属于LTSSM的通道都不能成为LTSSM的一部分,这是链路宽度upconfiguration过程的一部分。

在crosslink情况下,Receiver terminations 必须满足 Table 8-10定义的 ZRX-HIGH-IMP-DC-POS和 ZRX-HIGH-IMP-DC-NEG 。

这些Lane必须在LTSSM进入Detect状态之后,与LTSSM重新建立联系。

在进入电气空闲状态之前没必要发送EIOS,也没必要在符号或有序集的边缘进入电气空闲状态。

2ms超时后,

如果当前data rate是2.5GT/s或者5GT/s,下个状态就跳抓到Detect状态。

如果idleolockransitioned<FFh,且当前 data rate是8GT/s或更高,下个状态跳转到Configuration.ldle。

changed_speed_recovery 复位成0。

不属于已配置链路的Lane不再与正在工作的LTSSM相关联,并且要符合上述1)和2)的non-timeeout的进入Configuration.Idle 状态的条件。

upconfigure_capable 可以被设置。如果训练序列的Link Upconfigure Capabilitity=1∼b,upconfigure_capable 就设置为1b,反之设置为0b。

否则,下个状态就跳抓到Detect状态。

4.2.6.3.5.2 Upstream Lanes

在此子状态下,Downstream Lane会发送与收到的TS1序列集中Link number和Lane number一致的TS2序列集。

可以把TS2有序集的Upconfigure Capability字段置为1,表示此Port可以在此分配的Lane0上支持x1链路,并且在LinkUp=1的时候可以向上配置(up-configuring)链路。通告这个能力是个可选择实现的功能。

在此子状态退出时必须要为LOs设置好N_FTS值。

当使用8b/10b编码时,在此子状态退出时必须完成Lane-to-Lane de-skew。

如果传输的TS2序列集中的Disable Scrambling字段有效,则禁用加扰功能。

在所有配置的Lane 上发送 Disable Scrambling置1的训练序列的Port本身也需要禁用加扰。加扰功能只能在8b/10b 编码的时候可以被禁用。

如果在发送TS2序列集的所有Lane上收到了8个有相同Link number和Lane number 且 Data Rate Identifiers 字段相同(Link Upconfigure Capability也相同)的TS2序列集,并且在收到一个TS2序列集之后发送完16个TS2序列集,状态机就立马跳转到Configuration.Idle 状态。当数据速率为2.5 GT/s时,将Link Capabilities 2寄存器的Retimer Presence Detect Supported 字段设置为1b的实现也必须接收八个连续的Retimer Present字段相同的TS2有序集。当数据速率为2.5GT/s时,将Link Capabilities 2 寄存器的Two Retimers Presence Detect Supported字段设置为1b的实现也必须接收八个连续的Retimer Present 字段相同的TS2有序集。

如果数据速率为2.5GT/s:

如果Link Capabilities 2 寄存器的 Retimer Presence Detect Supported 字段设置为1b,并且任何已配置通道在八个连续接收的Retimer Present字段设置为1b的TS2有序集,则必须在Link Status 2寄存器中将Retimer Presence Detected字段设置为1b,否则设置为0b。

如果Link Capabilities 2寄存器的Two Retimer Presence Detect Supported 字段设置为1b,并且任何已配置通道在八个连续接收的Two Retimer Present字段设置为1b的TS2有序集,则必须在Link Status 2寄存器中将Two Retimer Presence Detected字段设置为1b,否则设置为0b。

如果设备支持大于2.5GT/s的data rate,它必须记录下载所有Lane 上收到的Data Rate Identifiers。这可能会覆盖之前记录的data rate值。定义了一个用于在Recovery状态切换data rate的变量 changed_speed_recovery,该变量在此子状态下设置为0b。

如果设备发送的TS2有序集中携带的Link Upconfigure Capability 字段为1,并且收到了8个连续的Link Upconfigure Capability 字段为1的TS2序列集,则upconfigure_capable变量设置为1,否则设置为0。

所有未经配置的剩余的Lane不再与LTSSM有任何关系,他们必须做如下处理:

1)如果支持多个LTSSM,则可以用新的 crosslink LTSSM来处理。

- 或者,所有没有与新的crosslink LTSSM关联的Lane进入电气空闲状态。建议保留这些通道的Receiver terminations。如果未将其保留,则必须在LTSSM进入Recovery.RcvrCfg时将其打开,直到达到Configuration.Complete子状态(如果upconfigure_capable 设置为1b以允许潜在的链路宽度的upconfiguration)。在通过LO进行初始链路训练期间,任何不属于LTSSM的通道都不能成为LTSSM的一部分,这是链路宽度upconfiguration过程的一部分。

这些Lane必须在LTSSM进入Detect状态之后,与LTSSM重新建立联系。

在进入电气空闲状态之前没必要发送EIOS,也没必要在符号或有序集的边缘进入电气空闲状态。

2ms超时后,

- 如果当前data rate是2.5GT/s或者5GT/s,下个状态就跳抓到Detect状态。

如果 idleolockransitioned<FFh,且当前data rate是8GT/s或更高,下个状态跳转到Configuration.Idle。

changed_speed_recovery复位成0。

不属于已配置链路的Lane不再与正在工作的LTSSM相关联,并且要符合上述1)和2)的non-timeeout的进入Configuration.Idle 状态的条件。

upconfigure_capable 可以被设置。如果训练序列的Link Upconfigure Capabilitity=1∼b,upconfigure_capable 就设置为1b,反之设置为 Obo

否则,下个状态就跳抓到Detect状态。

4.2.6.3.6 Configuration.Idle

在此子状态下,当使用8b/10b编码,发送器会在所有已配置的Lane上发送Idle data Symbol。

如果LinkUp=0∼b且链路的所有组件都支持32.0GT/s数据速率,就如在进入Configuration.Idle之前收到的八个连续的TS2或八个连续且相同的modified TS2 Ordered Set中通告的那样,则:

如果在收到的八个连续且相同的modified TS2 Ordered Set 中将No Equalization Needed 字段设置为1b,并且还在链路的所有已配置通道中的已发送modified TS2 Ordered Set中进行了设置;或者在收到的八个连续且相同的modified TS2Ordered Set 中将 Enhanced Link Behavior Control字段设置为10b,并且还在链路的所有已配置通道中的已发送modified TS2 Ordered Set 中进行了设置,则:

equalization_done_8GT_data_rate、equalization_done_16GT_data_rate 和 equalization_done_32GT_data_rate 变量设置为1b。

32.0 GT/s Status Register 中的 No Equalization Needed Received 设置为1b。

或者,如果在收到的八个连续且相同的 modified TS2 Ordered Set 中将 Equalization bypass to highest rate support字段设置为1b,并且还在链路的所有已配置通道中的已发送 modified TS2 Ordered Set中进行了设置;或者在收到的八个连续且相同的modified TS2 Ordered Set 中将 Enhanced Link Behavior Control 字段设置为01b或10b,并且还在链路的所有已配置通道中的已发送 modified TS2 Ordered Set 中进行了设置,则:

equalization_done_8GT_data_rate、equalization_done_16GT_data_rate 变量设置为1b。

如果进入此子状态是由于接收到八个连续且相同的modified TS2 Ordered Set 且 LinkUp=0b:

如果在接收到的八个连续的modified TS2 Ordered Set 中将 Modified TS Usage 字段设置为010b(备用协议),并且在在链路的所有已配置通道中,已发送的modified TS2 Ordered Set的 Modified TS Usage 字段设置为相同值,并且 Modified TS Information 1和 Alternate Protocol Vendor ID 字段在发送和接收的 modified TS2 Ordered Set 中有相同的值,则:

32.0 GT/s Status 寄存器中的Modified TS Received 字段设置为1b。基于接收到的八个连续的modified TS2Ordered Set,协商的详细信息将反映在Received Modified TS Data 1 Register 和 Received Modified TS Data 2Register中。

当使用128b/130b编码:

当数据速率为8.0GT/s,发送器会在所有已配置的Lane上先发送一个SDS有序集,然后紧跟着发Idle data Symbol。Lane 0上的第一个Idle data Symbol 就是数据流的第一个符号。

当数据速率为16.0GT/s或更高,则发送器在所有已配置通道上发送一个Control SKP Ordered Set,然后立即发送一个SDS有序集以启动数据流,然后在所有已配置通道上发送Idle data Symbol。在Lane 0上发送的第一个Idle data Symbol是数据流的第一个符号。

接收器在此子状态下等待接收Idle data。

LinkUp = 1b

当使用8b/10b编码,如果在所有已配置的Lane上接收到8个连续的Idle data并且在接收到一个Idle data后发送完16个Idle data,状态机就跳转到LO。

如果自上次从Recovery或Configuration进入L0后,软件将Link Control寄存器的Retrain Link字段写成1b,则Downstream Port 必须设置 Link Status 寄存器的 Link Bandwidth MManagement Status字段。

状态机切换到LO后,use_modified_TS1_TS2_Ordered_Set变量重置为0b。

当使用128b/130b编码,如果在所有已配置的Lane上接收到8个连续的Idle data并且在接收到一个Idle data后发送完16个Idle data,并且此状态不是由Configuration.Complete超时而进入的,状态机就跳转到 LO0

此时的Idle data 必须在接收的Data Block里。

数据流处理开始之前必须完成Lane-to-Lane de-skew。

如果自上次从Recovery或Configuration进入L0后,软件将Link Control寄存器的Retrain Link字段写成1b,则Downstream Port 必须设置Link Status 寄存器的Link Bandwidth Management Status字段。

在切换为LO时idle_to_rlock_transitioned 变量复位为00h。

否则,在2ms超时后执行下述操作:

如果idle_to_rlock_transitioned<FFh,状态机跳转到Recovery.RcvrLock。

在转换到Recovery.RcvrLock时,

如果data rate是8GT/s, idle_to_rlock_transitioned 自增1。

如果 data rate是2.5GT/s或5GT/s,idle_to_rlock_transitioned 直接设置为FFh。

否则,状态机跳转到Detect。

idle_to_rlock_transitioned定义的是从Configuration.Idle 跳转到Recovery.RcvrLock的次数。