【计组】指令与CPU

ISA(指令集体系结构)

ISA完整定义了软件与硬件之间的接口,是机器语言/汇编语言程序员熟悉的

内容

- 指令格式,指令寻址方式,操作类型,每种操作对应的操作数的相应规定

- 操作数的类型,操作数寻址方式,按大端/小端存放

- 程序可访问的寄存器编号、个数、位数,存储空间的大小和编址方式

- 指令执行过程的控制方式等,包括程序计数器、条件码定义

RISC和CISC

RISC

定长指令

流水线

硬布线

只允许load/store访存

CISC

不定长指令

微程序

访存指令不受限制

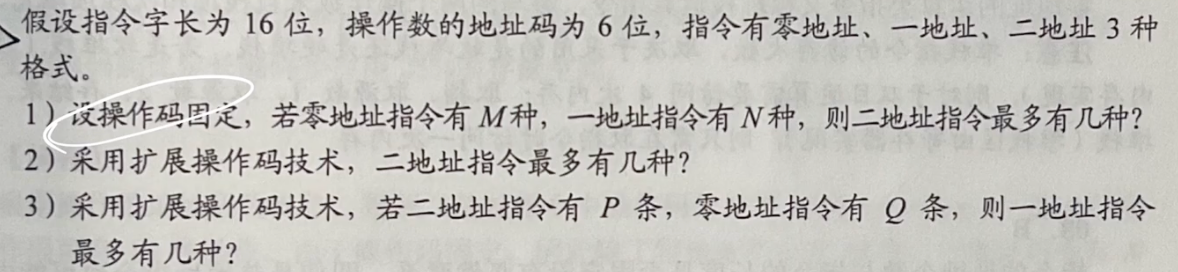

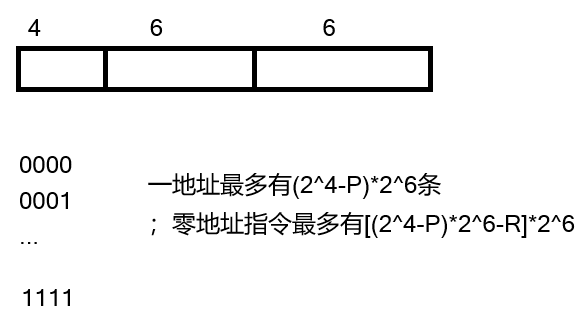

扩展操作码

n位操作码的指令共有

条 零地址+一地址+二地址+... 一共

条

x地址指令条数=2^{新扩展的操作码位数}*(x+1地址留下的扩展窗口数量)-给x-1地址留下的扩展窗口数量

寻址方式

隐含寻址

间接寻址

寄存器寻址

寄存器间接寻址

立即寻址

堆栈寻址

基址寻址

变址寻址

直接寻址

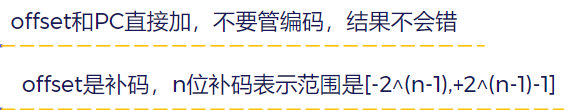

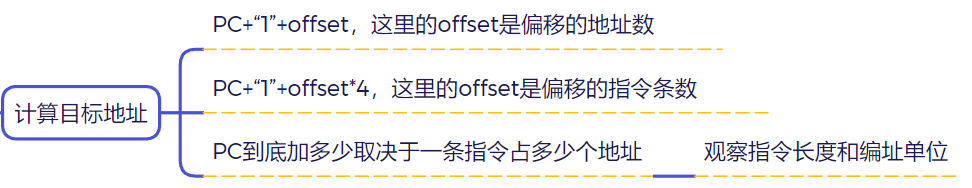

相对寻址

汇编

常见助记符

编址单位、指令字长、指令地址

数据通路

指令执行过程

1.取指令并计算下一跳指令的地址

2.对指令操作码译码

3.计算源操作数地址并取源操作数

4.数据操作

5.计算目的操作数地址并存结果

组成

组合逻辑元件(操作元件)

MUX

加法器

ALU

译码器

存储元件(状态元件)

流水段锁存器

IR

通用寄存器

输出带三态门的寄存器,三态门用来决定信息是否送至总线

带计数功能的寄存器

带移位功能的寄存器

带清零复位功能的寄存器

时序系统

机器周期

一个指令周期可分为取指令、读操作数、执行、写结果等多个基本工作周期称为机器周期

每个机器周期长短可能不同

一个机器周期会划分成若干节拍,每个动作在一个节拍内完成

总线特征

每个节拍每个总线只能有一种数据

每个节拍每个总线上只能有一种控制信号

控制器

硬布线

微程序

指令流水线

五段式流水线

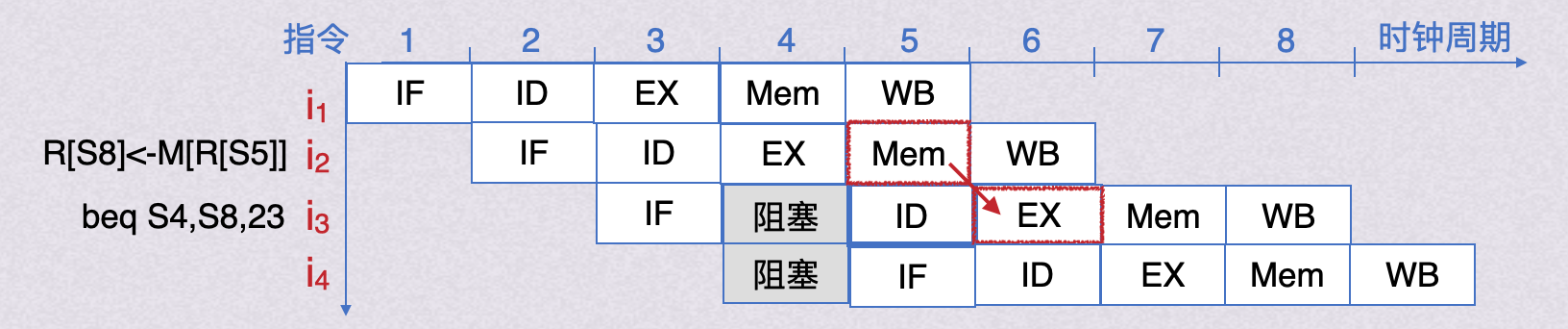

条件转移指令

EX阶段比较个数

MEM阶段决定是否跳转,将目的地址写回PC

WB阶段空段

无条件转移指令

EX阶段将目标地址写回PC

MEM阶段、WB阶段空段

冒险

结构冒险

不同指令争用同一功能部件产生资源冲突时产生的

设置多个功能部件

控制冒险

遇到改变指令正常执行顺序的情况,如转移、调用、返回指令时,会修改PC值,造成断流

对指令进行分支预测,尽早生成转移目标地址

数据冒险

写后读

load/use冒险

- 前一条指令为访存并将数据存储到存储器,后一条指令需要使用该数据

- load-use冒险在ID阶段进行检测,检测到后必须使load后的两条指令停顿一个时钟周期后继续执行

- 配合数据旁路,将load指令MEM阶段取到的数据送到use指令的EX阶段

- use指令先ID还是先阻塞都可以

数据旁路:从得到需要数据的流水段锁存器直接送至ALU的输入端

插入气泡stall或空操作指令NOP

将寄存器写口和读口分别控制在前后半个时钟周期内操作

多发技术

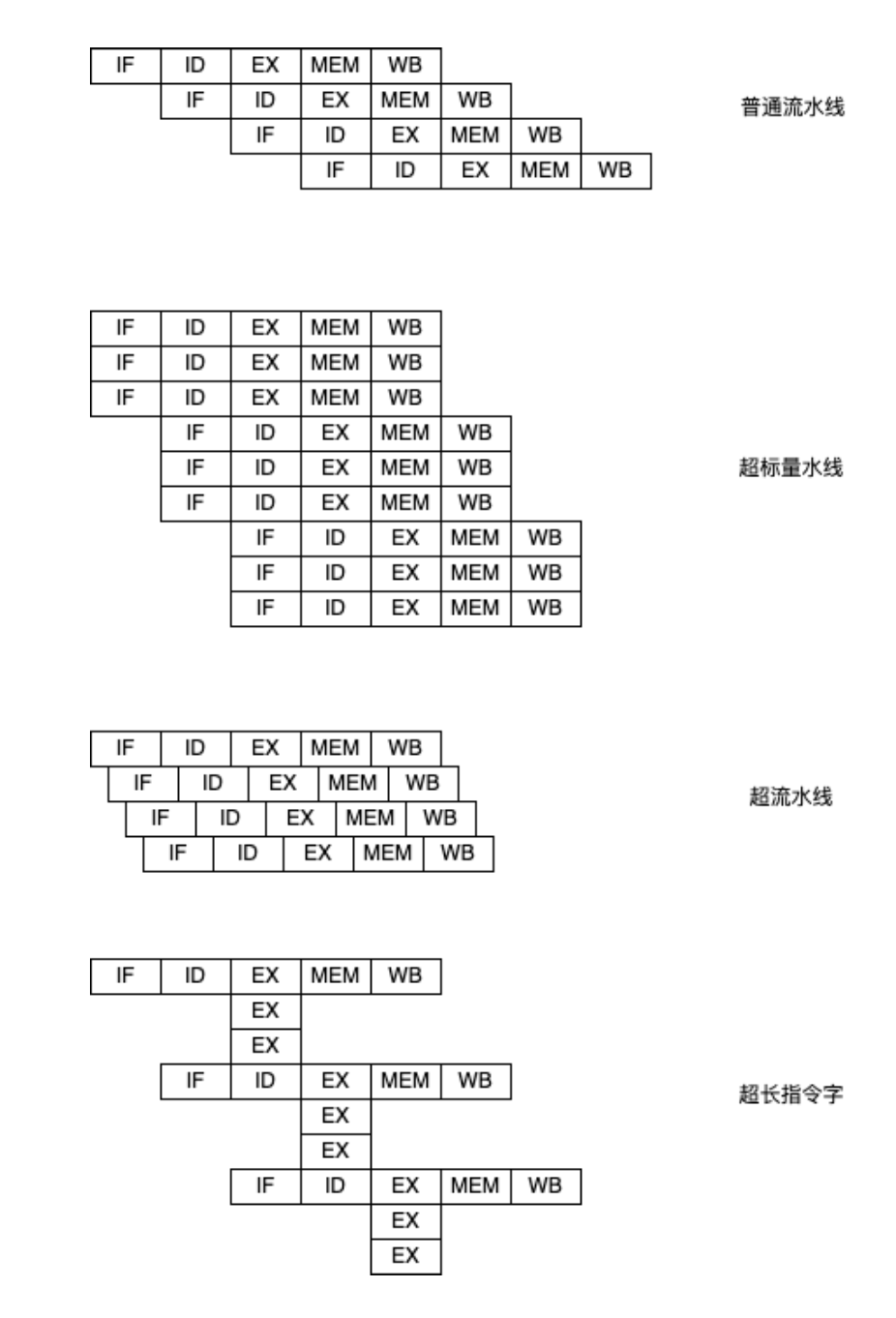

超标量

一次同时发射多条指令

CPI<1

超流水线

将每个段更细地划分

时钟周期变短

超长指令字

把多条能并行的指令组合成一条具有多个操作码字段的超长指令