IC验证 AHB-RAM 项目(二)——接口与事务代码的编写

目录

- 准备工作

- 接口相关代码编写

- 事务相关代码编写

准备工作

DVT(Design and Verification Tools)是一款专门为 IC 验证打造的 IDE 插件,可以理解为智能的 Verilog/System Verilog 编辑器,在 VS Code、Eclipse 软件中使用。

接口相关代码编写

- lvc_ahb_if.sv 是面向 DUT 的接口,方便 TB 与 DUT 建立总线通信

- rkv_ahbram_if.sv 是面向 TB 的接口,提供全局的 testbench 控制

- rkv_ahbram_tb.sv 是 TB 顶层文件,由于时钟信号较为固定,无需在后续测试过程中更改,所以可以把时钟信号生成的代码放于此

下面将介绍各文件的代码更新内容:

- lvc_ahb_defines.svh

- 定义 AHB 总线相关的宏

- lvc_ahb_if.sv

- 定义 AHB 总线信号

- rkv_ahbram_if.sv

- 定义时钟和复位信号

- 定义 task 任务产生复位信号,interface 里定义的 task/function 都是静态的,为了避免出现多个进程同时调用时,局部变量被覆盖的情况,这里使用动态任务

task automatic assert_reset(input int active_cycles = 5, // 复位保持多少个时钟周期input int start_delay = 0 // 复位开始前延迟多少个时钟周期

);rstn <= 1;repeat(start_delay) @(posedge clk); // 等待 start_delay 个时钟周期后开始复位rstn <= 0;repeat(active_cycles) @(posedge clk); // 复位保持 active_cycles 个时钟周期后释放复位rstn <= 1;

endtask

- rkv_ahbram_tb.sv

- 例化接口 lvc_ahb_if 类和 rkv_ahbram_if 类

- 使用 lvc_ahb_if 类的 interface 实例化 DUT(设计文件:ahb_blockram_32.v)

- 产生时钟信号

事务相关代码编写

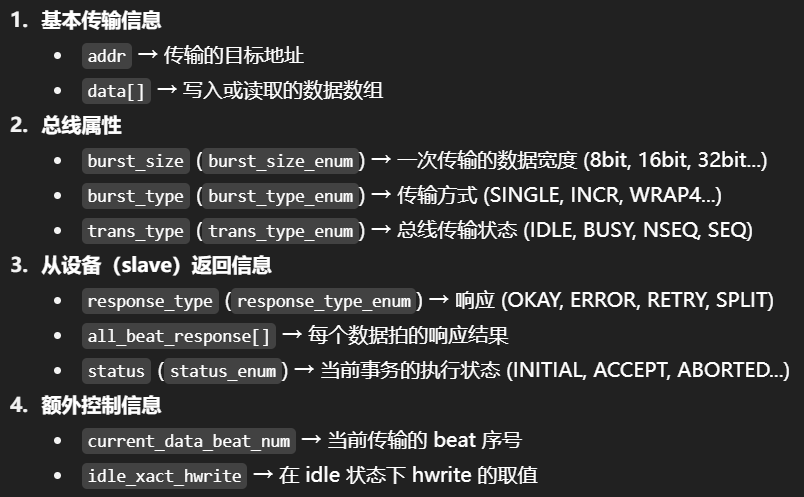

- lvc_ahb_types.sv 集中定义了协议里各种枚举类型

- lvc_ahb_transaction.sv 用于存放一次 AHB 传输需要的变量。作为输入激励,需要 sequence 随机化生成的变量定义为 rand 类型;仿真过程中记录/监测的变量为 非rand