模拟IC设计提高系列8-运算跨导放大器OTA Operational Transconduct Amplifiers

1.gmid设计方法

2. CMOS开关电路

3. 数模转换器DAC设计

4. 基准电流源

5. 工艺角与蒙特卡洛仿真

6. Library导入与新建Library

7. layout版图绘制技巧

8. 运算跨导放大器OTA Operational Transconduct Amplifiers

8.1 概述

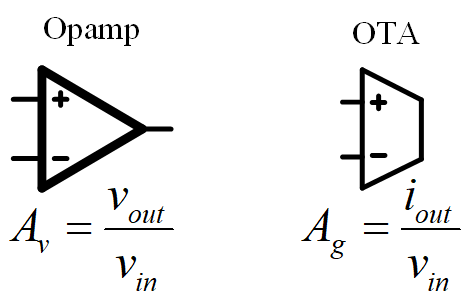

8.1.1 两种电压输入的放大器

8.1.1.1 1 运算放大器 Opamp

当输入电压,输出也为电压时,我们称这种放大器为运算放大器。

- 输入是电压——要求运放的输入阻抗要大,保证电压尽可能地落在运放输入端;

- 输出是电压——要求运放的输出阻抗要小,保证电压尽可能地落在下一级输入。

8.1.1.2 运算跨导放大器 OTA (Operational Transconduct amplifier)

当输入电压,输出电流时,我们称这种放大器为运算跨导放大器OTA。

- 输入是电压——要求运放的输入阻抗要大,保证电压尽可能地落在运放输入端;

- 输出是电流——要求运放的输出阻抗要大,保证电流尽可能地流到下一级输入。

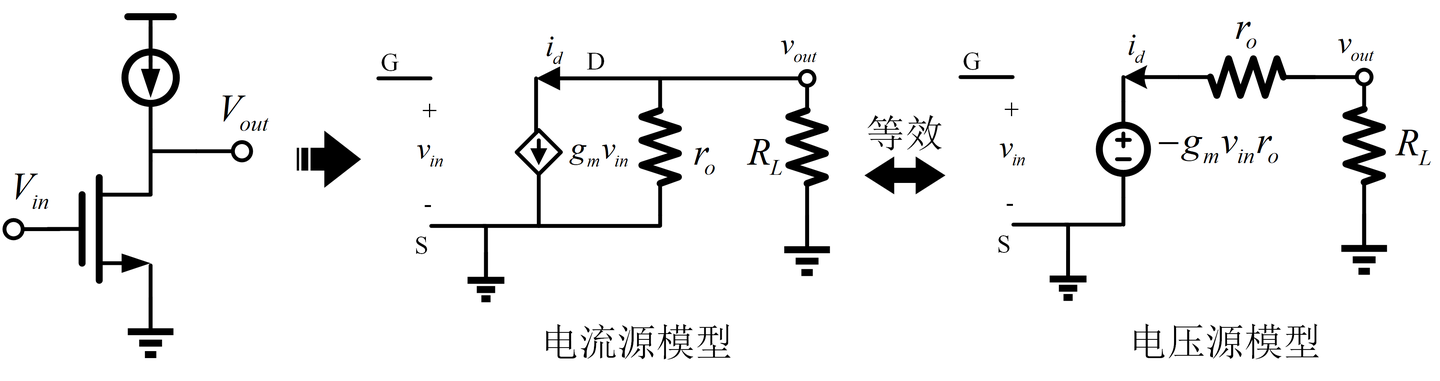

8.1.1.3 两种等效的MOS放大器模型

对于一个理想电流源负载的CS AMP,我们做出其小信号模型,通常我们会将其建模为电流源模型,那么有:

vout=−gmvinrout=−gmvin∥(ro∥RL)v_{out} = -g_m v_{in} r_{out} = -g_m v_{in} \parallel (r_o \parallel R_L) vout=−gmvinrout=−gmvin∥(ro∥RL)

将这一表达式进一步改写为:

vout=−gmvinroRLro+RL=−gmvinroRLro+RLv_{out} = -g_m v_{in} \frac{r_o R_L}{r_o + R_L} = -g_m v_{in} r_o \frac{R_L}{r_o + R_L} vout=−gmvinro+RLroRL=−gmvinroro+RLRL

这样改写得到的式子,若我们将(-g_m v_{in} r_o)视为一个电压源,则表达式中的RLro+RL\frac{R_L}{r_o + R_L}ro+RLRL代表输出电压voutv_{out}vout时电压源(−gmvinro)(-g_m v_{in} r_o)(−gmvinro)在RLR_LRL与ror_oro串联结构上的分压。即MOS模型还可以表示为右图的电压源形式。

分析上面两个表达式,我们可以知道,在建模为电流源模型时(OTA),模型的内阻ror_oro很大,利于作为电流源输出;而建模为电压源输出时(Opamp),模型的大内阻反而导致负载的分压很低。

所以具体情况使用那种模型取决于负载的阻抗。

当负载阻抗不是很大时,使用电流源模型更合适;

当负载阻抗非常大时(RL≫roR_L \gg r_oRL≫ro),使用电压源模型更合适。

8.1.2 运放性能参数介绍与理解

8.1.2.1 增益Gain

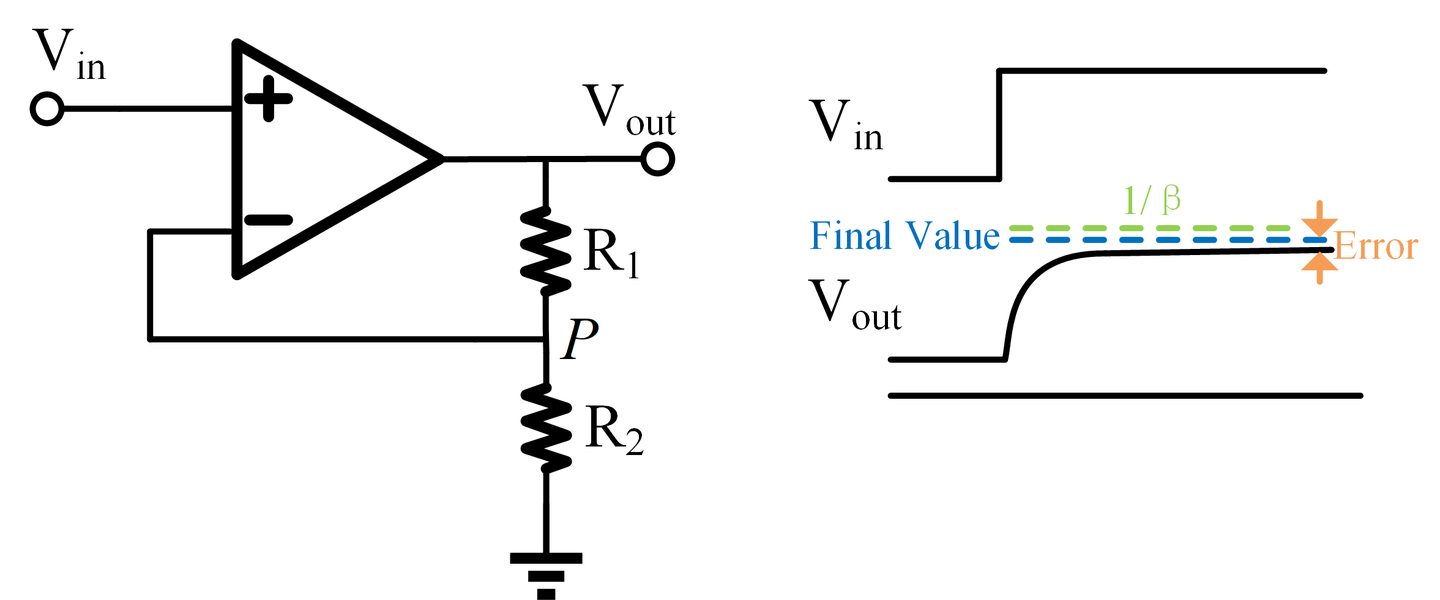

对于运放,增益影响主要是闭环增益的准确度。

若我们要求这个同相放大器的闭环增益为:

1β=R2R1+R2=10\frac{1}{\beta} = \frac{R_2}{R_1 + R_2} = 10 β1=R1+R2R2=10

且要求实际增益与目标增益的误差(即增益误差)小于1%,那么我们有:

{Acl=VoutVin=A01+βA0Error(Acl)=(1β−1ββA01+βA0)/1β<0.01\begin{cases} A_{cl} = \frac{V_{out}}{V_{in}} = \frac{A_0}{1+\beta A_0} \\ Error(A_{cl}) = (\frac{1}{\beta} - \frac{1}{\beta} \frac{\beta A_0}{1 + \beta A_0}) / \frac{1}{\beta} < 0.01 \end{cases} {Acl=VinVout=1+βA0A0Error(Acl)=(β1−β11+βA0βA0)/β1<0.01

解得:

A0>990A_0 > 990 A0>990

从上述计算我们了解了如何确定开换增益A0A_0A0,且证明了大增益最重要的作用就是提高环路增益的准确性。

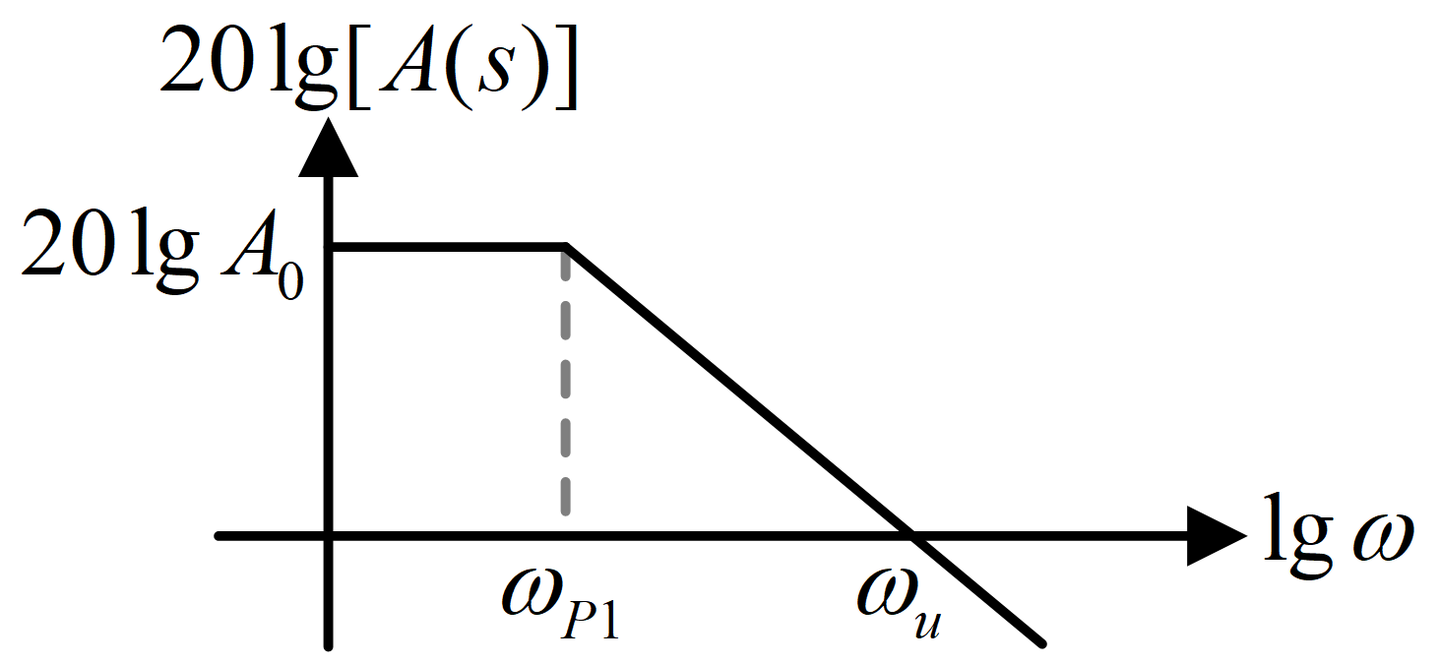

8.1.2.2 小信号带宽

对于单极点系统,近似地,ωp1\omega_{p1}ωp1即为-3dB频率点,ωu\omega_uωu为单位增益频率(此时运放增益降低到1)。

且在ωp1\omega_{p1}ωp1之后,频率每增大10倍,增益下降20dB,20dB就是10倍,增益减小10倍,增益带宽积保持不变,那么单位增益频率ωu\omega_uωu可以表示为:

ωu≈A0ω0\omega_u \approx A_0 \omega_0 ωu≈A0ω0

而带宽其实与电路的速度息息相关,下面以一个正向放大器的设计为例说明。

若我们要求这个同相放大器的闭环增益为:

1β=R2R1+R2=10\frac{1}{\beta} = \frac{R_2}{R_1 + R_2} = 10 β1=R1+R2R2=10

且要求在Vin的阶跃信号的5ns后,Vout的setting error(图中橙色所指,为终值和5ns时的Vout值的误差)要小于1%,求电路的增益带宽积的范围。我们有:

{A(s)=A01+s/ωoβ=R2R1+R2\begin{cases} A(s) = \frac{A_0}{1+s/\omega_o} \\ \beta = \frac{R_2}{R_1+R_2} \end{cases} {A(s)=1+s/ωoA0β=R1+R2R2

求得闭环增益为:

Acl=VoutVin(s)=1ββA(s)1+βA(s)=1ββA01+βA011+s/[(1+βA0)ω0]=1ββA01+βA011+s/ωP{A_{cl}} = \frac{{{V_{out}}}}{{{V_{in}}}}(s) = \frac{1}{\beta }\frac{{\beta A(s)}}{{1 + \beta A(s)}} = \frac{1}{\beta }\frac{{\beta {A_0}}}{{1 + \beta {A_0}}}\frac{1}{{1 + s/[(1 + \beta {A_0}){\omega _0}]}} = \frac{1}{\beta }\frac{{\beta {A_0}}}{{1 + \beta {A_0}}}\frac{1}{{1 + s/{\omega _P}}} Acl=VinVout(s)=β11+βA(s)βA(s)=β11+βA0βA01+s/[(1+βA0)ω0]1=β11+βA0βA01+s/ωP1

那么有:

{ωP=(1+βA0)ω0τ=1ωP=1(1+βA0)ω0≈1βA0ω0\begin{cases} {\omega _P} = (1 + \beta {A_0}){\omega _0}\\ \tau = \frac{1}{{{\omega _P}}} = \frac{1}{{(1 + \beta {A_0}){\omega _0}}} \approx \frac{1}{{\beta {A_0}{\omega _0}}} \end{cases} {ωP=(1+βA0)ω0τ=ωP1=(1+βA0)ω01≈βA0ω01

若输入电压为Vin=Vdu(t)V_{in} = V_d u(t)Vin=Vdu(t),那么有:

Vout(t)=Vd1ββA01+βA0(1−e−t/τ){V_{out}}(t) = {V_d}\frac{1}{\beta }\frac{{\beta {A_0}}}{{1 + \beta {A_0}}}(1 - {e^{ - t/\tau }}) Vout(t)=Vdβ11+βA0βA0(1−e−t/τ)

其中,VoutV_{out}Vout的终值为:

Vd1ββA01+βA0V_d \frac{1}{\beta} \frac{\beta A_0}{1 + \beta A_0} Vdβ11+βA0βA0

根据题目要求,5ns后,settling error小于1%,那么有:

e−t/τ∣t=5ns=e−tβA0ω0∣t=5ns<1%e^{ - t/\tau } |_{t = 5ns} = {{{e^{ - t\beta {A_0}{\omega _0}}}} |_{t = 5ns}} < 1 \% e−t/τ∣t=5ns=e−tβA0ω0∣t=5ns<1%

e−t/τ∣t=5nse^{ - t/\tau } |_{t = 5ns} e−t/τ∣t=5ns

解得:

GBW=A0ω0>9.21∗109(rad/s)≈1.47GHzGBW = {A_0}{\omega _0} > 9.21*{10^9}(rad/s) \approx 1.47GHz GBW=A0ω0>9.21∗109(rad/s)≈1.47GHz

而在单极点情况下我们有:

ωu≈A0ω0=GBW\omega _u \approx {A_0}{\omega _0} = GBW ωu≈A0ω0=GBW

上述计算说明了电路的速度取决于单位增益带宽 {\omega _u} 。

此外,我们还需要注意,Vout的终值并非等于目标的闭环增益大小,因此这里也贡献了误差。

8.1.2.3 大信号带宽

当阶跃响应是小信号时,输出电压变化是理想的指数变化,我们可以采用上述分析;而当阶跃的电压较大时,受到压摆率的影响,输出电压的变化会有一段线性的变化。

8.1.2.4 输出摆幅

定义:运放的有效电压输出范围。

摆幅有多种定义,一种严格的摆幅定义为运 放增益相对零输入时下降3dB(约30%)以内所对应的输出电压范围,即在输出摆幅范围内的电压时,运放的增益波动不超过3dB。

另一种相对宽松的定义是使得运放增益满足应用需求时的输出电压范围,这通常更符合实际使用。

对于商用运放,有时也会简单地定义摆幅为运放输岀一定电流时输出电压所能达到的最大范围。

当输出信号的大小超过输出摆幅,会导致输出端信号被“削平”。

通常我们不考虑输入端的摆幅,因为当增益较大时,输入两端的电压趋近于“虚短”,因此不容易超出输入范围。

8.1.2.5 线性度

输入幅度会显著地影响放大器的增益,导致放大器增益的线性度问题,而我们可以通过反馈来提高运放增益的线性度。详见下文中的2.4节:

8.1.2.6 失调 Offset

定义:当不施加差模信号,仅存在共模信号时,输出电压并不在理想的直流工作点,那么此时的输出电压与理想输出电压之差称为失调(差分对失配导致)。

我们常常将其等效到输入端上,得到:

VINF,os=Vout,os/A0{V_{INF,os}} = {V_{out,os}}/{A_0} VINF,os=Vout,os/A0

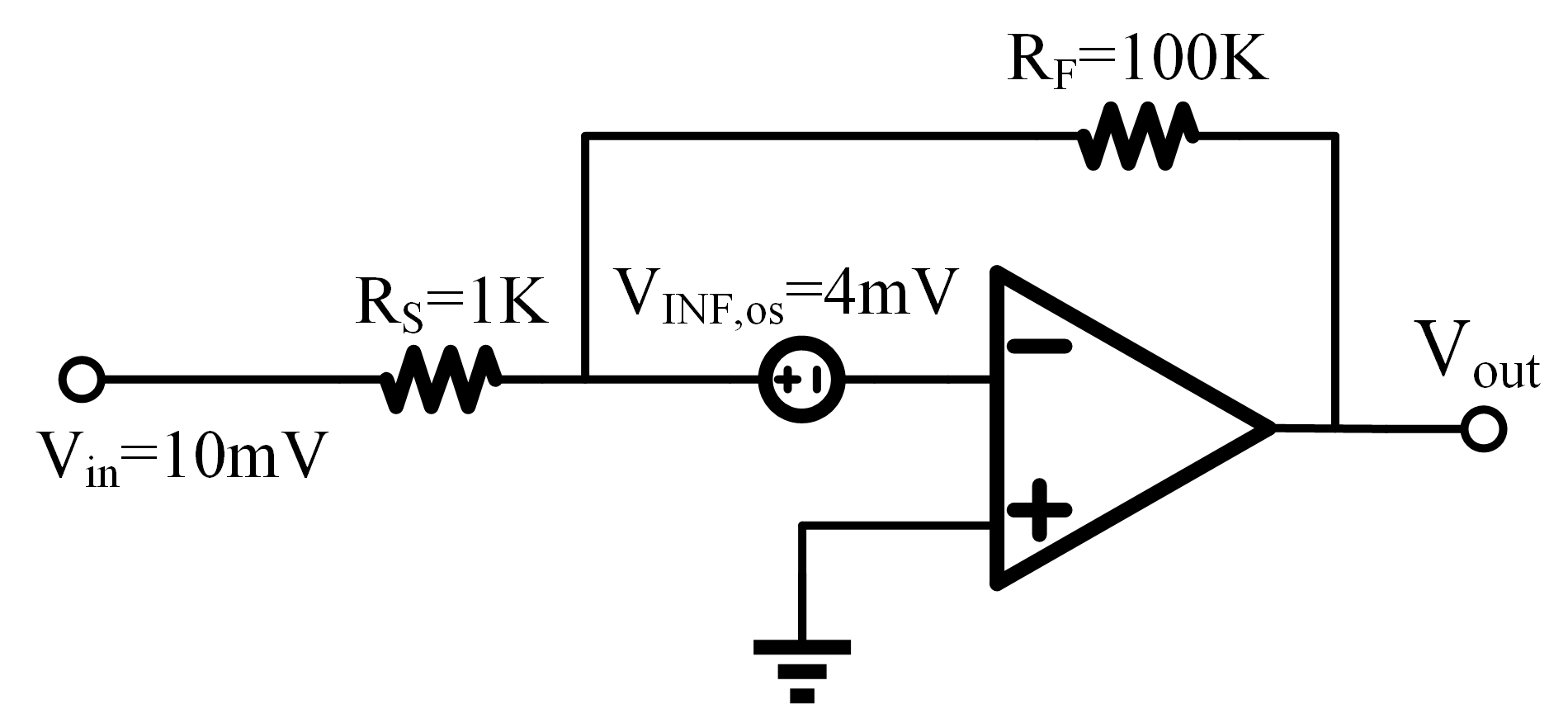

我们以下面这个电路为例说明:

若不考虑运放的失调,考虑到运放的虚短和虚断,理想的闭环增益为-100。

若考虑失调导致的 VINF,os{{V_{INF,os}}}VINF,os ,那么有:

Vout−VINF,osRF=VINF,os−VinRS\frac{{{V_{out}} - {V_{INF,os}}}}{{{R_F}}} = \frac{{{V_{INF,os}} - {V_{in}}}}{{{R_S}}} RFVout−VINF,os=RSVINF,os−Vin

解得 Vout=−596mV{V_{out}} = - 596mVVout=−596mV

实际上的失调没有那么大,这里为了说明问题取了一个较大的值。

可以看到,失调对闭环增益的影响非常大,这要求我们在设计运放时要尽量保证运放两边的匹配。

8.1.2.7 电源抑制与噪声

通常使用全差动的结构来降低电流源的扰动,但是这种结构会导致双倍的噪声功率。

详见:

https://zhuanlan.zhihu.com/p/937307533

以及噪声章节的4.7

https://zhuanlan.zhihu.com/p/2322788551

原文章来源

https://zhuanlan.zhihu.com/p/4103985611