时间数字转换器TDC的FPGA方案及核心代码

目录

简介

方案

方案项目:

简介

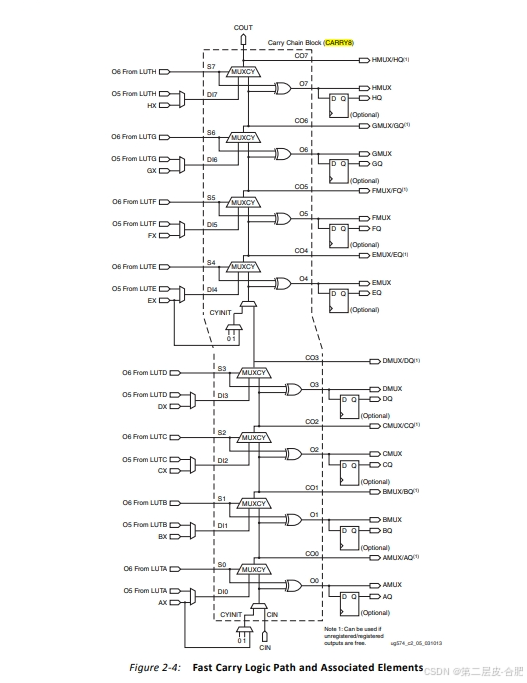

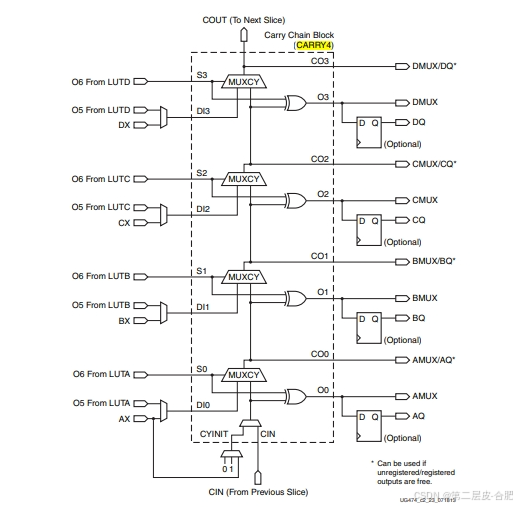

时间到数字转换器(TDC)是将时间间隔(TI)转换为数字代码的高精度时间传感器。它们被广泛应用于时间分辨应用,如粒子物理等。大多数F使用级联携带链来形成抽头延迟线(TDL),因为携带链是现代fpga中的标准链,并有专用的路由资源。

方案

本方案采用FPGA的延时链进行设计,重点采用FPGA的carry4(ultrascale 系列是carry8)

方案项目:

时间分辨率和时间线性度是任何基于FPGA的TDC设计中的关键问题。

分辨率(最小可检测的时间值,通常称