STM32-FSMC

TFT-LCD 是薄膜晶体管液晶显示器;TFT 液晶为每个像素都设有一个薄膜晶体管(TFT),

每个像素都可以通过点脉冲直接控制,因而每个节点都相对独立,并可以连续控

制,不仅提高了显示屏的反应速度,同时可以精确控制显示色阶,所以 TFT 液晶

的色彩更真,因此 TFT-LCD 也被叫做真彩液晶显示器。

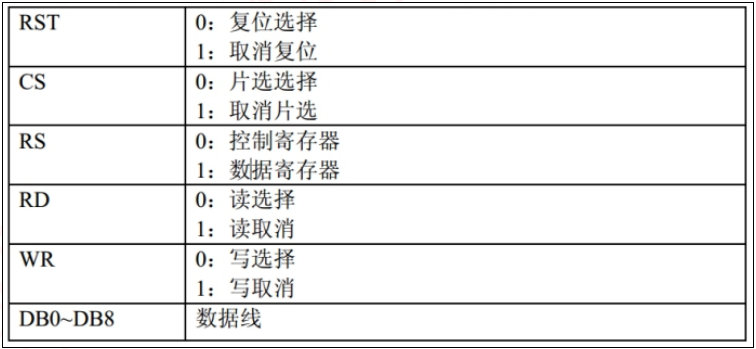

8080 接口有 5 条基本的控制线和多条数据线,数据线的数量主要看液晶屏使用的是几位模

式,有 8 根、9 根、16 根、18 根四种类型。

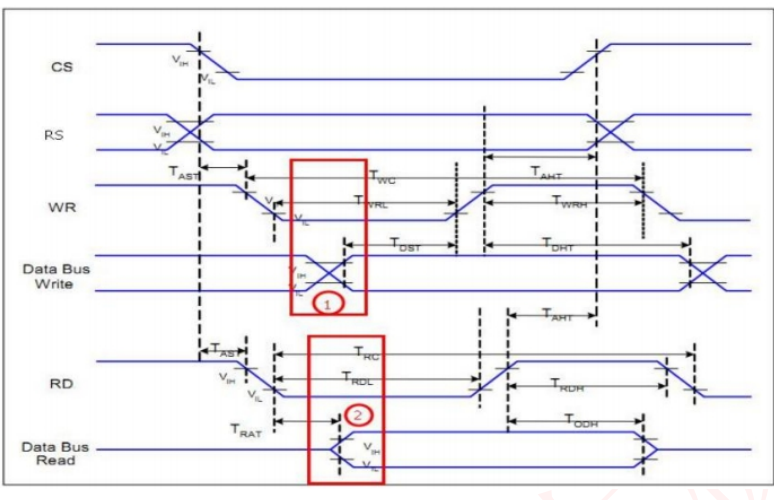

- 可以先在总线上面写入数据,然后在跳变 WR,以保证当读取的时候,总线上面的数据是稳定的。

- 在 RD 跳变为低电平之后,液晶屏放置数据到总线上面

- 设置 STM32F1 与 TFTLCD 模块相连接的 IO(这里我们用使用的是 STM32F1 的 FSMC)

- 初始化 TFTLCD 模块(写入一系列设置值)(首先复位,然后初始化-写入一系列的值)

- 将要显示的内容写到 TFTLCD 模块内(设置坐标→写 GRAM 指令→写 GRAM 来实现(这是点的实现))

FSMC 简介:灵活的静态存储控制器

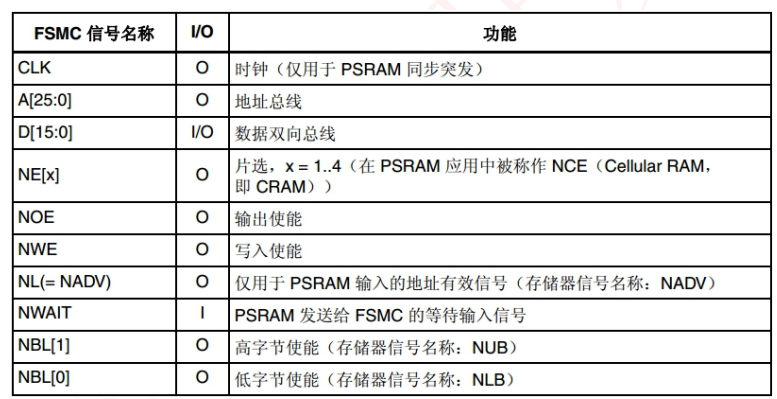

FSMC模块能够与同步或异步存储器和16位PC存储器卡接口,它的主要作用是:

● 将AHB传输信号转换到适当的外部设备协议

● 满足访问外部设备的时序要求

所有的外部存储器共享控制器输出的地址、数据和控制信号,每个外部设备可以通过一个唯一

的片选信号加以区分。FSMC在任一时刻只访问一个外部设备。将32位的AHB访问请求,转换到连续的16位或8位的,对外部16位或8位器件的访问

是 STM32 系列采用一种新型的存储器扩展技术,能够连接同步、异步存储器和 16 位 PC 存储卡。STM32 通过 FSMC 可以与 SRAM、ROM、PSRAM、NOR Flash 和 NANDFlash

等存储器的引脚直接相连。

SRAM 的核心优势是速度和稳定性-CPU 缓存

ROM:只读存储器-永久性存储介质,出厂时写入数据,断电后数据不丢失

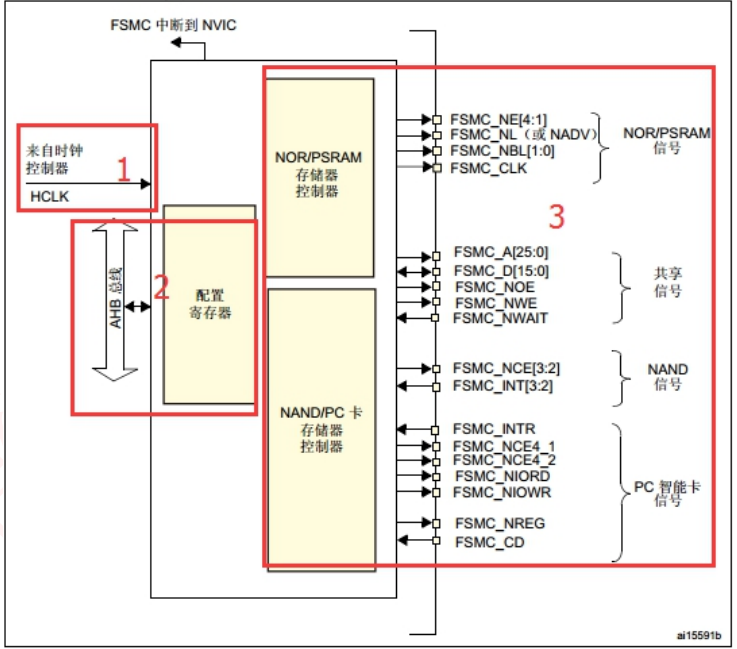

- 时钟输入:FSMC 的时钟来至时钟控制器 HCLK;使能 AHB总线时钟。

- AHB 接口:CPU 和其它 AHB 总线主设备可通过该 AHB 从设备接口访问外部静态存储器。

- FSMC 外部设备:NOR/PSRAM 设备、NAND/PC卡设备。有不同的CS可以区分

本章实验我们使用的是 FSMC 的 NOR/PSRAM 存储器控制器部分,即把 TFTLCD 当成 SRAM 设备使用。

在图中可以看出FSMC:外部 SRAM 的控制一般有:地址线(如 A0~A25)、双向 数据线(如 D0~D15)、写信号( NWE)、读信号( NOE)、片选信号(NE[x]), 如果 SRAM 支持字节控制,那么还有 UB/LB 信号。

TFTLCD 的信号包括: RS、DB0-DB15、 WR、 RD、 CS、 RST 等,TFTLCD 通过 RS 信号来决定传送的数据是数据还是命令;本质上可以理解 为一个地址信号,比如我们把 RS 接在 A0 上面,那么当 FSMC 控制器写地址 0的时候,会使得 A0 变为 0,对 TFTLCD 来说,就是写命令。

FSMC 写地址 1 的时候, A0 将会变为 1,对 TFTLCD 来说,就是写数据了。

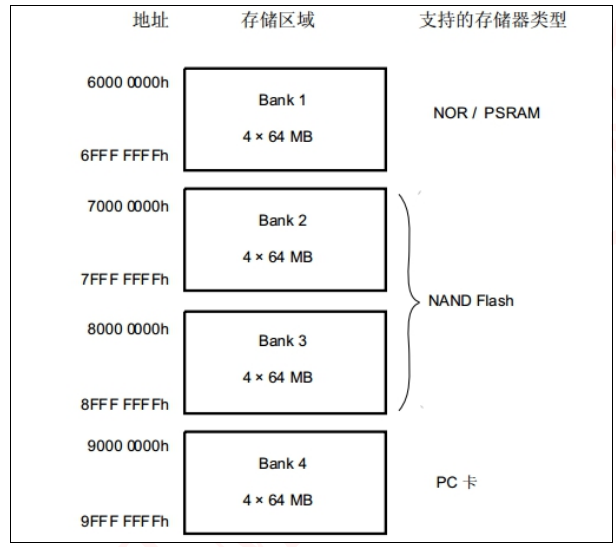

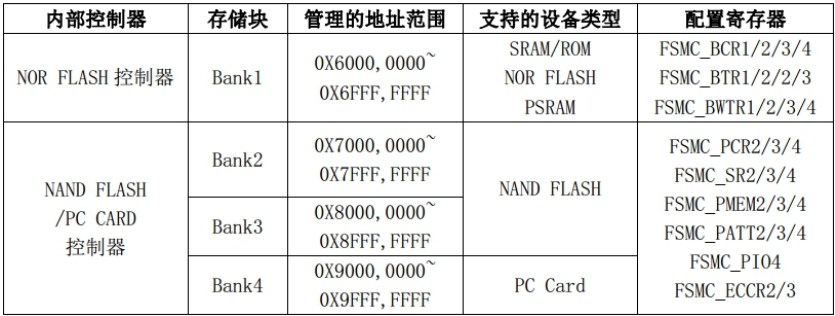

FSMC外部存储器被划分为 4 个固定大小的存储区域(Bank),每个存储区域的大小为 256 MB,共 1GB 空间。

存储区域 1 可连接多达 4 个 NOR Flash 或 PSRAM 存储器器件。此存储区 域被划分为 4 个 NOR/PSRAM 区域,带 4 个专用片选信号。存储区域 2 和 3 用 于连接 NAND Flash 器件(每个存储区域一个器件)。存储区域 4 用于连接 PC 卡设备。对于每个存储区域,所要使用的存储器类型由用户在配置寄存器中定义。

NOR FLASH 控制器,主要是通过 FSMC_BCRx、 FSMC_BTRx 和 FSMC_BWTRx 寄存器设置(其中 x=1~4,对应 4 个区)。通过这 3 个寄存器, 可以设置 FSMC 访问外部存储器的时序参数,

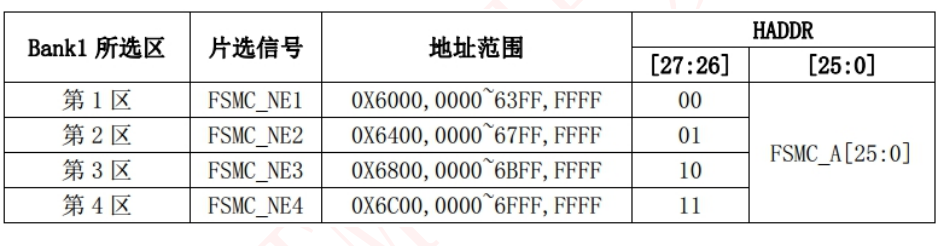

STM32F1 的 FSMC 存储块 1( Bank1)又被分为 4 个区,每个区管理 64M 字 节空间,每个区都有独立的寄存器对所连接的存储器进行配置。 Bank1 的 256M 字节空间由 28 根地址线(HADDR[27:0])寻址。这里 HADDR 是内部 AHB 地址 总 线,其 中 HADDR[25:0] 来自外部存储器地 址 FSMC_A[25:0],而 HADDR[26:27] 对 4 个区进行寻址

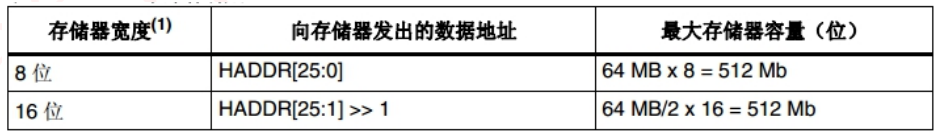

如果外部存储器的宽度为 8 位, FSMC 将使用内部的 HADDR[25:0] 地址来 作为对外部存储器的寻址地址 FSMC_A[25:0];如果外部存储器的宽度为 16 位, FSMC 将使用内部 的 HADDR[25:1] 地址来作为对外部存储器的寻址地址 FSMC_A[24:0],相当于右移了一位

后面我们设置 A10 地址的时候就要使用到。无论外部存储器的宽度 为 16 位还是 8 位FSMC_A[0] 都应连接到外部存储器地址 A[0]。HADDR[27:26]的设置,是不需要我们干预的,比如:当你选择使用Bank1 的第三个区,即使用 FSMC_NE3 来连接外部设备的时候,即对应了HADDR[27:26]=10,我们要做的就是配置对应第 3 区的寄存器组,来适应外部设备即可。

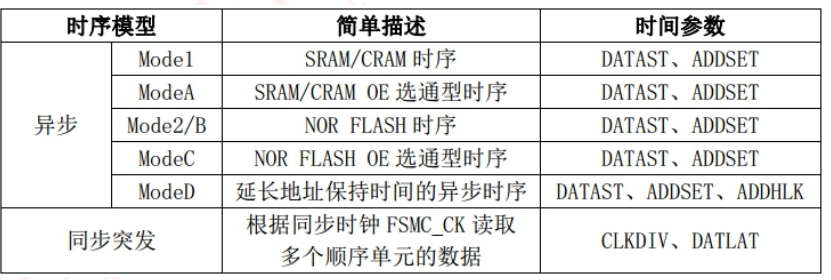

FSMC 的 NOR FLASH 控制器支持同步和异步突发两种访问方式(地址建立时间 (ADDSET)、数据建立时间(DATAST)和地址保持时间(ADDHLD))

采用模式A:支持独立的读写时序控制(由于TFTLCD读写时序不一样)

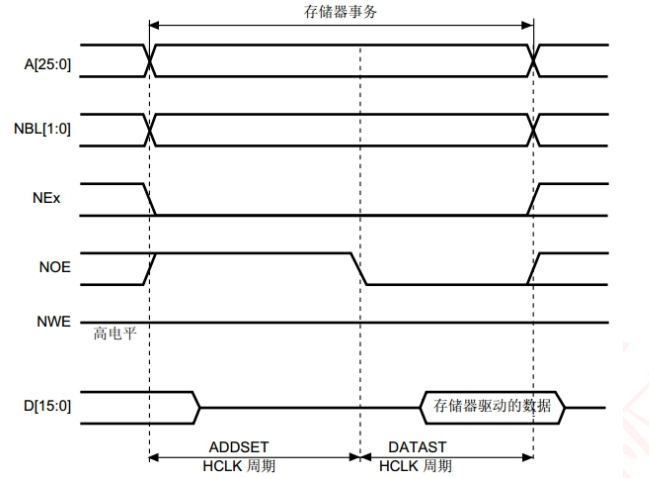

模式 A 的读 操作时序如下图所示:

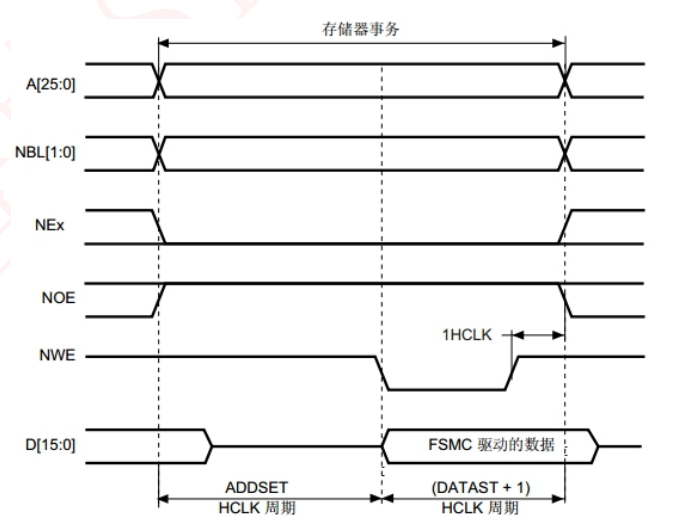

模式 A 的写操作时序如下图所示:

模式 A 读写时序中的 ADDSET 与 DATAST,是通过不同的寄存器设置的

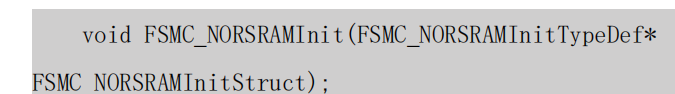

FSMC 的初始化主要是配置 FSMC_BCRx, FSMC_BTRx,FSMC_BWTRx 这三个寄

存器,下面三个初始化函数包含了对这三个寄存器的配置

FSMC_NORSRAMInit();

FSMC_NANDInit();

FSMC_PCCARDInit();

(1)FSMC 初始化

/*** @brief FSMC NOR/SRAM 接口初始化结构体* 用于配置STM32微控制器的灵活静态存储控制器(FSMC)中NOR闪存或SRAM的工作参数*/

typedef struct

{uint32_t FSMC_Bank; /* 选择要配置的FSMC存储区可选值:FSMC_Bank1_NORSRAM1~4(Bank1的4个NOR/SRAM子存储区 或FSMC_Bank2_NAND(NAND存储区2)等,根据具体芯片型号而定 */uint32_t FSMC_DataAddressMux; /* 地址/数据总线复用控制可选值:FSMC_DataAddressMux_Disable - 地址线和数据线分离(非复用模式) FSMC_DataAddressMux_Enable - 地址线和数据线复用(适用于部分存储设备) */uint32_t FSMC_MemoryType; /* 存储设备类型选择可选值:FSMC_MemoryType_SRAM - SRAM存储器FSMC_MemoryType_PSRAM - PSRAM存储器FSMC_MemoryType_NOR - NOR闪存 */uint32_t FSMC_MemoryDataWidth; /* 存储器数据宽度可选值:FSMC_MemoryDataWidth_8b - 8位数据宽度FSMC_MemoryDataWidth_16b - 16位数据宽度 */uint32_t FSMC_BurstAccessMode; /* 突发访问模式使能控制(仅适用于同步类型存储器)可选值:FSMC_BurstAccessMode_Disable - 禁用突发访问FSMC_BurstAccessMode_Enable - 使能突发访问 */uint32_t FSMC_AsynchronousWait; /* 异步等待信号使能(仅在异步模式下有效)可选值:FSMC_AsynchronousWait_Disable - 禁用异步等待FSMC_AsynchronousWait_Enable - 使能异步等待 */uint32_t FSMC_WaitSignalPolarity; /* 等待信号的极性设置可选值:FSMC_WaitSignalPolarity_Low - 等待信号低电平有效FSMC_WaitSignalPolarity_High - 等待信号高电平有效 */uint32_t FSMC_WrapMode; /* 突发模式下的自动换行功能(仅适用于同步类型存储器)可选值:FSMC_WrapMode_Disable - 禁用自动换行FSMC_WrapMode_Enable - 使能自动换行 */uint32_t FSMC_WaitSignalActive; /* 等待信号有效的时序阶段可选值:FSMC_WaitSignalActive_BeforeWaitState - 等待状态前有xiao FSMC_WaitSignalActive_DuringWaitState - 等待状态期间有效 */uint32_t FSMC_WriteOperation; /* 写操作使能控制可选值:FSMC_WriteOperation_Disable - 禁用写操作(只读模式)FSMC_WriteOperation_Enable - 使能写操作(可读可写) */uint32_t FSMC_WaitSignal; /* 等待信号使能控制(仅适用于同步模式)可选值:FSMC_WaitSignal_Disable - 禁用等待信号FSMC_WaitSignal_Enable - 使能等待信号 */uint32_t FSMC_ExtendedMode; /* 扩展模式使能(用于配置读写不同时序)可选值:FSMC_ExtendedMode_Disable - 禁用扩展模式(读写使用相同时序)FSMC_ExtendedMode_Enable - 使能扩展模式(读写使用不同时序) */uint32_t FSMC_WriteBurst; /* 写突发模式使能控制可选值:FSMC_WriteBurst_Disable - 禁用写突发FSMC_WriteBurst_Enable - 使能写突发 */FSMC_NORSRAMTimingInitTypeDef* FSMC_ReadWriteTimingStruct; /* 读写时序结构体指针(当扩展模式禁用时使用)指向包含地址建立时间、数据保持时间等时序参数的结构体 */FSMC_NORSRAMTimingInitTypeDef* FSMC_WriteTimingStruct; /* 写时序结构体指针(当扩展模式使能时使用)单独配置写操作的时序参数,读操作使用上面的读写时序结构体 */

} FSMC_NORSRAMInitTypeDef;FSMC_ReadWriteTimingStruct 和 FSMC_WriteTimingStruct:用于设置读 写时序。这两个变量都是 FSMC_NORSRAMTimingInitTypeDef 结构体指针类型。 这两个参数在初始化的时候分别用来初始化片选控制寄存器 FSMC_BTRx 和写操作时序控制寄存器 FSMC_BWTRx。

typedef struct{uint32_t FSMC_AddressSetupTime;//地址建立时间uint32_t FSMC_AddressHoldTime;//地址保持时间uint32_t FSMC_DataSetupTime;//数据建立时间uint32_t FSMC_BusTurnAroundDuration;//总线恢复时间uint32_t FSMC_CLKDivision;//时钟分频uint32_t FSMC_DataLatency;//数据保持时间uint32_t FSMC_AccessMode;//访问模式

}FSMC_NORSRAMTimingInitTypeDef;(2)使能(开启)FSMC

第一个参数用来选择存储器 的区域,第二个参数用来使能或者失能

void FSMC_NORSRAMCmd(uint32_t FSMC_Bank, FunctionalState NewState);

void FSMC_NANDCmd(uint32_t FSMC_Bank, FunctionalState NewState);

void FSMC_PCCARDCmd(FunctionalState NewState);