学习嵌入式-IMX6ULL学习——中断

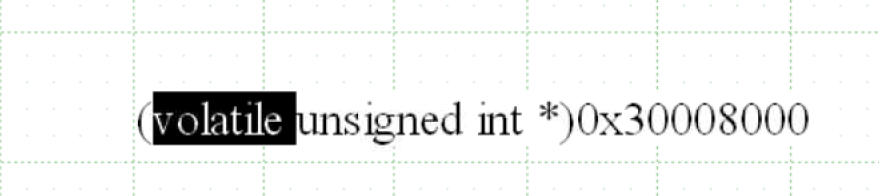

volatile:易变的,防止系统优化

对寄存器做处理的时候使用,在进行写1清零操作时,防止该操作被系统优化;

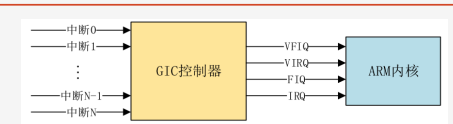

一、GIC通用中断控制器

1.GIC通用中断控制器

GIC接收众多外部中断,然后对其进行处理,最终通过VFIQ、VIRQ、FIQ 和 IRQ给内核;这四个 信号的含义如下: VFIQ:虚拟快速 FIQ。 VIRQ:虚拟 IRQ。 FIQ:快速中断 IRQ。 IRQ:中断 IRQ。

2,GIC中断分类:

- SPI(Shared Peripheral Interrupt),共享中断, (注意!不是 SPI 总线那个中断),这类中断泛指所有的 外设中断;

- PPI(Private Peripheral Interrupt),私有中断,我们说了 GIC 是支持多核的,每个核肯定有自己独有 的中断。这些独有的中断肯定是要指定的核心处理,因此这些中断就叫做私有中断;

- SGI(Software-generated Interrupt),软件中断,由软件触发引起的中断,通过向寄存器GICD_SGIR 写入数据来触发,系统会使用 SGI 中断来完成多核之间的通信。

中断优先级数字越小,优先级越高;

3,GIC组成

由分发器 (1个)、cPU接口(几核就几个);

(1)分发器:

- 全局中断使能控制;

- 控制每一个中断的使能或者关闭;

- 设置每个中断的优先级;

- 设置每个中断的目标处理器列表;

- 设置每个外部中断的触发模式:电平触发或边沿触发;

- 设置每个中 断属于组 0 还是组 1;

(2)CPU接口

- 使能或者关闭发送到 CPU Core 的中断请求信号;

- 应答中断;

- 通知中断处理完成;

- 设置优先级掩码,通过掩码来设 置哪些中断不需要上报给 CPU Core;

- 定义抢占策略;

- 当多个中断到来的时候,选择优先级最高的 中断通知给 CPU Core;

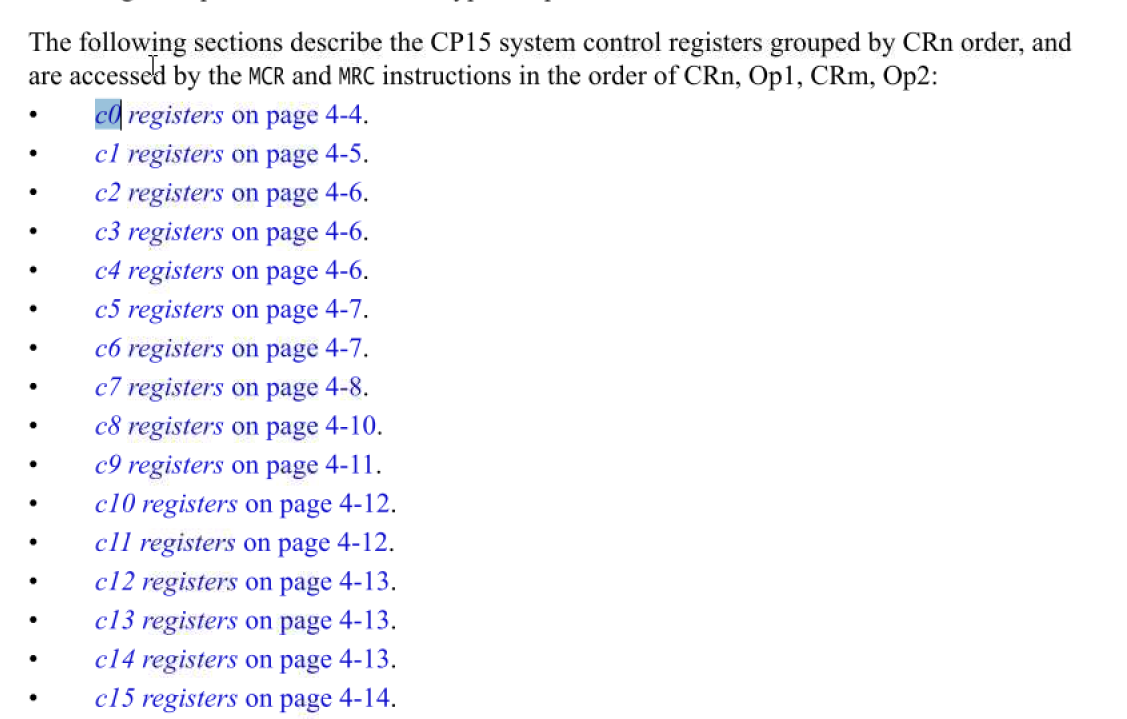

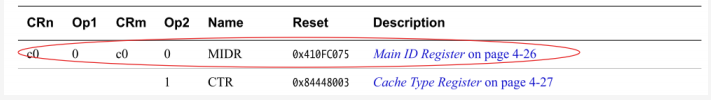

4.协处理器

(1)总共由16个,cp0~cp15;其中最常使用的cp15;

cp10,cp11:浮点型运算

5.cp15

(1)作用:

- 获取GIC的基地址(CBAR)

- MMU的配置(使能/禁用;SCTLR)

- cache的配置

- 监控系统性能

- 配置中断控制器(优先级、分组、使能/禁用,VBAR:设置中断向量表基地址)

- 访问寄存器(mrc读、mcr写)

- 获取或结束中断(IAR、EOIR)

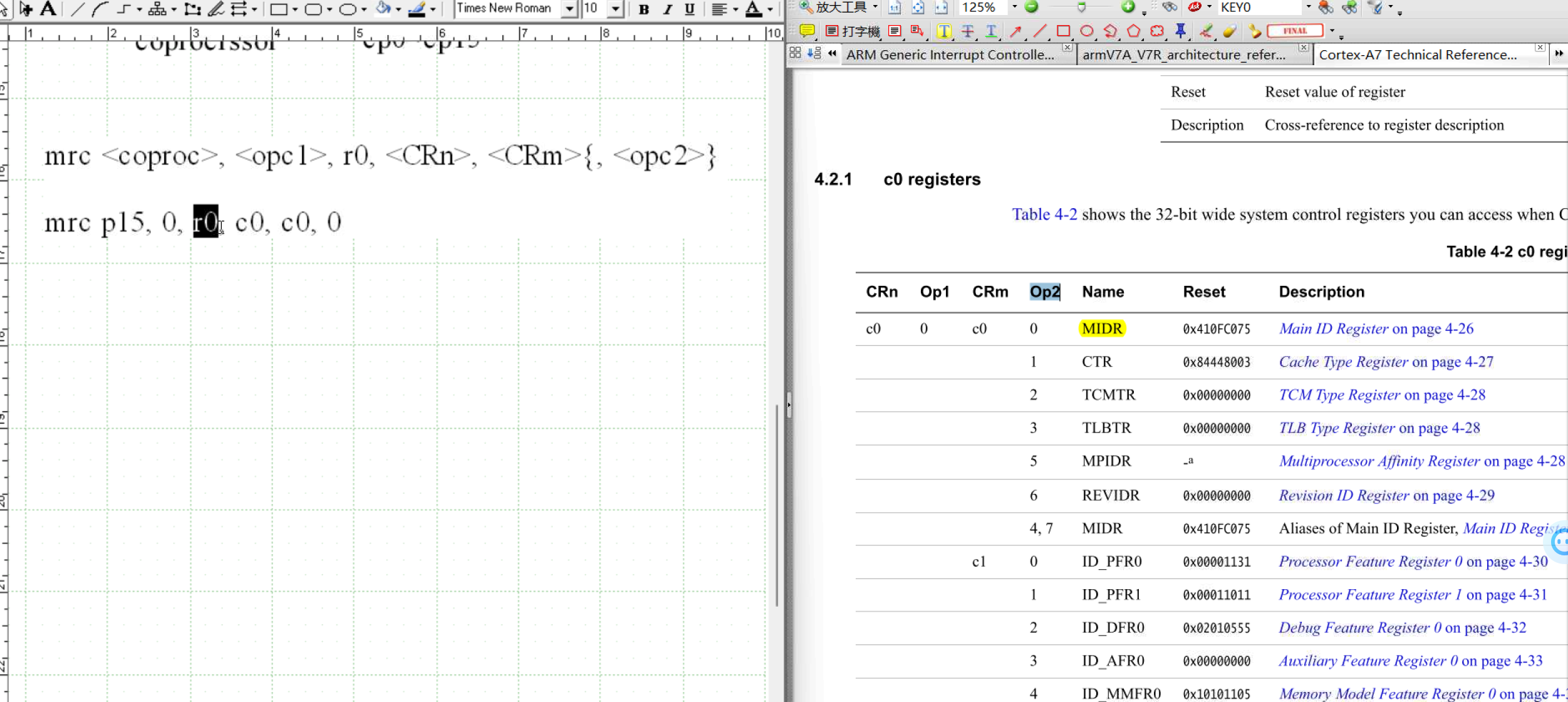

(2)mrc:将从cp15里面读出来放寄存器里面

MRC{cond} p15, <opc1>, <Rt>, <CRn>, <CRm>, <opc2>

mcr:把寄存器里面的东西往cp15里面写

MCR{cond} p15, <opc1>, <Rt>, <CRn>, <CRm>, <opc2>

简单总结一下,通过 MIDR 寄存器可以获取到处理器内核信息;通过 SCTLR 寄存器可以使能或禁止 MMU、I/D Cache 等;通过 VBAR 寄存器可以设置中断向量偏移;通过CBAR 寄存器可以获取 GIC 基地址。

二、外部中断

1.设置GIC

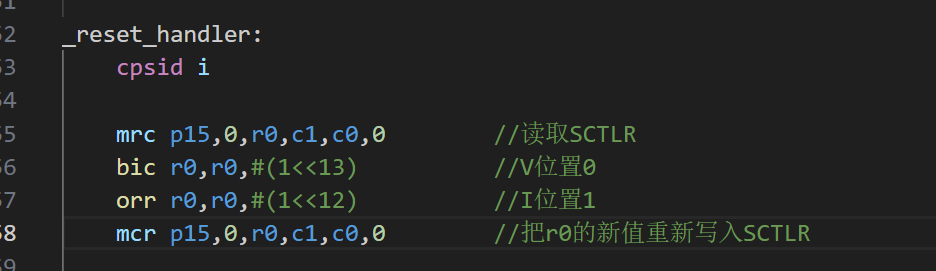

(1)读取SCTLR,将V位置0(软件可以通过 VBAR来重新映射这个基地址)I位置1(I cache使能)

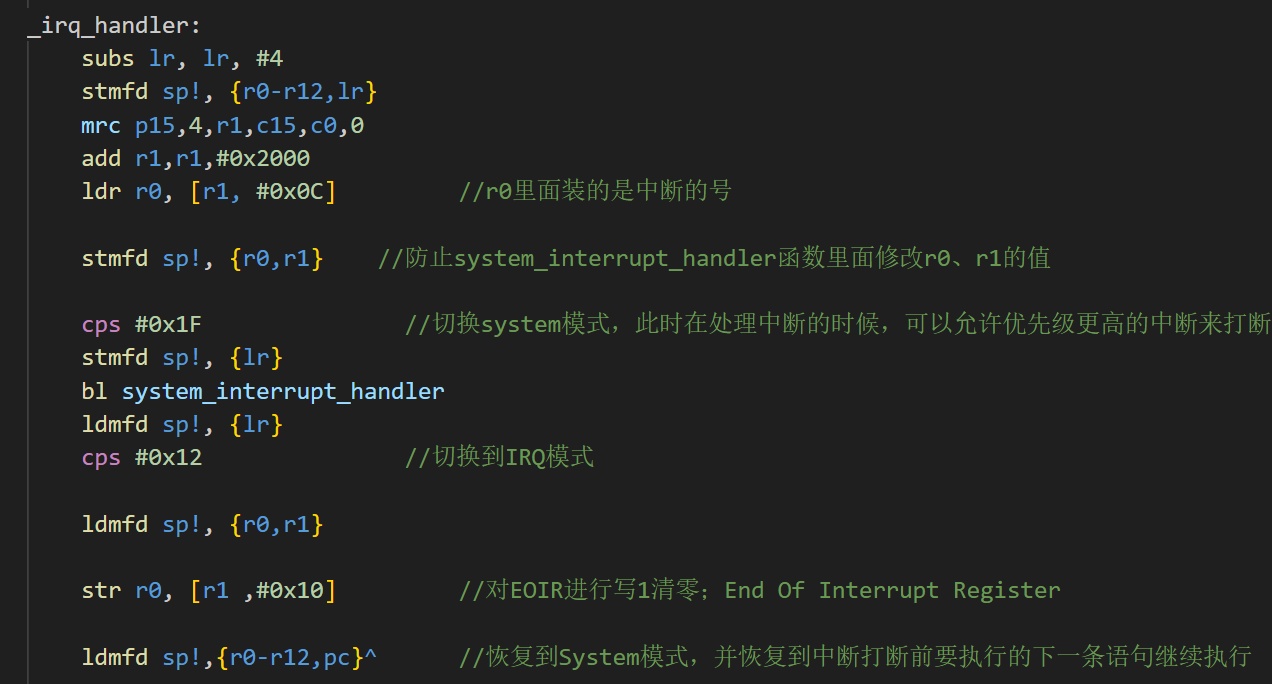

(2)通过GIC查询当前中断ID;先获取GIC基地址(CBAR);对其进行偏移(IAR),获得中断ID,然后进入中断处理函数

2.中断服务函数

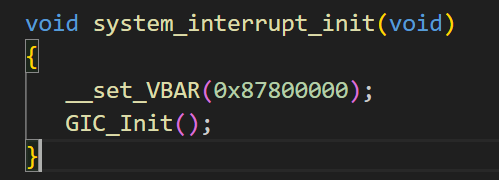

(1)中断初始化;重新定位异常向量表的位置到0x87800000;并且调用GIC_Init函数

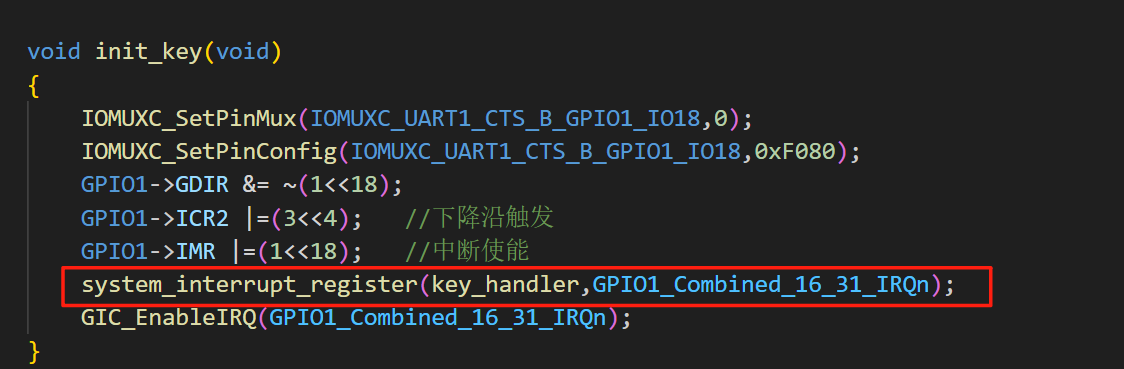

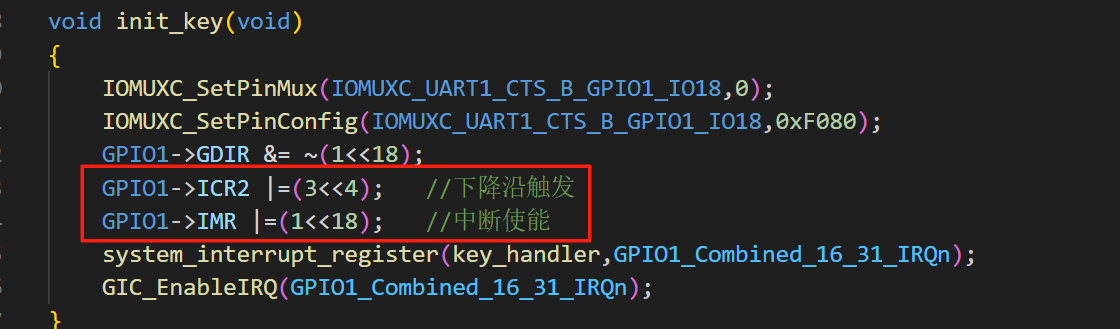

(2)对于GPIO1->ICR2(触发方式)、GPIO1->IMR(该中断使能)在中断源初始化进行配置

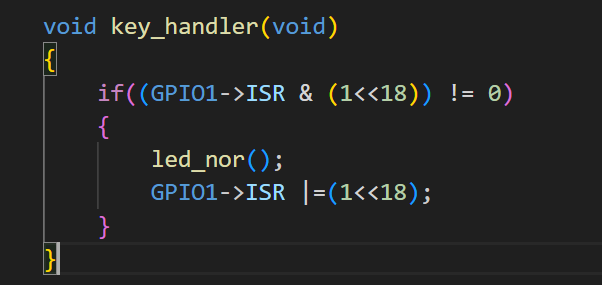

(4)中断服务函数

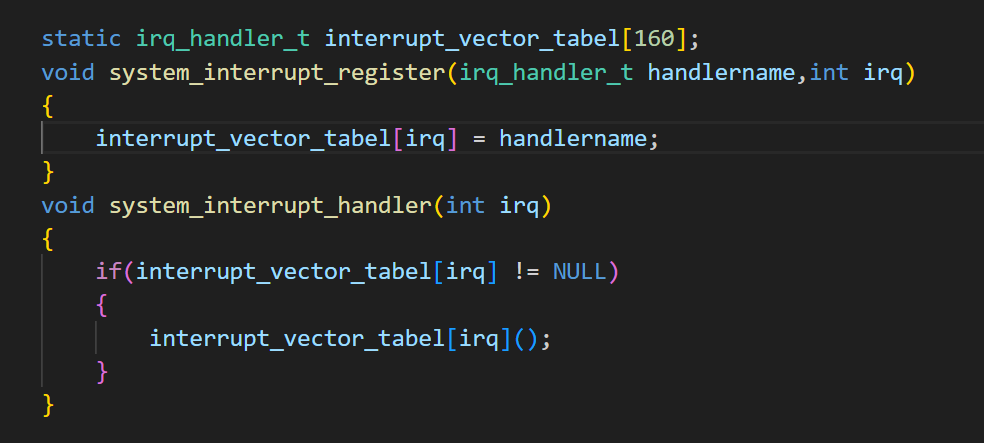

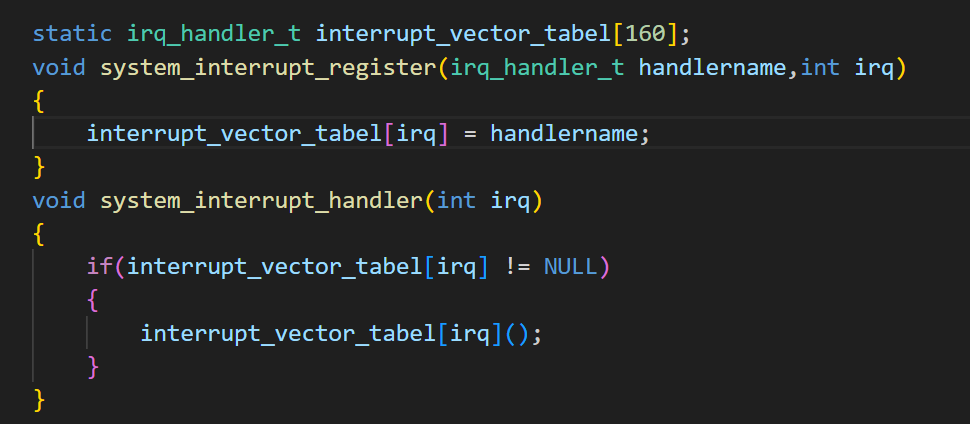

注意:先要在相对应的中断源的初始化函数里面注册在中断向量数组中;例子:注册完中断之后,中断发生就会调用中断服务函数

内敛函数:INLINE,定义被放在头文件中

三、OCP原则

1.OCP:开闭原则,对程序代码的添加是开放的,对程序的修改是关闭的

2.基于OCP原则对代码的修改

- 应用于中断服务函数的处理