LVDS系列24:Xilinx Ultrascale系ISERDESE3原语(二)

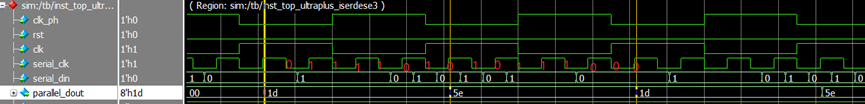

下面进行ISERDESE3原语的仿真验证:

DDR模式8bit,不使用FIFO:

由于iserdese3不带有bitslip功能,所以得到的数据可能需要bit拼接一下才能判断;

从上一讲的上图中,可以看到,原语将先进来的比特数据放到了并行输出的低位;

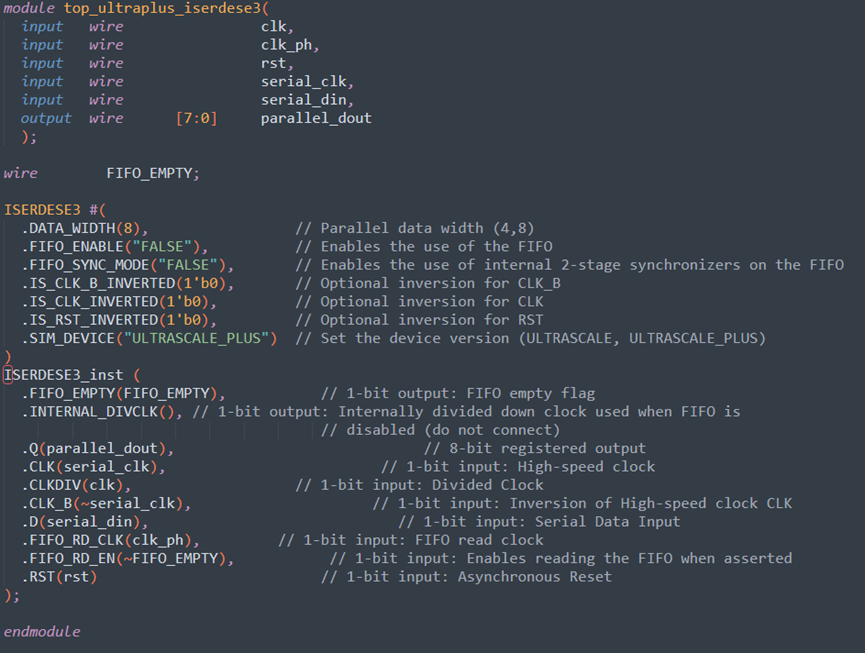

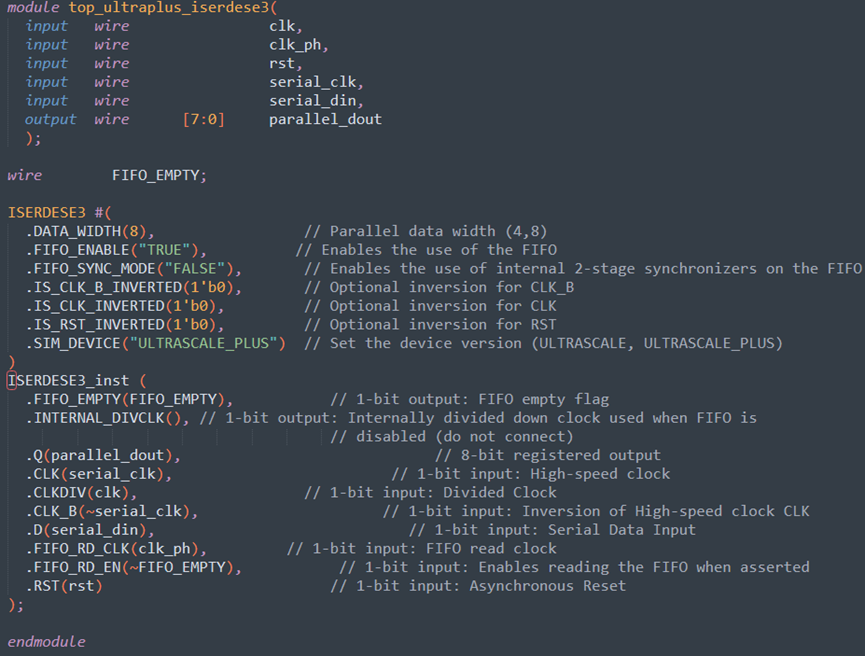

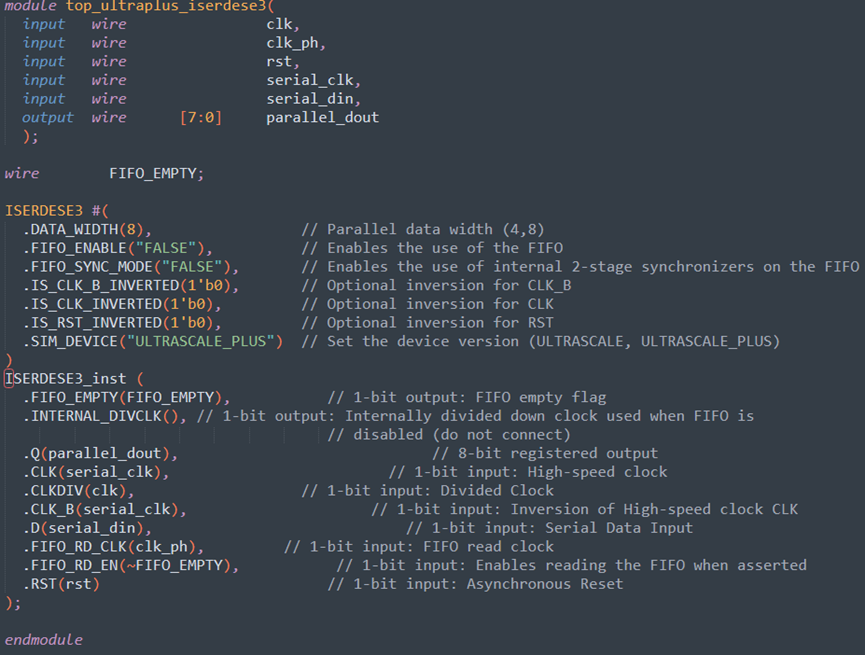

测试模块:

Tb中产生循环的8’hc3和8’hab,这里用低位先发的方法转成串行,

产生这一串数据顺序大概如下:

11010101 11000011

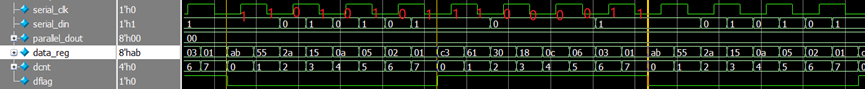

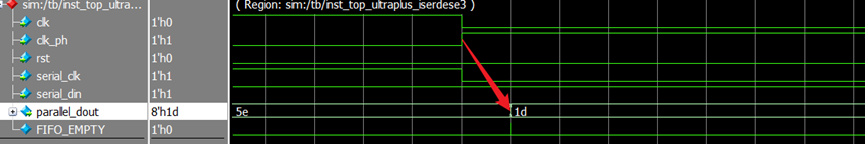

解串情况:

可以看到解出数据为1d和5e,

由于没有bitslip功能,我们自己对照下输入输出,

理想的数据输入序列是如下:

11010101 11000011 11010101 11000011 11010101 11000011…

但是图上进行解串的数据划分确是:

11010101 11000011 11010101 11000011 11010101 11000011…

其中红色绿色序列相同,且按该划分重复解串,

0111 1010,左侧为低位,组成8’h5E,

1011 1000,左侧为低位,组成8’h1D,与解串结果一致,

若想要得到预设的tb数据,则需要在获得解串结果后,再编写一层比特滑动的逻辑进行结果的变换,才能得到预设的结果。

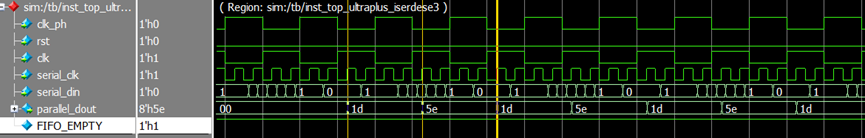

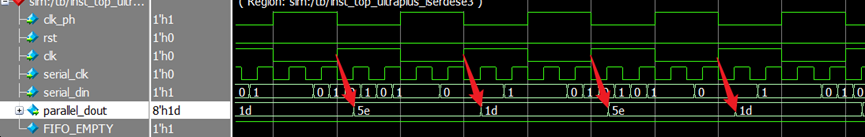

DDR模式8bit,使用FIFO:

修改测试模块中使用FIFO读取数据,

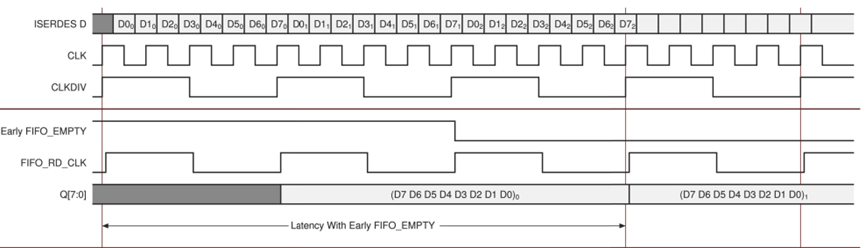

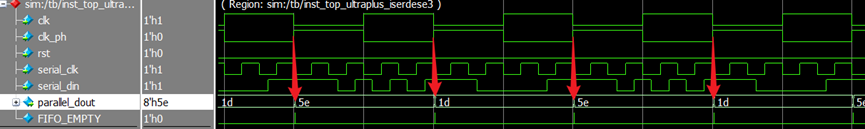

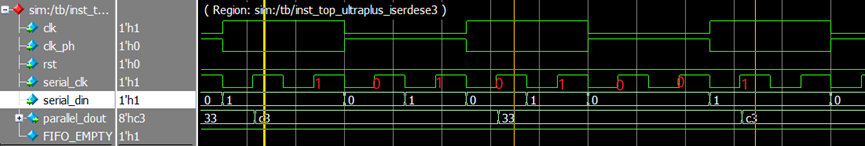

下图为不使用FIFO时,数据输出时间,可以看到是在CLK_DIV上升沿后一段时间输出

下图为使用FIFO时,输出数据都一致,数据输出时间,可以看到是在FIFO_RD_CLK上升沿后一小段时间输出,FIFO_RD_CLK这里使用一个与CLK_DIV不同相的时钟,

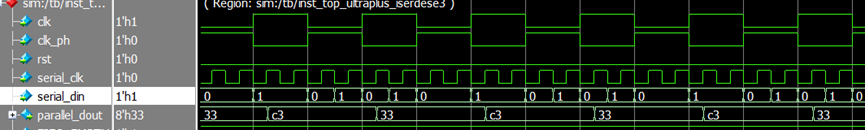

SDR模式4bit,不使用FIFO:

测试模块修改如下,CLK和CLK_B连接到同一高速时钟,

此时两个时钟相位对齐,彼此上升沿采集时,采集的数据相同,此时组成的8bit输出数据里,只有一半有效值,使用Q6、Q4、Q2、Q0即可;

Tb生成的数据是交替的4’ha和4’hc,低位先发,产生的数据流是:

00110101 00110101 00110101…

此时得到的解串数据是8’h 33和8’h c3,其中8’h 33是8’b00110011,8’h c3是8’b11000011,可以看到Q6、Q4、Q2、Q0和Q7、Q5、Q3、Q1的值分别相等,这是由于CLK和CLK_B相同,两者同时采一个值,所以解串得到的数据是4’b0101和4’b1001

上图为仿真解串的序列:

1010 1001 1010 1001…

在预设数据流中所处位置为 00110101 00110101 00110101 00110101…

左侧先到比特为低位,则解串数据为4’b0101和4’b1001,符合时序要求;

本文章由威三学社出品

对课程感兴趣可以私信联系