赛灵思ZYNQ官方文档UG585自学翻译笔记:General Purpose I/O (GPIO)通用输入 / 输出

该文档主要围绕 Zynq-7000 AP SoC 的通用目的 I/O(GPIO)展开,内容如下:

1. 概述

- GPIO 外设通过 MIO 模块提供对多达 54 个设备引脚的观测和控制,还通过 EMIO 接口提供与可编程逻辑(PL)间的 192 个 GPIO 信号(64 个输入、128 个输出)。

- GPIO 按寄存器组分为四个 bank,控制不同范围的 MIO 和 EMIO 信号,由软件通过一系列内存映射寄存器控制。

2. 关键特性

- 54 个用于设备引脚的 GPIO 信号(通过 MIO 多路复用器路由),输出支持三态。

- 192 个 PS 与 PL 间的 EMIO GPIO 信号,包括 64 个输入和 128 个输出(64 个真实输出和 64 个输出使能)。

- 每个 GPIO 可独立动态编程为输入、输出或中断感应模式。

- 支持可编程中断,可选择电平敏感(高 / 低)或边沿敏感(上升沿、下降沿、双边沿),能读取原始和屏蔽的中断状态。

3. 框图与 bank 划分

- Bank0:32 位,控制 MIO 引脚 [31:0]。

- Bank1:22 位,控制 MIO 引脚 [53:32](因 MIO 共 54 个引脚,故 Bank1 限制为 22 位)。

- Bank2:32 位,控制 EMIO 信号 [31:0]。

- Bank3:32 位,控制 EMIO 信号 [63:32]。

4. 注意事项

- 7z007s 和 7z010 CLG225 器件的可用 MIO 引脚减至 32 个,仅特定引脚可作为 GPIO,其他 MIO 引脚未连接。

- MIO 的 Bank0 和 Bank1 通过 MIO 模块路由到设备引脚,需通过 slcr.MIO_PIN_xx 寄存器选择合适的 I/O 类型、使能 GPIO 模块等,TRI_ENABLE 应设为 0 以让 GPIO 控制三态模式。

5. 功能描述

- MIO 引脚的 GPIO 控制:软件配置 GPIO 为输入或输出,DATA_RO 寄存器始终返回 GPIO 引脚状态,DATA 寄存器控制输出值,MASK_DATA_LSW 和 MASK_DATA_MSW 寄存器支持选择性更改输出值,DIRM 控制方向,OEN 控制输出使能。

- EMIO 信号:寄存器接口与 MIO 银行相同,但 EMIO 是 PS 与 PL 间的连线,输入与输出值和 OEN 寄存器无关,输出无三态功能,输出使能线由 DIRM 和 OEN 寄存器控制。

- Bank0 的 Bits [8:7]:对应控制 I/O 缓冲区电压模式的引脚,不能作为通用输入,可作为通用输出(复位时输出驱动禁用)。

- 中断功能:中断检测逻辑监控 GPIO 输入信号,触发方式可配置,中断状态存于 INT_STAT,通过 INT_EN 和 INT_DIS 控制中断屏蔽,所有 GPIO 共享 IRQ ID#52 中断。

6. 编程指南

- 启动序列:包括复位、时钟、GPIO 引脚配置、向输出引脚写数据、从输入引脚读数据、设置 GPIO 引脚为唤醒事件。

- GPIO 引脚配置:可将引脚配置为输入或输出,Bank0 的 [8:7] 引脚必须配置为输出。

- 向输出引脚写数据:可通过 DATA 寄存器(读 - 修改 - 更新)或 MASK_DATA_x_MSW/LSW 寄存器(选择性更新)。

- 从输入引脚读数据:可使用 DATA_RO_x 寄存器或中断逻辑。

- GPIO 作为唤醒事件:需在 GIC 中启用 GPIO 中断,启用特定引脚的 GPIO 中断,且不关闭任何 GPIO 相关时钟。

7. 寄存器概览

- 数据读写相关:MASK_DATA_{3:0}{MSW,LSW}、DATA{3:0}、DATA_{3:0}_RO。

- I/O 缓冲区控制相关:DIRM_{3:0}、OEN_{3:0}。

- 中断控制相关:INT_MASK_{3:0}、INT_EN_{3:0}、INT_DIS_{3:0}、INT_STAT_{3:0}、INT_TYPE_{3:0}、INT_POLARITY_{3:0}、INT_ANY_{3:0}。

8. 系统功能

- 时钟:由 APB 接口的 CPU_1x 时钟驱动,可通过 slcr.APER_CLK_CTRL [GPIO_CPU_1XCLKACT] 进行时钟门控实现电源管理。

- 复位:由 slcr.GPIO_RST_CTRL [GPIO_CPU1X_RST] 位复位,仅影响总线接口。

- 中断:所有 GPIO 控制器产生的中断路由到 IRQ 52。

9. I/O 接口

- MIO 编程:Bank0 和 Bank1 引脚通过 MIO 路由,可通过 slcr.MIO_PIN_XX 寄存器配置为 GPIO,需正确设置相关参数。

第 14 章 通用输入 / 输出(GPIO)

14.1 简介

通用输入 / 输出(GPIO)外设通过 MIO 模块为软件提供对多达 54 个设备引脚的观测和控制功能。它还通过 EMIO 接口提供来自可编程逻辑(PL)的 64 个输入和到 PL 的 128 个输出的访问。GPIO 分为四个寄存器组,每组对相关的接口信号进行分组管理1。

每个 GPIO 可独立且动态地编程为输入、输出或中断感应模式。软件可使用单条加载指令读取一个组内的所有 GPIO 值,或使用单条存储指令向一个或多个 GPIO(在 GPIO 的一定范围内)写入数据。GPIO 控制和状态寄存器的内存映射基地址为 0xE000_A0002。

14.1.1 特性

GPIO 外设的主要特性总结如下:

- 54 个用于设备引脚的 GPIO 信号(通过 MIO 多路复用器路由)

- 输出支持三态

- 通过 EMIO 接口在 PS 和 PL 之间有 192 个 GPIO 信号

- 64 个输入、128 个输出(64 个真实输出和 64 个输出使能)

- 每个 GPIO 的功能可单独或成组动态编程

- 使能、位或组数据写入、输出使能和方向控制

- 可在单个 GPIO 基础上进行可编程中断

- 可读取原始和屏蔽中断的状态

- 可选择的灵敏度:电平敏感(高或低)或边沿敏感(上升沿、下降沿或两者皆有)3至4

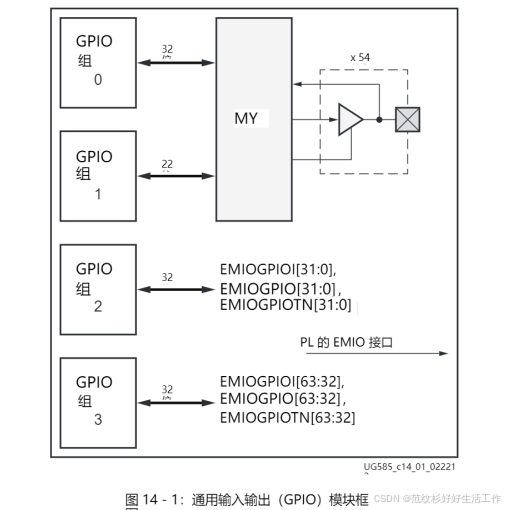

14.1.2 框图

如图 14-1 所示,GPIO 模块分为四个组:

- Bank0:32 位组,控制 MIO 引脚 [31:0]

- Bank1:22 位组,控制 MIO 引脚 [53:32]

- Bank2:32 位组,控制 EMIO 信号 [31:0]

- Bank3:32 位组,控制 EMIO 信号 [63:32]

注:由于 MIO 总共有 54 个引脚,因此 Bank1 限制为 22 位。

GPIO 通过一系列内存映射寄存器由软件控制。每个组的控制方式相同,但由于 MIO 组和 EMIO 组的功能不同,两者之间存在细微差异5至6。

14.1.3 注意事项

7z007s 和 7z010 CLG225 器件

7z007s 单核和 7z010 双核 CLG225 器件将可用的 MIO 引脚减少到 32 个,如 2.5.4 节 “MIO 一览表格” 中的 MIO 表所示。因此,在这些器件中,仅 15:0、39:28、48、49、52 和 53 号 MIO 引脚可作为 GPIO 引脚使用。其他 MIO 引脚未连接,不应使用。所有 EMIO 信号均可使用7至8。

MIO 注意事项

GPIO 外设模块的 Bank0 和 Bank1 通过 MIO 模块路由到设备引脚。有关 MIO 操作的完整描述,请参阅 2.5 节 “PS-PL MIO-EMIO 信号和接口”。MIO 的主要控制通过 slcr.MIO_PIN_xx 寄存器实现。请注意以下几点:

- 用户必须根据自身系统,使用 IO_Type、PULLUP、DisableRcvr 和 Speed 字段选择合适的 I/O 类型。

- 用户必须通过多路复用器控制字段 L0_SEL、L1_SEL、L2_SEL 和 L3_SEL 选择 GPIO 模块。请注意,每个 I/O 引脚可单独选择。当 MIO 引脚用于 IOP 设备时,它不能作为 GPIO 使用。

- TRI_ENABLE 应设置为 0。这使 GPIO 能够控制 I/O 的三态模式。如果 MIO 中的 TRI_ENABLE 设置为 1,则无论 GPIO 设置如何,输出驱动器都将处于三态9至10。

14.2 功能描述

14.2.1 设备引脚的 GPIO 控制

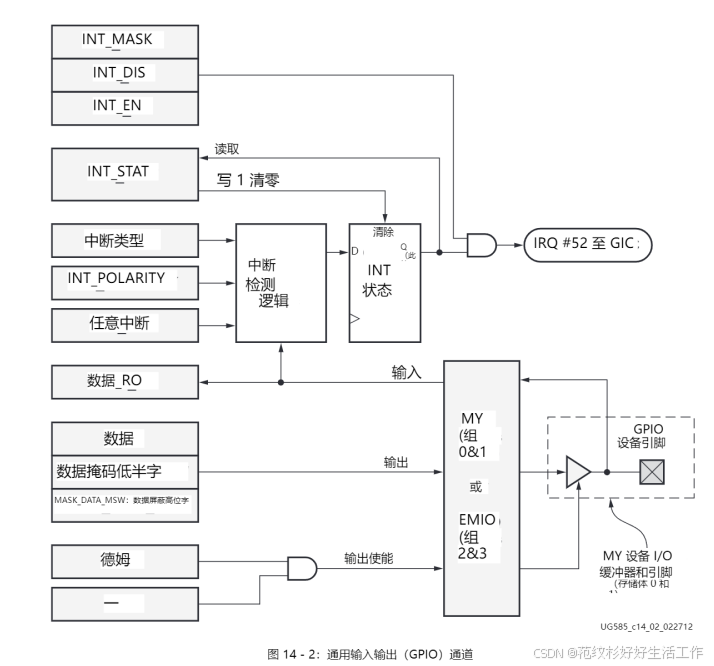

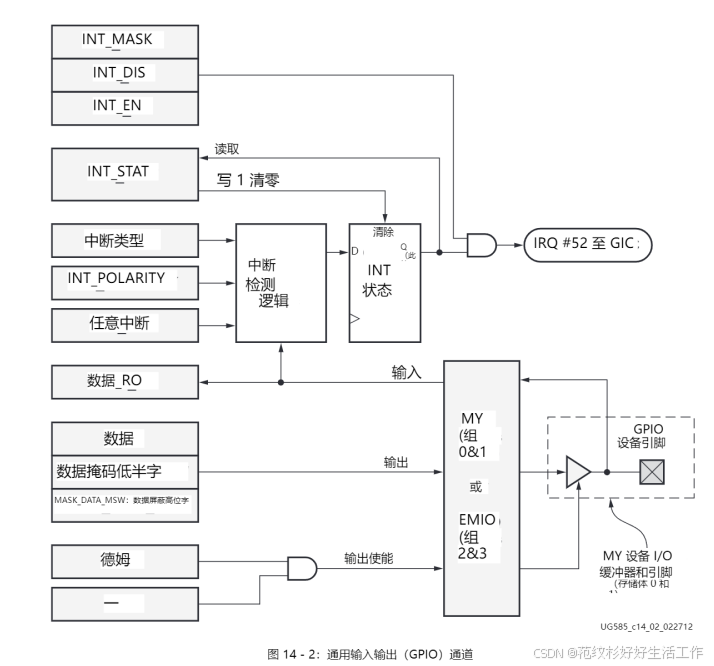

本节描述 Bank0 和 Bank1 的操作(见图 14-2)11。

软件将 GPIO 配置为输出或输入。无论 GPIO 设置为输入(OE 信号为假)还是输出(OE 信号为真),DATA_RO 寄存器始终返回 GPIO 引脚的状态。要生成输出波形,软件需反复向一个或多个 GPIO 写入数据(通常使用 MASK_DATA 寄存器)12。

应用可能需要同时切换多个 GPIO(两个 I/O 缓冲区之间的固有偏斜时间较小)。在这种情况下,所有需要同时切换的 GPIO 必须来自同一个 16 位半组(即最高有效 16 位或最低有效 16 位)的 GPIO,以便 MASK_DATA 寄存器能在一条存储指令中向它们写入数据13。

GPIO 组控制(针对 Bank0 和 Bank1)总结如下:

- DATA_RO:该寄存器使软件能够观测设备引脚上的值。如果 GPIO 信号配置为输出,则该寄存器通常会反映输出上驱动的值。向该寄存器写入数据将被忽略。

注:如果 MIO 未配置为启用该引脚作为 GPIO 引脚,则 DATA_RO 是不可预测的,因为软件无法通过 GPIO 寄存器观测非 GPIO 引脚上的值14至15。 - DATA:当 GPIO 信号配置为输出时,该寄存器控制要输出的值。该寄存器的所有 32 位将同时写入。从该寄存器读取将返回之前写入 DATA 或 MASK_DATA_{LSW,MSW} 的值;它不会返回设备引脚上的当前值16。

- MASK_DATA_LSW:该寄存器能够更有选择性地更改所需的输出值。最多可写入 16 位的任意组合。未写入的位将保持不变,保留其先前的值。从该寄存器读取将返回之前写入 DATA 或 MASK_DATA_{LSW,MSW} 的值;它不会返回设备引脚上的当前值。该寄存器避免了对未更改的位进行读 - 修改 - 写操作的需求17。

- MASK_DATA_MSW:该寄存器与 MASK_DATA_LSW 相同,但它控制组的高 16 位18。

- DIRM(方向模式):这控制 I/O 引脚是作为输入还是输出。由于输入逻辑始终启用,这实际上是启用 / 禁用输出驱动器。当 DIRM [x]==0 时,输出驱动器禁用19。

- OEN(输出使能):当 I/O 配置为输出时,这控制输出是否启用。当输出禁用时,引脚处于三态。当 OEN [x]==0 时,输出驱动器禁用20。

注:如果 MIO TRI_ENABLE 设置为 1,启用三态并禁用驱动器,则 OEN 将被忽略,输出处于三态21。

14.2.2 EMIO 信号

本节描述 Bank2 和 Bank3 的操作(见图 14-2)22。

EMIO 组的寄存器接口与上一节中描述的 MIO 组相同。然而,EMIO 接口只是 PS 和 PL 之间的连线,因此存在一些差异:

- 输入是来自 PL 的连线,与输出值或 OEN 寄存器无关。当 DIRM 设置为 0(使其成为输入)时,可从 DATA_RO 寄存器读取它们。

- 输出连线不支持三态,因此它们不受 OEN 的影响。要输出的值使用 DATA、MASK_DATA_LSW 和 MASK_DATA_MSW 寄存器进行编程。DIRM 必须设置为 1(使其成为输出)。

- 输出使能连线只是来自 PS 的输出。它们由 DIRM/OEN 寄存器控制,如下所示:EMIOGPIOTN [x] = DIRM [x] & OEN [x]

- EMIO I/O 与 MIO I/O 没有任何连接。EMIO 输入不能连接到 MIO 输出,MIO 输入也不能连接到 EMIO 输出。每个组都是独立的,只能用作软件可观测 / 控制的信号23至24。

14.2.3 Bank0 的位 [8:7] 为输出

Bank0 的 GPIO 位 [8:7] 对应于在复位期间用于控制 I/O 缓冲区自身电压模式的封装引脚。这些引脚称为 MIO 组的 VMODE 引脚带(参见 “引导模式引脚设置” 部分,第 165 页)。它们必须由外部系统根据适当的电压模式驱动。为防止它们被其他系统逻辑驱动,它们不能用作通用输入25至26。

由于复位时输出驱动器禁用,这些位可用作通用输出。系统在系统引导期间读取电压模式后,可以开始将这些位用作输出27。

14.2.4 中断功能

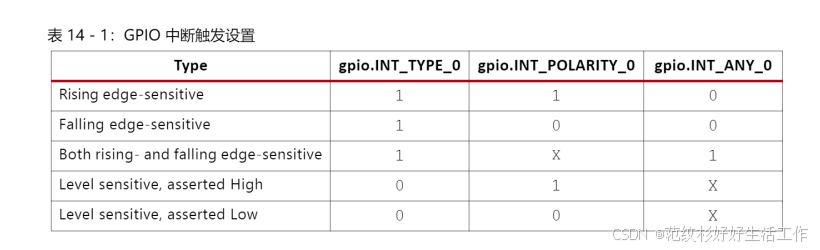

中断检测逻辑监控 GPIO 输入信号。中断触发可以是上升沿、下降沿、任一沿、低电平或高电平。触发灵敏度通过 INT_TYPE、INT_POLARITY 和 INT_ANY 寄存器进行编程28。

如果检测到中断,中断检测逻辑会将 GPIO 的 INT_STAT 状态设置为真。如果 INT_STAT 状态被启用(未屏蔽),则中断会传播到一个大型 OR 函数。该函数将所有四个组中所有 GPIO 的所有中断组合为一个输出(IRQ ID#52)到中断控制器。如果中断被禁用(屏蔽),则 INT_STAT 状态会保持到被清除,但除非 INT_EN 随后被写入以禁用屏蔽,否则它不会传播到中断控制器。由于所有 GPIO 共享同一个中断,软件必须同时考虑 INT_MASK 和 INT_STAT 来确定哪个 GPIO 引起了中断29。

中断屏蔽状态通过向 INT_EN 和 INT_DIS 寄存器写入 1 来控制。向 INT_EN 寄存器写入 1 会禁用屏蔽,允许活动中断传播到中断控制器。向 INT_DIS 寄存器写入 1 会启用屏蔽。可使用 INT_MASK 寄存器读取中断屏蔽的状态30。

如果 GPIO 中断是边沿敏感的,则检测逻辑会锁存 INT 状态。通过向 INT_STAT 寄存器写入 1 来清除 INT 锁存。对于电平敏感的中断,必须清除到 GPIO 的中断输入源才能清除中断信号。或者,软件可以使用 INT_DIS 寄存器屏蔽该输入31。

可以通过读取 INT_STAT 和 INT_MASK 寄存器来推断发送到中断控制器的中断信号的状态。如果 INT_STAT=1 且 INT_MASK=0,则该中断信号被断言32。

GPIO 组控制总结如下:

- INT_MASK:该寄存器为只读,显示当前哪些位被屏蔽以及哪些位未被屏蔽 / 启用。

- INT_EN:向该寄存器的任何位写入 1 会启用 / 取消屏蔽该信号的中断。从该寄存器读取将返回不可预测的值。

- INT_DIS:向该寄存器的任何位写入 1 会屏蔽该信号的中断。从该寄存器读取将返回不可预测的值。

- INT_STAT:该寄存器显示是否发生了中断事件。向该寄存器的某位写入 1 会清除该位的中断状态。向该寄存器的某位写入 0 会被忽略。

- INT_TYPE:该寄存器控制中断是边沿敏感还是电平敏感。

- INT_POLARITY:该寄存器控制中断是低电平有效还是高电平有效(或下降沿敏感还是上升沿敏感)。

- INT_ON_ANY:如果 INT_TYPE 设置为边沿敏感,则该寄存器允许在上升沿和下降沿发生中断事件。如果 INT_TYPE 设置为电平敏感,则该寄存器被忽略33至34。

14.3 编程指南

GPIO 控制器有四个组,MIO 和 EMIO 各两个。每个 GPIO 引脚可以单独编程。如 14.2.1 节 “设备引脚的 GPIO 控制” 中所述,可通过单次写入对多个引脚进行编程35至36。

14.3.1 启动序列

主要示例:启动序列

- 复位:复位选项在 14.4.2 节 “复位” 中描述。

- 时钟:时钟在 14.4.1 节 “时钟” 中描述。

- GPIO 引脚配置:将引脚配置为输入 / 输出在 14.3.2 节 “GPIO 引脚配置” 中描述。

- 向 GPIO 输出引脚写入数据:参见 14.3.3 节 “向 GPIO 输出引脚写入数据” 中的示例。

- 从 GPIO 输入引脚读取数据:参见 14.3.4 节 “从 GPIO 输入引脚读取数据” 中的示例。

- 将 GPIO 引脚设置为唤醒事件:参见 “GPIO 作为唤醒事件” 部分中的示例37至38。

14.3.2 GPIO 引脚配置

每个单独的 GPIO 引脚可配置为输入 / 输出。但是,bank0 的 [8:7] 引脚必须配置为输出。有关更多详细信息,请参阅 14.2.3 节 “Bank0 的位 [8:7] 为输出”39至40。

示例:将 MIO 引脚 10 配置为输出

- 将方向设置为输出:向 gpio.DIRM_0 寄存器写入 0x0000_0400。

- 设置输出使能:向 gpio.OEN_0 寄存器写入 0x0000_0400。

注:输出使能仅在 GPIO 引脚配置为输出时才有意义41至42。

示例:将 MIO 引脚 10 配置为输入

- 将方向设置为输入:向 gpio.DIRM_0 寄存器写入 0x0。这将 gpio.DIRM_0 [10] 设置为 043至44。

14.3.3 向 GPIO 输出引脚写入数据

对于配置为输出的 GPIO 引脚,有两种方法可对所需值进行编程45至46。

选项 1:使用 gpio.DATA_0 寄存器读取、修改和更新 GPIO 引脚。

示例:使用 DATA_0 寄存器设置 GPIO 输出引脚 10。

- 读取 gpio.DATA_0 寄存器:将 gpio.DATA_0 寄存器读取到 reg_val 变量。

- 修改值:设置 reg_val [10]=1。

- 向输出引脚写入更新后的值:将 reg_val 写入 gpio.DATA_0 寄存器47至48。

选项 2:使用 MASK_DATA_x_MSW/LSW 寄存器更新一个或多个 GPIO 引脚。

示例:使用 MASK_DATA_0_MSW 寄存器将输出引脚 20、25 和 30 设置为 1。

- 生成引脚 20、25 和 30 的掩码值:要驱动引脚 20、25 和 30,0xBDEF 是 gpio.MASK_DATA_0_MSW [MASK_0_MSW] 的掩码值。

- 生成引脚 20、25、30 的数据值:要在引脚 20、25 和 30 上驱动 1,0x4210 是 gpio.MASK_DATA_0_MSW [DATA_0_MSW] 的数据值。

- 向 MASK_DATA_x_MSW 寄存器写入掩码和数据:向 gpio.MASK_DATA_0_MSW 寄存器写入 0xBDEF_421049至50。

14.3.4 从 GPIO 输入引脚读取数据

对于配置为输入的 GPIO 引脚,有两种方法可监控输入51至52。

选项 1:使用每个组的 gpio.DATA_RO_x 寄存器。

示例:使用 DATA_RO_0 寄存器读取 bank 0 中所有 GPIO 输入引脚的状态。

- 读取输入 Bank 0:读取 gpio.DATA_0 寄存器53至54。

选项 2:在输入引脚上使用中断逻辑(参见 14.2.4 节 “中断功能”)。

示例:将 MIO 引脚 12 配置为上升沿触发。

- 将触发设置为上升沿:向 gpio.INT_TYPE_0 [12] 写入 1。向 gpio.INT_POLARITY_0 [12] 写入 1。向 gpio.INT_ANY_0 [12] 写入 0。

- 启用中断:向 gpio.INT_EN_0 [12] 写入 1。

- 输入引脚的状态:gpio.INT_STAT_0 [12] =1 表示发生了中断事件。

- 禁用中断:向 gpio.INT_DIS_0 [12] 写入 155至56。

14.3.5 GPIO 作为唤醒事件

GPIO 可配置为唤醒设备。

重要提示:必须正确设置 GIC。

- 在 GIC 中启用 GPIO 中断。

- 使用 gpio.INT_EN_{0..3} 寄存器启用所需引脚的 GPIO 中断。向 gpio.INT_EN_0 [10] 设置 1 以启用 GPIO10 中断。

- 不要关闭任何与 GPIO 相关的时钟57至58。

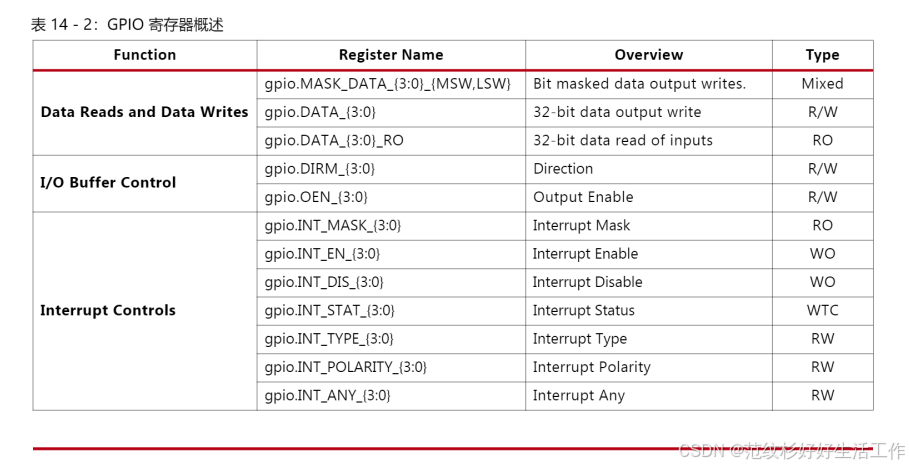

14.3.6 寄存器概述

GPIO 寄存器的概述如表 14-2 所示(另请参见 14.2.1 节 “设备引脚的 GPIO 控制”)。寄存器的详细信息在附录 B “寄存器详细信息” 中提供59至60。

14.4 系统功能

本节描述控制器的时钟和复位。GPIO 控制器中生成的所有中断都路由到 IRQ 52。GPIO I/O 信号路由到 MIO 或 EMIO61至62。

14.4.1 时钟

控制器由来自 APB 接口的 CPU_1x 时钟提供时钟。所有输出和输入采样都使用 CPU_1x 时钟进行63至64。

为了进行电源管理,可以使用 slcr.APER_CLK_CTRL [GPIO_CPU_1XCLKACT] 对 GPIO 控制器时钟采用时钟门控65。

14.4.2 复位

控制器由 slcr.GPIO_RST_CTRL [GPIO_CPU1X_RST] 位复位。有关更多信息,请参阅第 26 章 “复位系统”。此复位仅影响总线接口,不影响控制器逻辑本身66至67。

14.4.3 中断

控制器中断在 14.2.4 节 “中断功能” 中说明。控制器向 GIC 断言 IRQ #52。编程示例在 14.3.4 节 “从 GPIO 输入引脚读取数据” 中描述68至69。

14.5 I/O 接口

14.5.1 MIO 编程

Bank0 和 Bank1 引脚通过 MIO 路由。这些引脚可使用 slcr.MIO_PIN_XX 寄存器配置为 GPIO70至71。

示例:将 MIO 引脚 6 配置为 GPIO 信号

- 选择 MIO 引脚作为 GPIO:设置 L0_SEL、L1_SEL、L2_SEL、L3_SEL = L3_SEL =0。

- 设置 TRI_ENABLE =0。

- LVCMOS18(有关其他电压选项,请参阅寄存器定义)。

- 慢 CMOS 边沿。

- 启用内部上拉电阻。

- 禁用 HSTL 接收器。

注:如果 TRI_ENABLE=1,则无论任何 GPIO 设置如何,输出都处于三态。如果 TRI_ENABLE =0,则三态由 gpio.OEN_x 寄存器控制72至73。