RK3399 启动流程 --从复位到系统加载

一、启动入口:ROM Code的执行

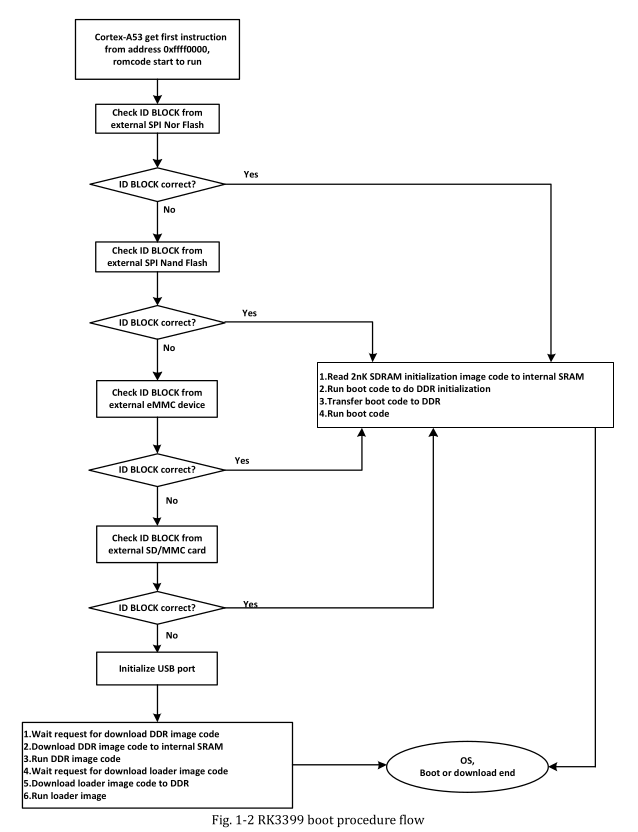

RK3399的启动流程始于Cortex-A53核心从固定地址0xFFFF0000获取第一条指令。这个地址是Rockchip芯片设计的硬件复位向量,由内置的ROM Code(固化在芯片内部的引导代码)开始执行。ROM Code作为启动流程的"第一推动力",负责初始化基础硬件并寻找可启动的存储设备。

二、存储设备探测:四级递进式检查

ROM Code会按照特定顺序探测外部存储设备,采用经典的"设备树"式检测逻辑:

- SPI Nor Flash优先检测:首先检查高速串行闪存,适合存储小型引导程序。

- SPI NAND Flash次之:针对采用NAND架构的串行闪存设备。

- eMMC设备检测:嵌入式存储介质,常见于工业级应用。

- SD/MMC卡最后检测:作为可移动存储的备选方案。

每个检测环节都会验证设备的ID BLOCK(标识块),这是Rockchip定义的特定数据结构,包含设备签名和基础参数。只有当ID BLOCK验证通过时,才会进入对应设备的启动流程。

三、备用方案:USB启动模式

当所有存储介质均未通过验证时,系统会初始化USB OTG端口,进入下载模式(Download Mode)。这种设计为系统恢复提供了最后手段:

- 开发者可通过USB烧录工具重新写入引导程序

- 支持Rockchip特有的MaskROM模式修复砖机

四、内存初始化:精密的三阶段加载

成功识别启动设备后,系统执行精密的初始化序列:

- SRAM阶段:将SDRAM初始化代码(通常<32KB)加载到芯片内部SRAM运行,避开未初始化的DDR内存。

- DDR初始化:运行SRAM中的代码配置内存控制器,使外部DDR内存可用。

- 代码转移:将更大的引导代码从存储设备搬运到已初始化的DDR内存。

五、多级引导架构

RK3399采用典型的嵌入式系统引导链:

- DDR Image:包含基础硬件驱动和文件系统支持

- Loader Image:实现更复杂的设备初始化和安全验证

- 最终引导:加载操作系统内核(如Linux)或进入Fastboot等特殊模式

六、设计特点分析

- 容错机制:多级存储检测确保单一存储故障不影响系统恢复能力

- 安全考虑:每阶段代码都需验证完整性签名

- 性能优化:通过SRAM先行初始化DDR的设计避免内存冲突

- 扩展性:USB下载模式支持后期固件更新

该流程图清晰展现了现代ARM SoC从硬件复位到软件加载的完整过程,其模块化设计思想值得嵌入式开发者借鉴。理解这个流程对于进行RK3399平台的低层开发、系统移植和故障诊断都具有重要意义。