3-基于FZ3B的Vitis AI DPU加速平台搭建

基于FZ3B的Vitis AI DPU加速平台搭建

- 0 前言

- 1 环境搭建

- 2 具体部署-面向硬件开发者

- 2.1 Vivado最小系统构建

- 2.2 Petalinux工程构建

- 3 遇到的问题

0 前言

DPU 的部署通常可分为两条技术路线:① Vivado → Vitis → PetaLinux,② Vivado → PetaLinux。这两种体系的存在,旨在分别服务于硬件开发工程师与软件开发工程师的开发需求。前者强调底层的硬件设计与优化,适合具备 FPGA 开发经验的人员;而后者则更侧重于基于 Vitis AI 的软件应用开发,使开发者无需深入了解 FPGA 细节也能快速上手。

然而,由于 Xilinx 官方在 Vitis AI 相关资料的组织和维护方面存在一定混乱,导致用户在实际部署过程中常常遇到困扰。因此,整理一套清晰、详细的运行流程具有重要意义,有助于提升开发效率并降低系统集成的复杂度。

1 环境搭建

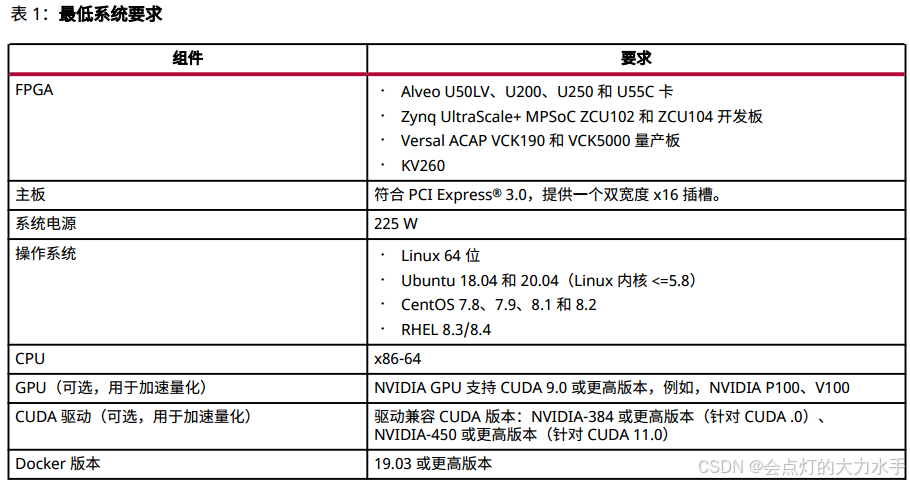

根据官方文档 UG1414 的说明,搭建 Vitis AI 环境有最低系统要求限制。此外,不同版本的 DPU 还对所需的 Xilinx 工具链(包括 Vivado、Vitis 和 PetaLinux)版本以及 Linux 系统内核版本提出了明确要求(不要抱有侥幸心理,三者之间依赖关系很强)。以 Vitis AI 1.4 至 2.0 为例,建议使用 Xilinx 2021.2 工具链版本,并搭配 Ubuntu 18.04 或 Ubuntu 20.04 作为开发主机的操作系统,以确保各组件间的兼容性和工具运行的稳定性。DPU与环境要求

2 具体部署-面向硬件开发者

2.1 Vivado最小系统构建

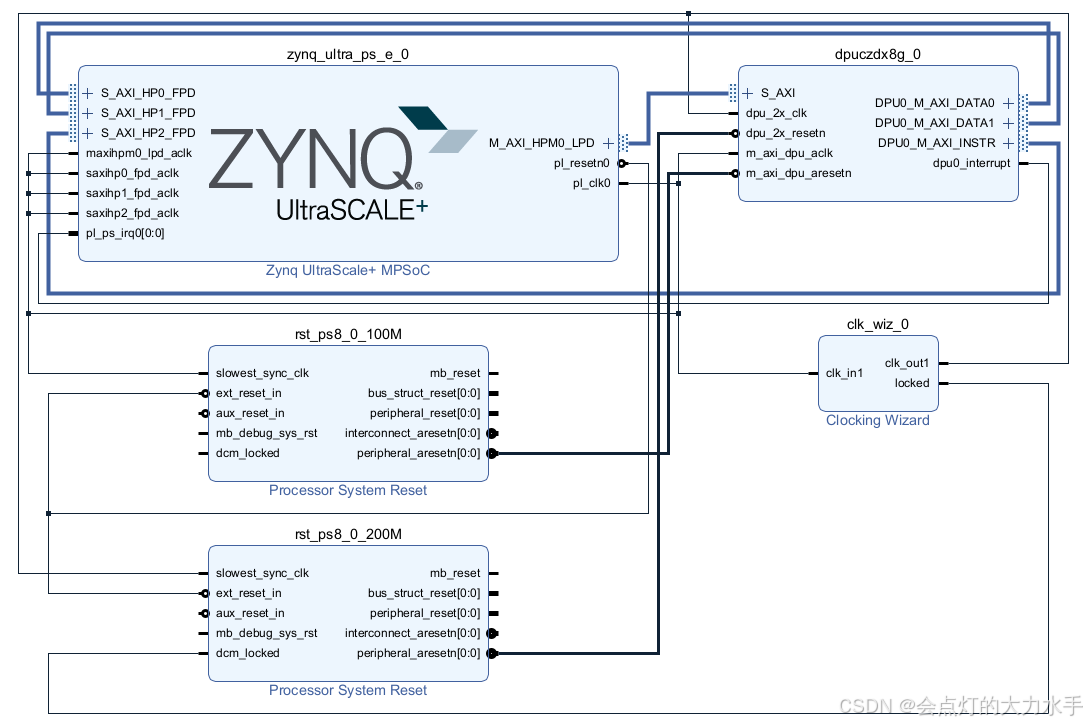

根据所选用的 DPU 版本与型号的不同,需前往 Xilinx 官网下载对应版本的资源包,并将 DPU IP 核路径添加至 Vivado 的 IP 仓库中,以便在 Block Design 中调用使用。在完成最小系统的构建基础上,仅需额外添加少量必要接口,即可满足 DPU 的部署需求。这些接口包括:

- 中断信号

irq, - 两个 128-bit 数据位宽的高速端口

HP0和HP1, - 一个 32-bit 数据位宽的高速端口

HP2, - 一个 32-bit 的主机端口

HPM0。

时钟方面,DPU 所需的时钟信号可直接连接至 Processing System 中提供的 CLKx1 和 CLKx2 时钟输出。

2.2 Petalinux工程构建

Vivado生成包含bit的xsa之后即可进行Petalinux的构建,一些基础的配置没有什么特殊的,可以直接查阅之前的文章

Vitis-AI-resource-2.0

Vitis-Tutorials-2.0

3 遇到的问题

1、Ubuntu20.04安装Xilinx卡在最后一步

缺少依赖库,需要先安装库再重新安装Xilinx。

2、综合过程失败

虚拟机配置的运存8G不够,需要增加到16G。

3、Vitis运行时失败

y2k22-Patch