非整数倍数据位宽转换24to128

描述

实现数据位宽转换电路,实现24bit数据输入转换为128bit数据输出。其中,先到的数据应置于输出的高bit位。

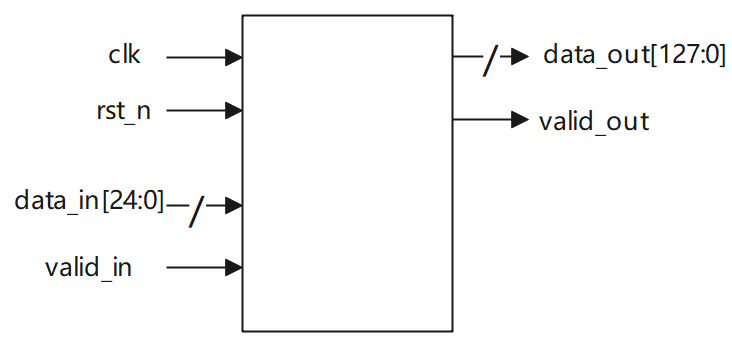

电路的接口如下图所示。valid_in用来指示数据输入data_in的有效性,valid_out用来指示数据输出data_out的有效性;clk是时钟信号;rst_n是异步复位信号。

接口时序示意图

输入描述

input clk , input rst_n ,input valid_in ,input [23:0] data_in 输出描述

output reg valid_out ,output reg [127:0] data_out解题分析

输入:valid_in, data_in[23:0]

输出:valid_out,data_out[127:0]

输入数据是24bit,输出数据是128bit。

因为128×3=24×16128\times3=24\times16128×3=24×16,所以每输入16个有效数据,就可以产生三个完整的输出。因此设置一个仅在输入数据有效时工作的计数器cnt,计数范围是0-15。

reg [3:0] cnt;always@(posedge clk or negedge rst_n) beginif(~rst_n)cnt <= 0;elsecnt <= ~valid_in? cnt:cnt==15 ? 0 :cnt+1;end

然后设置一个数据暂存器data_lock,每当输入有效时,将数据从低位移入。

reg [127:0] data_lock;

always@(posedge clk or negedge rst_n) beginif(~rst_n)data_lock <= 0;elsedata_lock <= valid_in? {data_lock[103:0], data_in}: data_lock;

end

由上图易得,每当计数器cnt计数到5、10、15时,data_out要进行更新,并拉高valid_out一个周期。

always@(posedge clk or negedge rst_n) beginif(~rst_n)valid_out <= 0;elsevalid_out <= (cnt==5 || cnt==10 || cnt==15)&&valid_in;endalways@(posedge clk or negedge rst_n) beginif(~rst_n)data_out <= 0;else if(cnt==5)data_out <= valid_in? {data_lock[119:0], data_in[23:16]}: data_out;else if(cnt==10)data_out <= valid_in? {data_lock[111:0], data_in[23: 8]}: data_out;else if(cnt==15)data_out <= valid_in? {data_lock[103:0], data_in[23: 0]}: data_out;elsedata_out <= data_out;end

参考代码

`timescale 1ns/1nsmodule width_24to128(input clk , input rst_n ,input valid_in ,input [23:0] data_in ,output reg valid_out ,output reg [127:0] data_out

);reg [3:0] cnt;reg [127:0] data_lock;always@(posedge clk or negedge rst_n) beginif(~rst_n)cnt <= 0;elsecnt <= ~valid_in? cnt:cnt+1;endalways@(posedge clk or negedge rst_n) beginif(~rst_n)valid_out <= 0;elsevalid_out <= (cnt==5 || cnt==10 || cnt==15)&&valid_in;endalways@(posedge clk or negedge rst_n) beginif(~rst_n)data_lock <= 0;elsedata_lock <= valid_in? {data_lock[103:0], data_in}: data_lock;endalways@(posedge clk or negedge rst_n) beginif(~rst_n)data_out <= 0;else if(cnt==5)data_out <= valid_in? {data_lock[119:0], data_in[23:16]}: data_out;else if(cnt==10)data_out <= valid_in? {data_lock[111:0], data_in[23: 8]}: data_out;else if(cnt==15)data_out <= valid_in? {data_lock[103:0], data_in[23: 0]}: data_out;elsedata_out <= data_out;end

endmodule

注:解题分析来源于网友,如有侵权,请告删之。