riscv中断处理软硬件流程总结

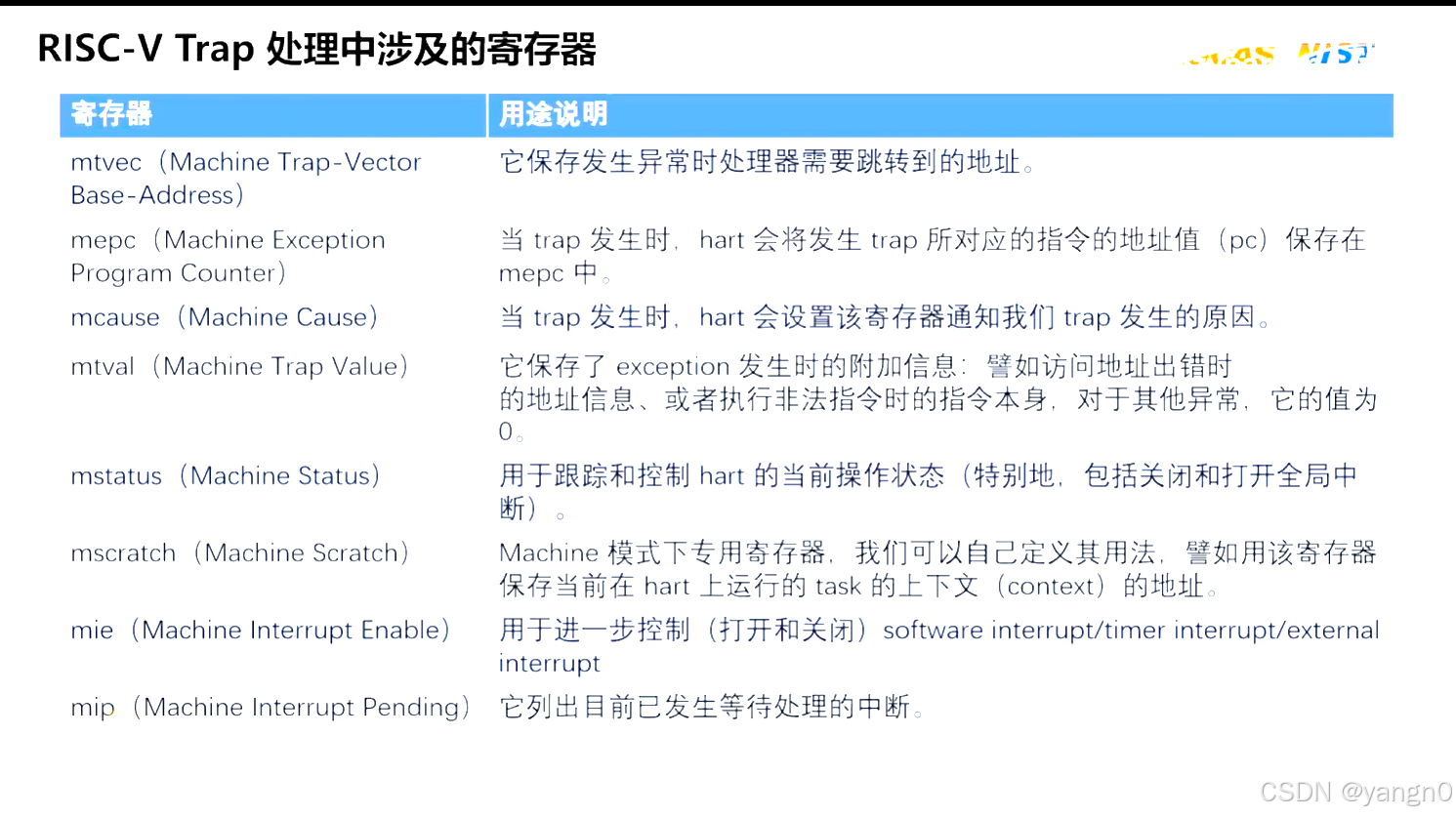

trap相关csr

trap初始化

需要在程序里先设置好mtvec,如果需要中断委托的话还需要设置mideleg、medeleg。

硬件处理过程

硬件先去关中断

- 设置mstatus.xPIE为trap发生时xIE的值。

- 设置mstatus.xIE为0。

- 设置mepc为 当前指令(异常)或下一条指令的地址(中断)。

指令触发同步异常后,处理程序处理后再重新执行一次这个指令。例如:缺页异常。

如果是中断的话,在这个指令执行末尾才会跳异常处理程序,所以返回时直接跑下一条指令就可以。 - 设置pc为mtvec设定的值。

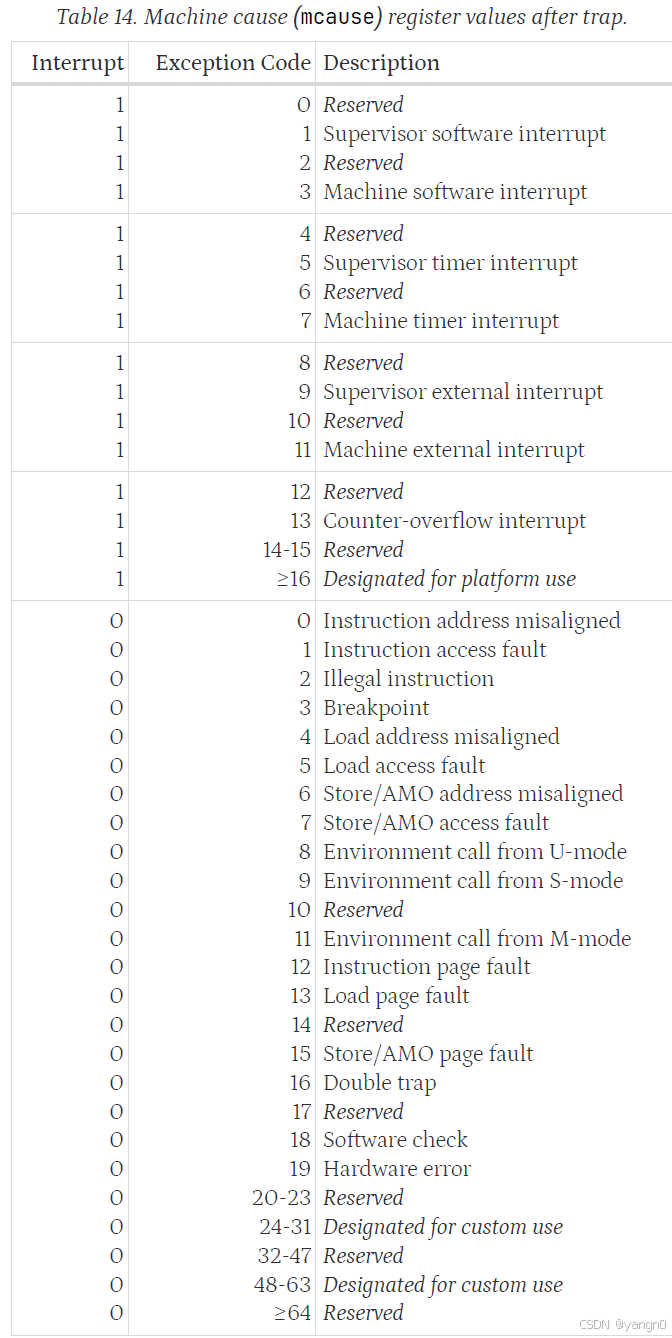

- 设置mcause为trap发生的原因(exception code)。

- 设置mtval为该异常的附加信息。

- 设置mstatus.xPP为trap发生时的权限级别值。

软件处理过程

- 保存当前控制流的上下文信息(通用寄存器x1-x31),利用mscratch。

mscratch中保存当前上下文信息的内存地址,没法直接使用,需要先用csr指令读出来放到一个通用寄存器里。比如:可以用x31(t6)寄存器,使用csrrw t6, mscratch, t6交换寄存器的数据,然后就可以用sw指令来将信息保存进t6里的地址处了。 - trap handler

- 从trap handler返回,mepc可以调整。

- 恢复上下文的信息。

- 执行MRET返回到trap之前。

xRET后硬件处理流程

- 将当前hart的特权等级改为mstatus.MPP的值。

- 将mstatus.MPIE的值恢复到mstatus.MIE。

- mstatus.MPIE更新为1。

- 将pc设置为mepc。