CUDA 编程笔记:GPU 硬件资源

一、前言

本文主要针对 Nvidia 的 GPU 进行总结,分为流多处理器 SM,线程模型与物理结构和线程束三部分。

二、流多处理器 SM

物理上,GPU 最基本的处理单元为 SP(streaming processor),又称为 CUDA core,主要包括若干整数型运算的核心、若干单精度浮点数运算的核心、若干双精度浮点数运算的核心、若干单精度浮点数超越函数的特殊函数单元、若干混合精度的张量核心(有伏特架构引进,适用于机器学习)。最后具体的指令和任务都是在 SP 上处理的,GPU 进行并行计算,即为多个 SP 同时做处理。

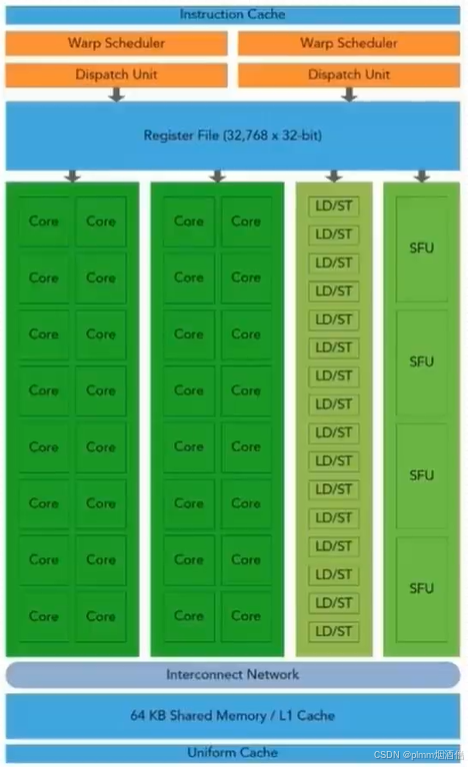

而 SM(streaming multiprocessor)则是 GPU 的核心,又称为 GPU 大核。它由一定数量的寄存器、一定数量的共享内存

、常量内存的缓存、纹理内存和表面内存的缓存、L1缓存、线程束(thread warp)调度器、SP 组成。每个流式多处理器可以视为具有较小结构的 CPU,支持指令并行(多发射)。流式多处理器是线程块的运行载体,但一般不支持乱序执行。每个流式多处理器上的单个 Warp 以 SIMD 方式执行相同指令。

一个典型的 Fermi 架构 SM 包括以下几个组件:

(1)核心SP(CUDA core)

(2)共享内存/一级缓存 (ShareMem/Cache)

(3)寄存器文件 (Register File)

(4)加载/存储单元 (LD/ST)

(5)特殊功能单元 (SFU)

(6)线程束调度器 (Warp Sched)

1. GPU中每个SM(流多处理器)都可以支持数百个线程并发(不是并行)执行;

2. 以线程块(block)为单位向 SM 分配资源,多个线程块可被同时分配到一个可用的 SM 上;

3. 线程块与 SM 的绑定关系具有独占性:一旦分配后,该线程块不可再被分配到其他 SM。

SM 的基本执行单元是线程束(thead warp),线程束包含 32 个线程,这些线程同时执行相同的指令,但是每个线程都包含自己的指令地址计数器和寄存器状态,也有自己独立的执行路径。

三、线程模型与物理结构

1、逻辑角度分析

1. 线程组织架构

(1)可定义成千上万个线程

(2)线程组织为线程块(Block)和网格(Grid)层级结构

2. 资源分配规则

(1)网格中所有线程块需分配到 SM(流多处理器)执行

(2)单个线程块内的线程固定绑定到同一 SM,但一个 SM 可同时托管多个线程块

3. 调度单元

(1)线程块分配到 SM 后,会按 32 线程为一组分割,每组称为一个Wrap/Warp

2、物理角度分析

1. 硬件资源限制

(1)SM 的寄存器、共享内存等物理资源有限

(2)实际可同时活跃的线程束(Warp)数量受 SM 资源严格约束

2. 关键结论

(1)逻辑层定义的线程规模 ≠ 物理层实际执行效率

(2)需通过优化线程块大小、资源占用以匹配SM硬件特性

四、线程束

CUDA线程执行模型(SIMT架构)

1. 核心机制

(1)采用单指令多线程(SIMT)架构管理线程

(2)以32个线程为一组构成基本执行单元,称为线程束(Warp)

2. 线程束生成规则

(1)在同一个线程块(Thread Block)内:

(2)相邻的连续32个线程自动归并为同一线程束

示例:

第0~31号线程 → 第0个线程束

第32~63号线程 → 第1个线程束

3. 硬件执行特性

(1)线程束是GPU调度和指令执行的最小单位

(2)同一线程束内所有线程同步执行相同指令(SIMT核心特征)