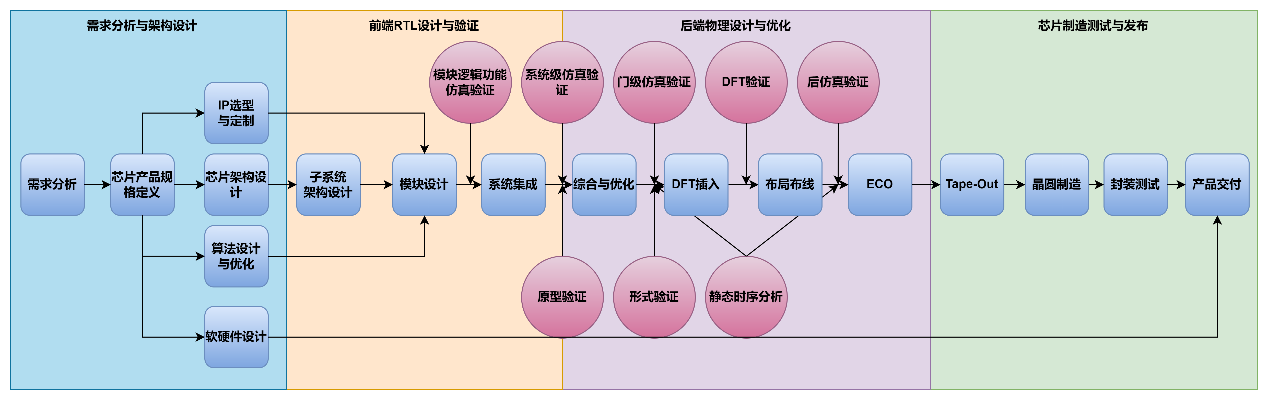

芯片设计流程

这是 芯片设计全流程(从需求到交付)的阶段划分与逻辑关系图 ,覆盖芯片设计的四大核心阶段:需求分析与架构设计→前端 RTL 设计与验证→后端物理设计与优化→芯片制造测试与发布 ,帮你理解芯片是如何从 “概念” 变成 “产品” 的,拆解如下:

1. 四大阶段与核心任务

1.1 需求分析与架构设计(最左端,蓝色区域 )

- 核心目标:明确 “做什么样的芯片”,规划整体技术方案。

- 关键步骤:

- 需求分析:调研市场 / 客户需求(如手机芯片需要高性能 + 低功耗 )。

- 芯片产品规格定义:把需求转化为技术指标(如 CPU 频率、内存带宽、接口标准 )。

- 芯片架构设计:规划芯片的 “大框架”(如多核 CPU 怎么布局、子系统怎么划分 )。

- 子任务(分支):

- IP 选型与定制:选成熟 IP(如 USB 控制器)或定制特殊 IP(如 AI 加速模块 )。

- 算法设计与优化:为芯片功能(如图像处理、AI 推理 )设计高效算法。

- 软硬件协同设计:让硬件架构适配软件需求(如操作系统、应用程序 )。

1.2 前端 RTL 设计与验证(橙色区域 )

- 核心目标:把架构 “翻译” 成硬件可执行的 RTL 代码(Verilog/VHDL ),并验证功能是否正确。

- 关键步骤:

- 子系统架构设计:细化架构到子系统(如把 “AI 子系统” 拆成计算、存储、控制模块 )。

- 模块设计:用 RTL 代码实现每个子模块(如写一个 UART 控制器的 Verilog 代码 )。

- 系统集成:把所有子模块整合,形成完整的芯片 RTL 代码。

- 验证环节(粉色圆形 ):

- 模块逻辑功能仿真验证:验证单个模块的功能(如 UART 能否正确收发数据 )。

- 系统级仿真验证:验证整个芯片的系统功能(如手机芯片的多核调度是否正常 )。

- 原型验证:在 FPGA 上跑 RTL 代码,快速验证硬件逻辑(比软件仿真更快、更接近真实硬件 )。

- 形式验证:用数学方法证明 RTL 代码的逻辑正确性(避免死锁、逻辑冲突 )。

1.3 后端物理设计与优化(紫色区域 )

- 核心目标:把 RTL 代码变成 “物理版图”(芯片制造需要的几何图形 ),并优化性能、面积、功耗。

- 关键步骤:

- 综合与优化:把 RTL 代码转化为门级网表(用基本逻辑门描述电路 ),并优化时序、面积。

- DFT 插入(可测性设计 ):插入测试电路,方便芯片制造后检测缺陷(如扫描链 )。

- 布局布线:给每个逻辑单元(如寄存器、门电路 )分配物理位置,连线并满足时序约束(如时钟树综合 )。

- 验证环节(粉色圆形 ):

- 门级仿真验证:验证门级网表的功能(确保综合后的电路和 RTL 功能一致 )。

- DFT 验证:验证测试电路是否有效(能否检测出制造缺陷 )。

- 后仿真验证:考虑实际物理效应(如线延迟、串扰 ),验证芯片在真实环境下的功能。

- 静态时序分析(STA):检查电路是否满足时序要求(如建立时间、保持时间 )。

- ECO(工程变更命令 ):如果验证发现问题,微调物理设计(无需重新走全流程 )。

1.4 芯片制造测试与发布(绿色区域 )

- 核心目标:把物理版图 “变成真实芯片”,并测试、封装、交付。

- 关键步骤:

- Tape-Out(流片 ):把物理版图文件发给代工厂,开始制造芯片。

- 晶圆制造:在硅片上用光刻、蚀刻等工艺,把版图变成实际电路(最耗时、最花钱的环节 )。

- 封装测试:把晶圆切成芯片,封装(如 BGA、QFN 封装 ),并测试成品芯片的功能、性能。

- 产品交付:把合格的芯片交给客户(如手机厂商、电脑厂商 )。

2. 阶段间的依赖关系

- 顺序执行,环环相扣:

需求→架构→前端设计→后端设计→制造→交付,前一阶段的输出是后一阶段的输入(如前端 RTL 代码给后端物理设计 )。 - 验证贯穿始终:

每个阶段都有 “验证 / 测试” 环节(如前端的仿真、后端的后仿真、制造后的封装测试 ),确保芯片功能、性能符合要求,避免流片后才发现问题(代价极高 )。

3. 为什么要分这么多阶段?

- 复杂度拆解:芯片设计极其复杂(千万级 / 亿级晶体管 ),必须分阶段细化,否则无法管理。

- 风险控制:每个阶段验证通过后再进入下一阶段,避免后期发现问题导致 “推倒重来”(流片失败损失巨大 )。

- 专业分工:不同阶段需要不同技能(前端懂 RTL 设计,后端懂物理实现,制造懂光刻工艺 ),分阶段让团队聚焦专业领域。

一句话总结

这张图是芯片设计的 “全流程地图”:从需求出发,先规划架构,再用 RTL 代码实现并验证,接着做物理版图设计与优化,最后制造、测试、交付。每个阶段都有明确任务和验证环节,确保芯片从 “概念” 到 “产品” 的可靠性,是芯片设计团队协作的基本框架 。

4 FPGA原型验证

FPGA(Field - Programmable Gate Array,现场可编程门阵列)原型验证是芯片设计流程中用于验证 RTL(Register - Transfer Level,寄存器传输级)代码的关键环节,以下从多个方面对其进行详细讲解:

4.1 基本原理

FPGA 是一种可编程的硬件器件,它内部包含了大量的逻辑单元(如查找表、触发器等)、布线资源以及存储器等。通过对 FPGA 的编程,能够将 RTL 代码所描述的硬件逻辑映射到 FPGA 的物理资源上 。具体来说,开发工具会对 RTL 代码进行综合,将其转换为门级网表,然后进行布局布线,把逻辑单元和连线合理地分配到 FPGA 的芯片结构中,最终实现与目标芯片类似的硬件行为。

4.2 优势

- 速度快:软件仿真是在计算机上通过软件算法来模拟硬件行为,存在较大的时间开销。而 FPGA 原型验证是基于实际的硬件电路运行,其运行速度接近真实芯片。例如,对于一个复杂的处理器 RTL 代码,软件仿真可能需要数小时甚至数天来模拟芯片在特定场景下的运行,而在 FPGA 上进行原型验证,可能只需要几分钟就能完成同样场景的验证。

- 接近真实硬件:软件仿真很难完全准确地模拟硬件的所有特性,如信号的传输延迟、时钟的抖动、功耗等。FPGA 原型验证使用的是实际的硬件电路,能够更真实地反映硬件在实际工作中的情况。比如,在验证高速接口电路时,FPGA 可以模拟出信号在传输线上的延迟和反射等现象,这对于发现和解决硬件设计中的时序问题、信号完整性问题非常有帮助。

- 可扩展性:现代 FPGA 芯片通常具有丰富的资源,并且可以通过扩展板卡等方式增加额外的功能模块。在进行芯片原型验证时,如果 RTL 代码所描述的逻辑规模超出了单个 FPGA 的资源限制,可以通过多片 FPGA 级联的方式来实现更大规模的逻辑验证 。

- 实时调试:在 FPGA 原型验证过程中,可以利用一些调试工具实时观察硬件的运行状态,如信号的电平变化、寄存器的值等。这种实时调试功能可以帮助工程师快速定位和解决问题,而软件仿真在这方面相对不够直观和便捷。

4.3 实施流程

- RTL 代码准备:确保 RTL 代码的功能正确性和完整性,并且代码要符合综合工具的要求,例如遵循一定的编码规范,避免使用综合工具不支持的结构。

- FPGA 选型:根据 RTL 代码的规模(逻辑单元数量、存储容量需求等)、运行速度要求、接口类型等因素选择合适的 FPGA 芯片。例如,如果设计的是一个高性能的图像处理器,可能需要选择具有大量逻辑单元和高速接口的高端 FPGA 芯片。

- 综合与实现:使用 FPGA 综合工具(如 Synopsys 的 Design Compiler、Cadence 的 Genus 等)将 RTL 代码转换为门级网表,然后通过布局布线工具(如 Xilinx 的 Vivado、Intel 的 Quartus Prime 等)将网表映射到 FPGA 的物理资源上,完成电路的实现。

- 接口适配:设计和实现 FPGA 与外部设备之间的接口,如与测试设备、主机等的通信接口。例如,对于一个网络芯片的原型验证,需要设计以太网接口与外部网络设备进行通信,以验证芯片的网络功能。

- 调试与验证:将编译好的程序下载到 FPGA 中运行,通过调试工具(如逻辑分析仪、片上调试器等)观察硬件的运行状态,根据测试用例对 RTL 代码的功能进行验证。如果发现问题,需要回到 RTL 代码进行修改,然后重复上述流程,直到满足设计要求。

4.4 局限性

- 资源限制:尽管 FPGA 的资源越来越丰富,但对于一些超大规模的芯片设计,可能仍然无法完全容纳整个芯片的 RTL 代码。此时,需要对设计进行分割,分别在不同的 FPGA 上进行验证,这增加了验证的复杂性。

- 与真实芯片的差异:虽然 FPGA 接近真实硬件,但在工艺、电路结构等方面与目标芯片(如 ASIC,Application - Specific Integrated Circuit,专用集成电路)仍存在一定差异。例如,FPGA 的逻辑单元结构和 ASIC 中的标准单元不同,这可能导致在 FPGA 上验证通过的设计,在 ASIC 实现后出现一些意想不到的问题。

- 成本较高:高端 FPGA 芯片的价格昂贵,并且在进行原型验证时,可能还需要额外的开发板、测试设备等,这增加了验证的成本。同时,FPGA 原型验证的开发周期相对较长,也会带来一定的时间成本。

FPGA 原型验证在芯片设计中具有重要地位,它能够在芯片流片前快速、有效地验证 RTL 代码的功能和性能,帮助工程师提前发现和解决问题,从而降低芯片设计的风险和成本。