【从0到1制作一块STM32开发板】6. PCB布线--信号部分

在之前的学习中,我偏向的多是嵌入式软件开发的工作,如果想要自己diy一款具备特定功能的嵌入式工具的话,还需要具备画板子的能力。但由于我目前还没学模电,故我打算直接找个b站的学习视频先跟着画个板子出来,简单理解各个模块的功能,后续再详细了解其内部原理。

我选择的课程是expert实验室的PCB大师篇教学视频,链接如下:

【大师篇】8-stm32开发板原理图设计(单片机最小系统)_哔哩哔哩_bilibili

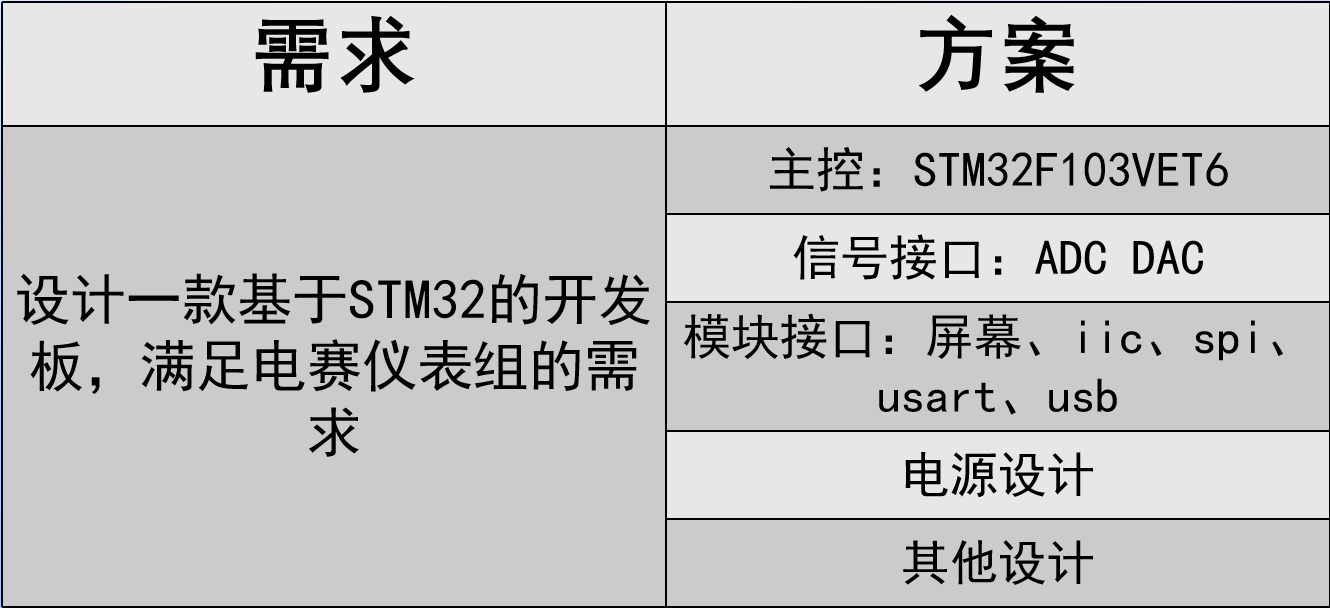

我将跟随教程做一个stm32f103vet6开发板出来,具体需求和方案如下:

接下来,我会尽可能以博客的形式将我每期的学习总结下来,仅供交流,如有谬误,欢迎指正。

接下来,我会尽可能以博客的形式将我每期的学习总结下来,仅供交流,如有谬误,欢迎指正。

本系列博客目录如下:

【从0到1制作一块STM32开发板】1. 芯片选型及电源电路设计-CSDN博客

【从0到1制作一块STM32开发板】2. 单片机最小系统设计-CSDN博客

【从0到1制作一块STM32开发板】3. 信号部分设计-CSDN博客

【从0到1制作一块STM32开发板】4. 模块化布局-CSDN博客

【从0到1制作一块STM32开发板】5. 整体布局-CSDN博客

1. 本节概述

1.1. 要做什么

简单来说,就是要将PCB上的飞线转化为实际的走线网络。

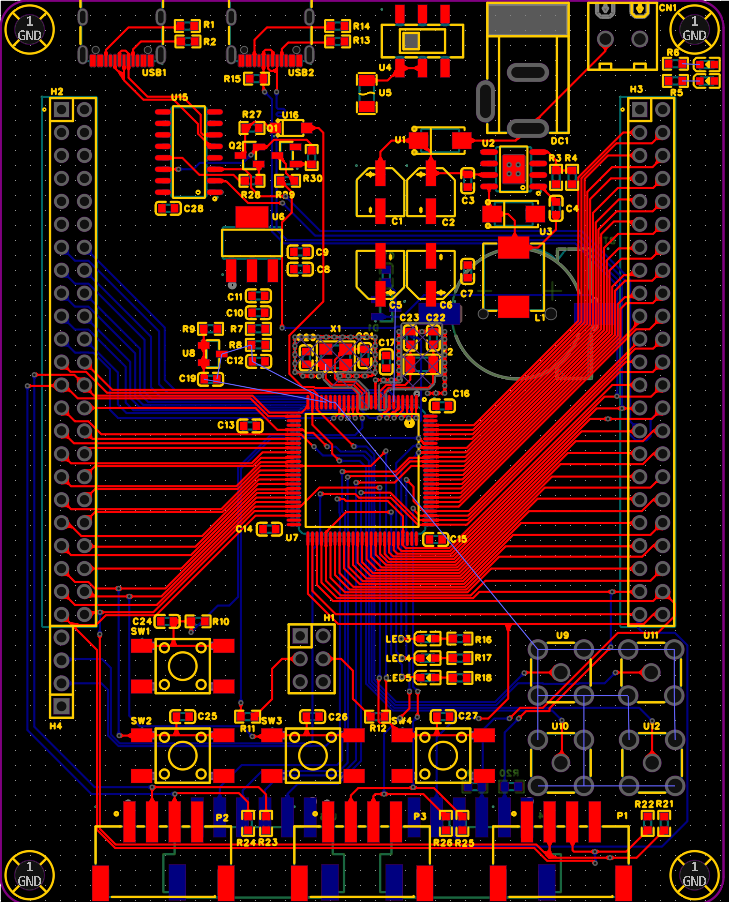

2. 整体信号部分布线效果

由于布线部分并不好一个模块一个模块地讲解,故只标注需要关注的部分。

3. 注意点

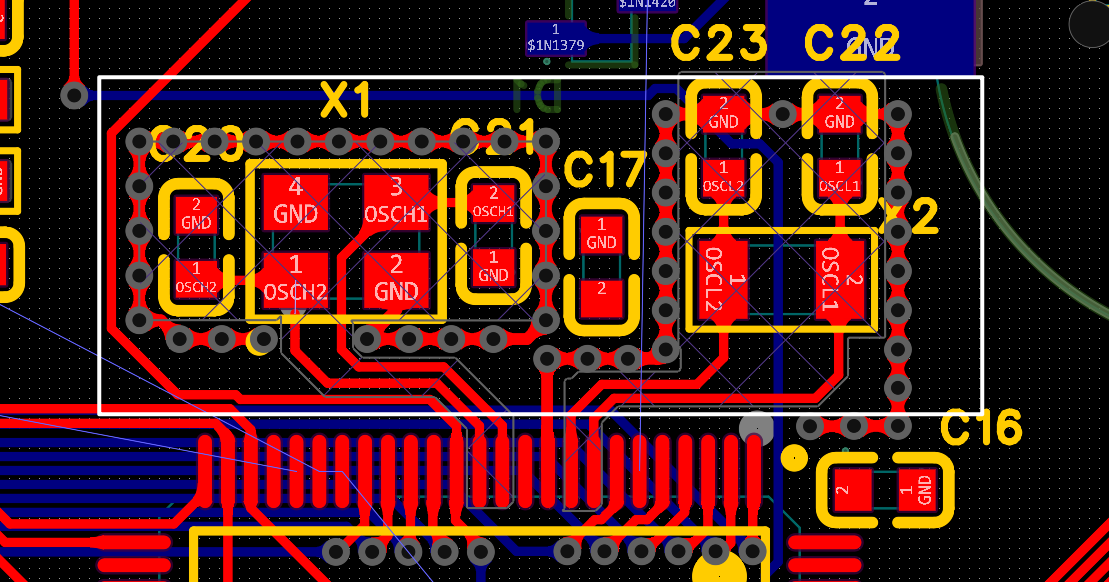

3.1 晶振隔离处理

在对晶振部分的飞线做好连接之后,需要用接地过孔将该区域隔离,并将此区域设置为禁止铺铜区。隔离是为了让晶振在一个“干净、安静”的电磁环境中工作,避免它受外界干扰,也减少它对外界的干扰,从而保证系统时钟稳定和 EMC 可靠性

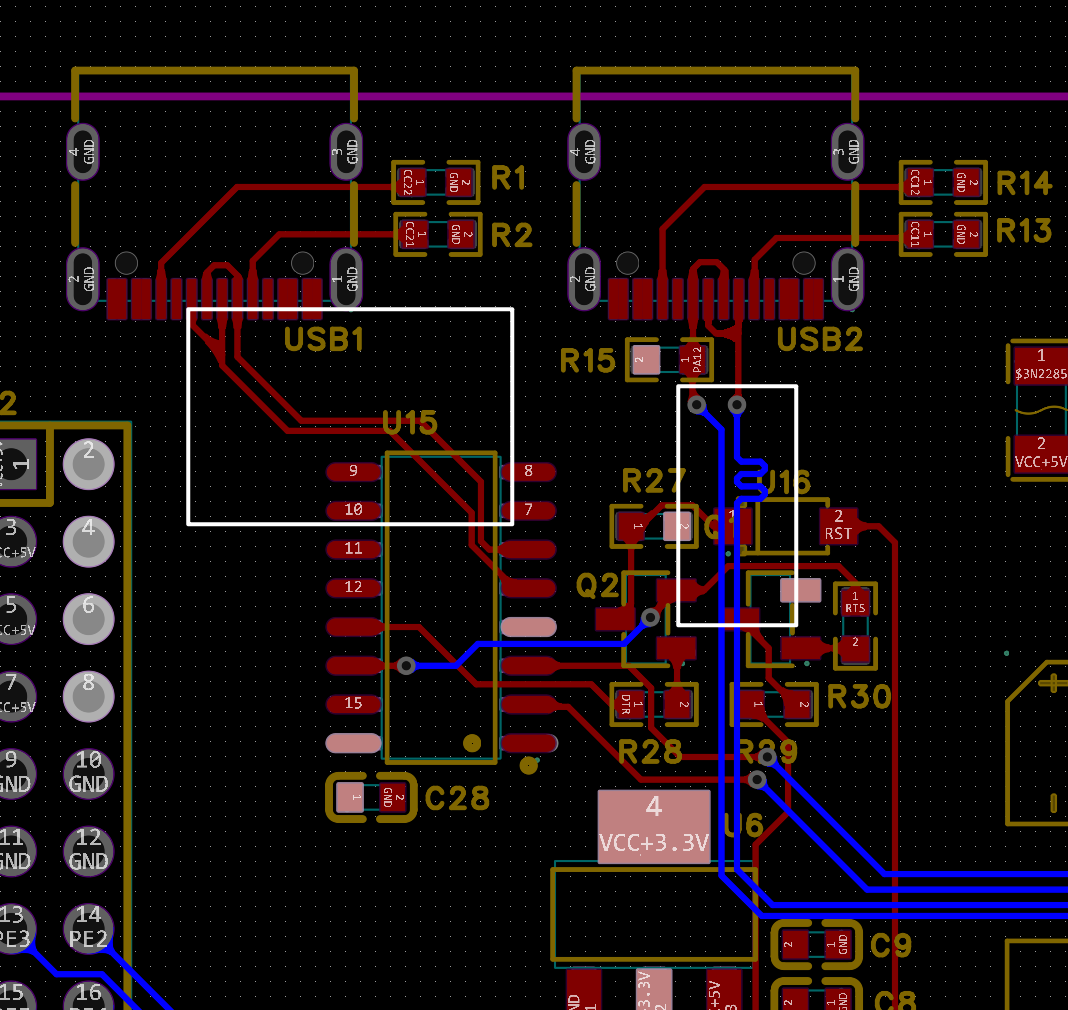

3.2 USB信号线差分布线

两个typec接口的usb信号端口需要进行差分布线,因为其本身是差分信号。核心是保证两根线的长度差小于10mil。可使用立创eda中菜单栏的布线-等长调节来实现蛇形布线,以减小长度误差。

总结

本文讲解了项目-stm32f103vet6开发板设计的信号布线部分。