PCIe Base Specification解析(八)

文章目录

- 4 Physical Layer Logical Block

- 4.1Introduction

- 4.2 Logical Sub-block

- 4.2.1 Encoding for 2.5 GT/s and 5.0 GT/s Data Rates

- 4.2.1.1 Symbol Encoding

- 4.2.1.1.1 Serialization and De-serialization of Data

- 4.2.1.1.2 Special Symbols for Framing and Link Management(K code)

- 4.2.1.1.3 8b/10b Decode Rules

- 4.2.1.2 Framing and Application of Symbols to Lanes

- 4.2.1.3 Data Scrambling

- 4.2.2 Encoding for 8.0 GT/s and Higher Data Rates

- 4.2.2.1 Lane Level Encoding

- 4.2.2.2 Ordered Set Blocks

- 4.2.2.2.1 Block Alignment

- 4.2.2.3 Data Blocks

- 4.2.2.3.1 Framing Tokens

- 4.2.2.3.2 Transmitter Framing Requirements

4 Physical Layer Logical Block

4.1Introduction

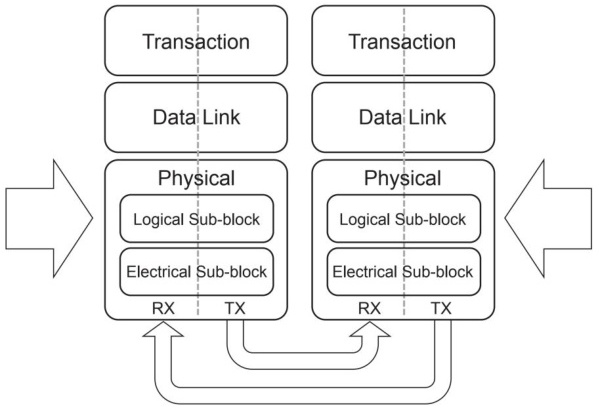

物理层规范分为逻辑子层和电气子层,如Figure 4-1所示。

Figure 4-1 Layering Diagram Highlighting Physical Layer

4.2 Logical Sub-block

逻辑子层介于数据链路层与电气子层之间。

4.2.1 Encoding for 2.5 GT/s and 5.0 GT/s Data Rates

4.2.1.1 Symbol Encoding

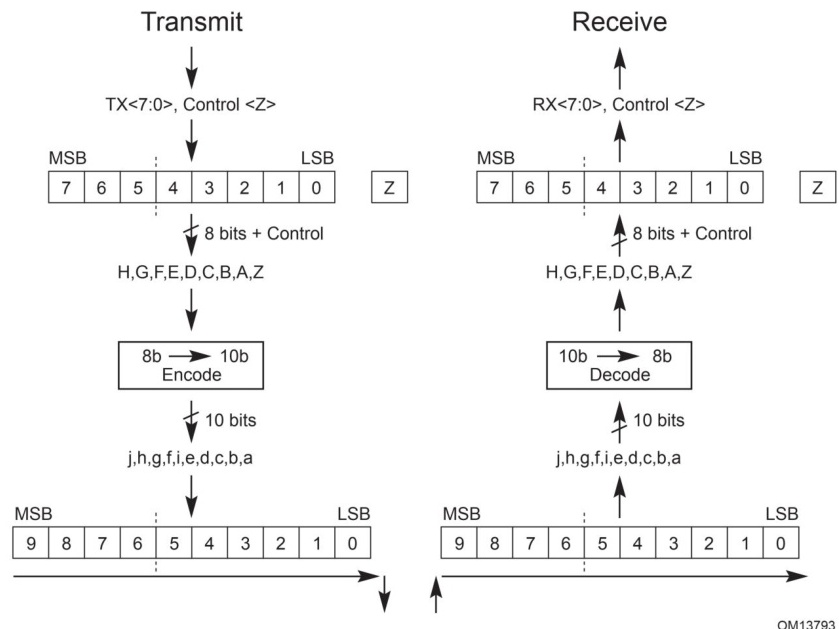

在2.5GT/s和5.0GT/s下,PCle用8b/10b编码传输。这套传输码的定义符合ANSI X3.230-1994,clause 11(同样也符合 IEEE 802.3z,36.2.4)的定义。这种方案将8bit数据分成两个部分:3bit部分和5bit部分,分别映射到一个4bit编码和一个6bit编码。控制位(Control<Z>)与数据字符(TX<7:0>和RX<7:0>)一起用于识别何时对8b/10b传输代码中包含的12个特殊符号之一进行编码。这些代码组串联在一起形成10bit的symbol。如Figure 4-2,ABCDE映射到abcdei,FGH映射到fghj。

注:在控制位的作用下,相同的8bit数据映射为不同的10bit符号;编码前的8bit数据可以称作character(字符),编码后的10 bit数据可以称作symbol(符号)。

Figure 4-2 Character to Symbol Mapping

4.2.1.1.1 Serialization and De-serialization of Data

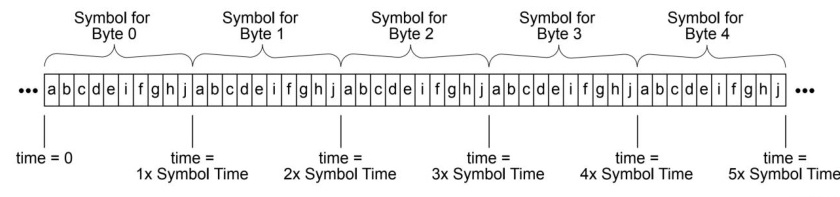

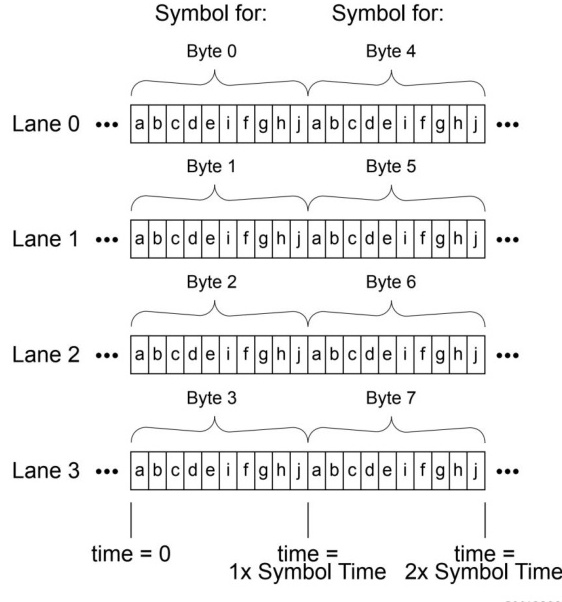

编码后的符号的比特流序如 Figure 4-3与 Figure 4-4。

OM13808

Figure 4-3 Bit Transmission Order on Physical Lanes-x1 Example

Figure 4-4 Bit Transmission Order on Physical Lanes-x4 Example

4.2.1.1.2 Special Symbols for Framing and Link Management(K code)

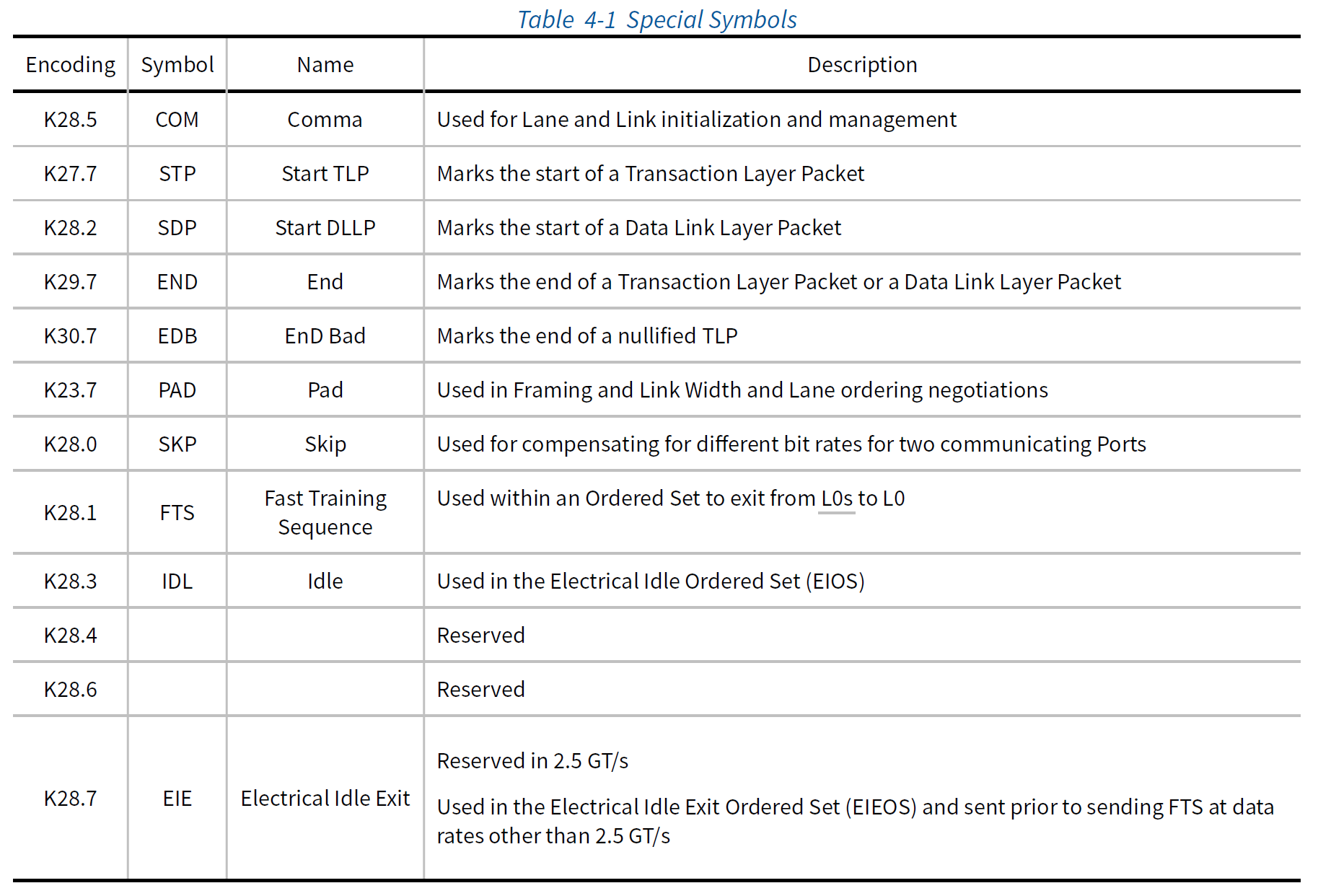

控制字符(Kcode)用于管理物理层数据传输,如Table 4-1。参考附录B的Table B-2获取这些控制字符的编码值。

Table 4-1 Special Symbols

4.2.1.1.3 8b/10b Decode Rules

8b/10b解码按照Appendix B进行。如果收到的符号与Appendix B中任一个都不对应,就是符号错误,会向链路层报告此错误,参阅Section 6.2的描述。

4.2.1.2 Framing and Application of Symbols to Lanes

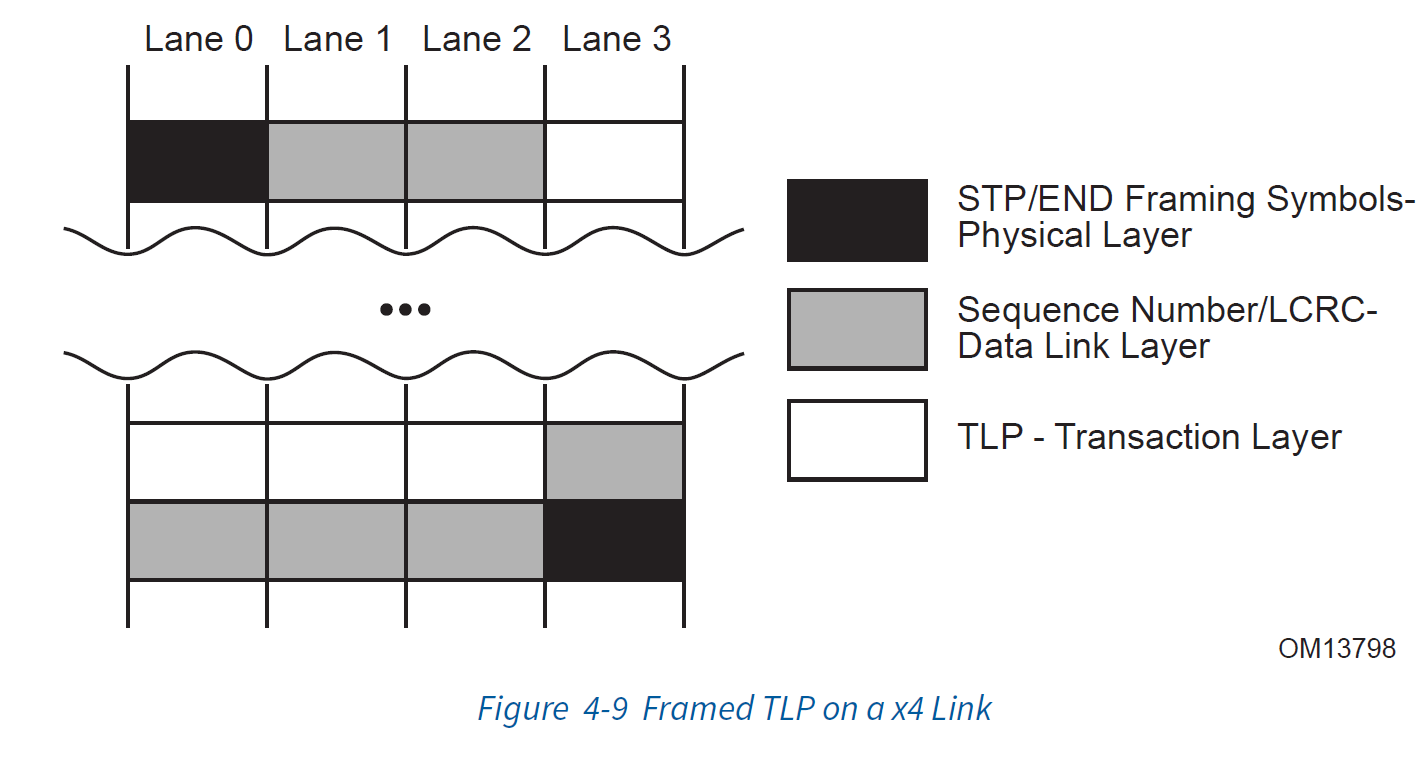

本节主要讲述物理层的组帧,以及将符号映射到各Lane上。

Symbol的作用有两个:一个是有序集的传输,用于管理物理层;一个是用于传输DLLP和TLP信息的Symbol。

K28.2“SDP”用于开始一个DLLP传输,K27.7“STP”用于开始一个TLP传输。K29.7“END”用于一个DLLP或一个TLP传输的结束。

当没有数据包信息或特殊的有序集正在传输时,发送器处于逻辑空闲状态。在这段时间内,必须传输空闲数据。空闲数据必须由0组成,该数据按照Section 4.2.1.3的规则加扰,并且是按照Section 4.2.1.1的规则采用与TLP和DLLP相同的数据编码方式进行8b/10b编码。同样,当接收方未接收到任何分组信息或特殊的有序集时,接收方处于逻辑空闲状态,并且应如上所述接收空闲数据。逻辑空闲期间,必须传输SKP有序集,参阅Section 4.2.7获取相关内容。

以下规则描述中的“place”的定义是指要求发送器将符号放入链路的对应Lane中。

-

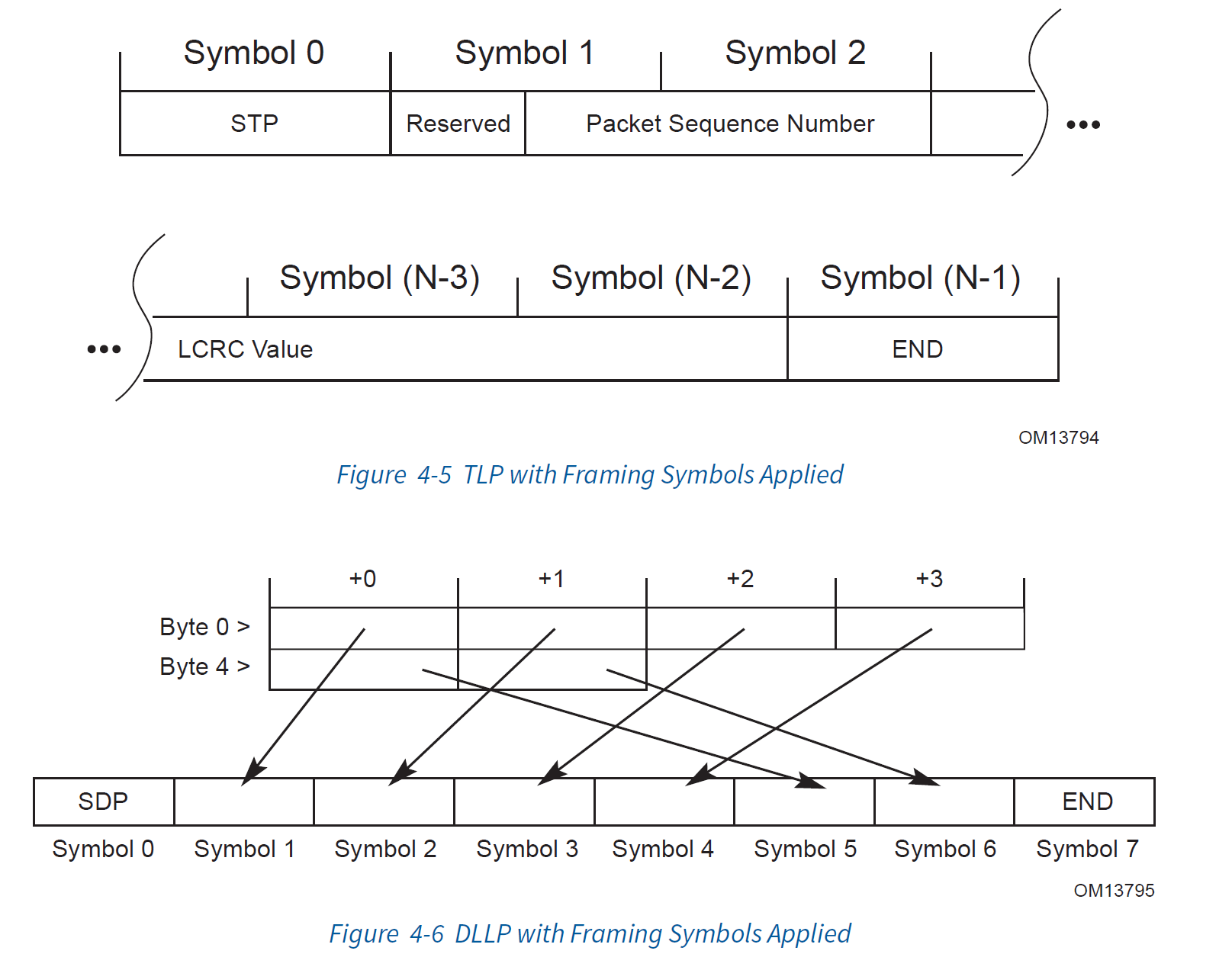

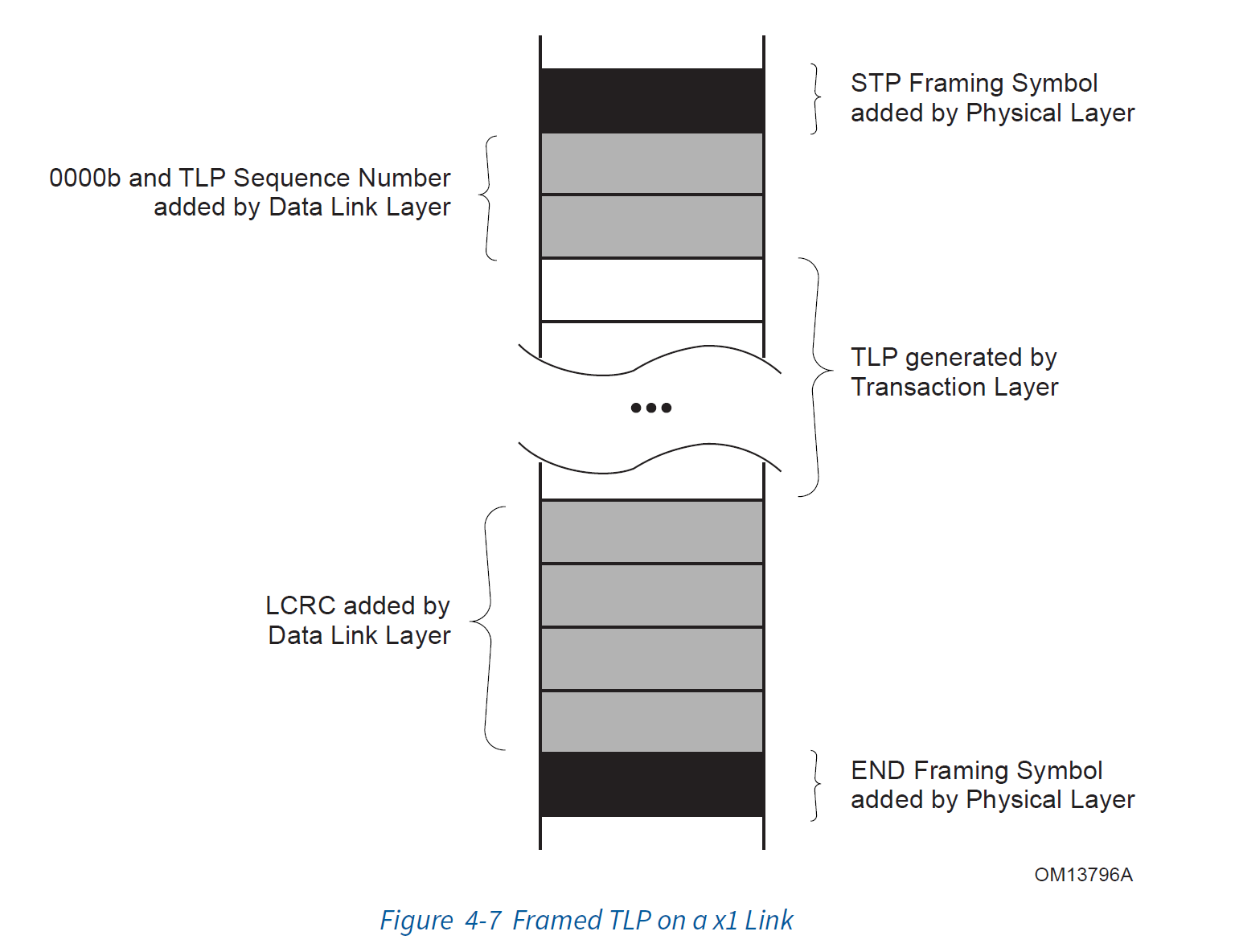

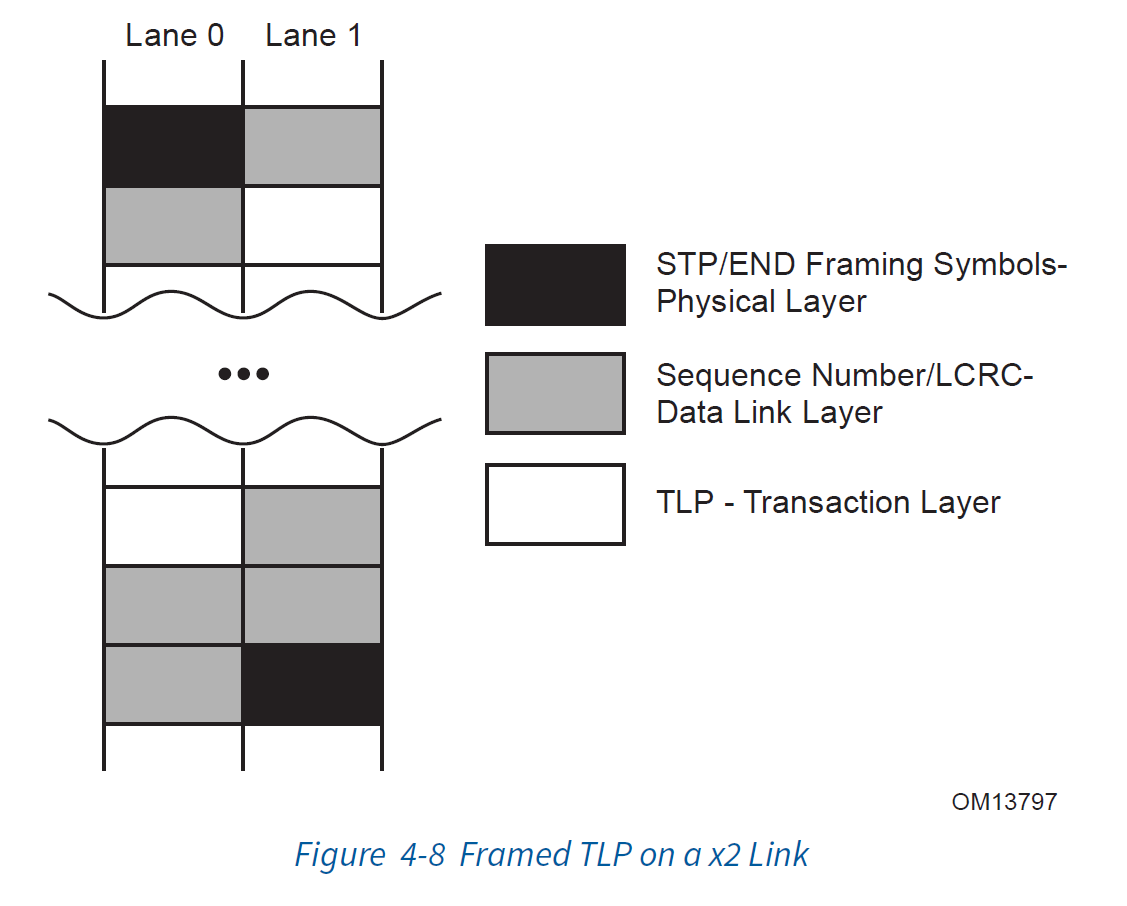

TLP必须以一个STP符号开始,以一个END(正常结束)符号或EDB(异常结束)符号结束,如Figure 4-5。

-

DLLP必须以一个SDP符号开始,以一个END符号结束,如Figure 4-6。

-

逻辑空闲状态与电气空闲状态不同,逻辑空闲状态传输Idle Symbol(00h)。

-

逻辑空闲状态时,发送器必须在所有Lane上发送Idle Symbol,参阅Section 4.2.1.3。

-

接收器必须忽略在逻辑空闲状态时接收到的信息。

-

-

对于宽度大于x1的链路,当从逻辑空闲链路条件开始发送TLP时,必须将STP符号放置在Lane0中。

-

对于宽度大于x1的链接,从逻辑空闲链接条件开始发送DLLP时,必须将SDP符号放置在Lane0中。

-

每个符号期间,STP符号在链接上放置的频率不得超过一次。

-

每个符号期间,SDP符号在链接上放置的频率不得超过一次。

-

只要满足上述规则,就可以允许TLP和DLLP的传输连续不断的进行。

-

一个STP符号和一个SDP符号可以在同一符号时间内放置在链路上。

- 宽于x4的链路可以在Lane 4*N中放置STP和SDP符号,其中N是一个正整数。例如,对于x8,可以将STP和SDP符号放置在Lane0和4中。对于x16,可以将STP和SDP符号放置在Lane 0、4、8或12中。

-

对于N为8或更大的xN链路,如果将END或EDB符号放在LaneK中,其中K不等于N-1,并且在LaneK+1中不跟STP或SDP符号(即,之后没有立即跟TLP或DLLP),则必须将PAD符号放置在Lane K+1到Lane N-1上。

- 例如,在x8链路上,如果将END或EDB放置在Lane3上,如果其后跟的不是STP或SDP,则必须将PAD放置在Lane 4至7中。

-

EDB符号用于标记无效TLP的结尾。有关EDB的用法,请参阅Section 3.6.2.1。

-

接收者可以选择是否检查违反了本部分的规则。这些检查是独立可选的(参阅Section 6.2.3.4)。如果实现此功能,则要报接收器错误,请参阅Section 6.2。

4.2.1.3 Data Scrambling

数据加扰在8b/10b编码之前进行。Scrambler的主要作用就是通过“加扰”的方法消减EMI噪声,所谓加扰是将源数据流与一个随机序列异或后,再发送出去。此时被发出的数据流也基本是伪随机的,从而降低了发送数据时产生的EMI噪声。

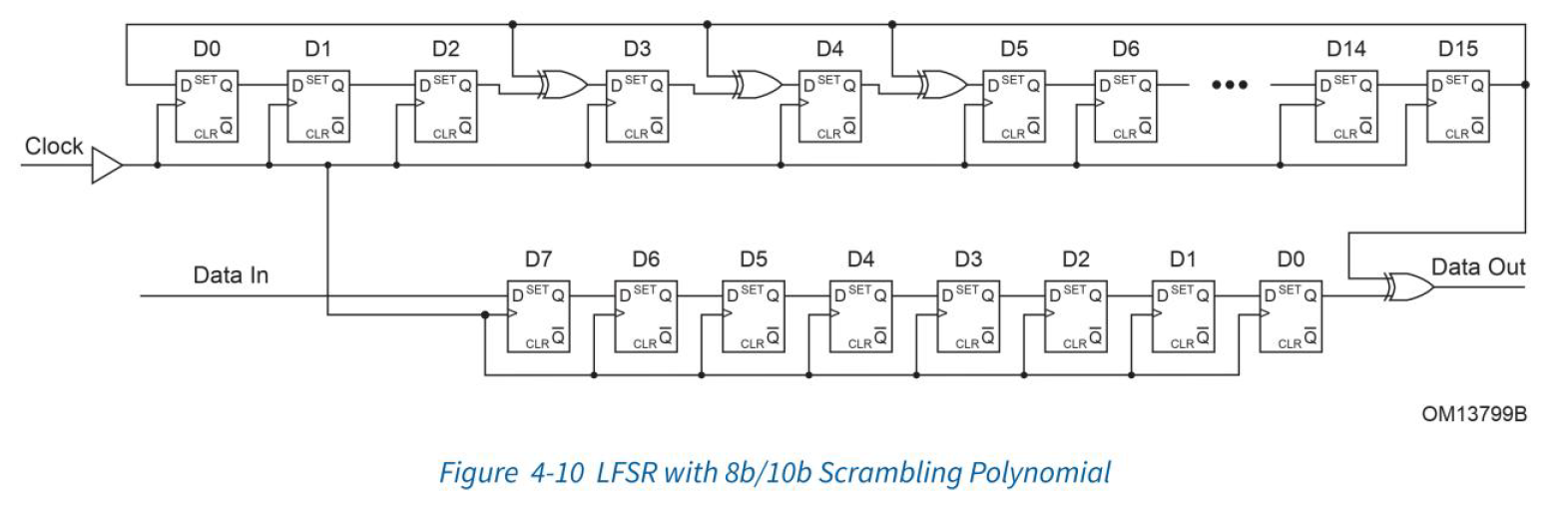

PCle定义的加扰功能可以通过多Lane链路上的一个或多个线性反馈移位寄存器(Linear Feedback Shift register,LFSR)来实现。如果每个链路发送端实现了多个LFSR,则这些LFSR必须协同工作,即在同一时刻每个LFSR生成的值相同(请参阅 Table 4-18,Lane-to-Lane Output Skew)。如果接收器中实现了多个LFSR,则它们也必须协同工作,即在同一时刻每个LFSR生成的值相同(请参阅Table 4-24,Lane-to-Lane Skew)。无论如何实现,LFSR都必须在逐个Lane的基础上与数据进行交互,就像在此链路中每个Lane所描述的那样,都有一个单独的 LFSR0。在发送侧,加扰应用于8b/10b编码之前的字符。在接收端,对8b/10b解码后的字符进行解扰。

LFSR如 Figure 4-10所示。通过将8位(D0-D7)字符与LFSR的16位(D0-D15)输出串行异或来执行加扰或解扰。LFSR的输出D15与要处理的数据的DO进行异或。然后,对LFSR和数据寄存器进行串行高级处理,并对D1至D7重复输出处理。数据进行异或后,LFSR将前进。LFSR实现多项式为:

G(X)=X16+X5+X4+X3+1G(X)=X16+X5+X4+X3+1G(X)=X16+X5+X4+X3+1

数据链路层用来通知物理层禁用加扰的机制和接口是特定于实现的,不在本规范的范围之内。

加扰规则如下:

- COM字符来指示初始化 LFSR

- 除SKP外,每个符号的LFSR值都提前了八个串行移位。

- 训练序列有序集(Training Sequence Ordered,如TS1和TS2)、一致性Pattern(参阅Section4.2.8)和修改后的一致性Pattern (Section 4.2.9)不需要加扰,其余所有数据符号(D codes)都要加扰。

- 所有的控制符号(K codes)都不需要加扰。

- LFSR的种子(DO-D15)的初始值为FFFFh。COM发出后,立即初始化发送侧的LFSR。每当COM在该链路的任何Lane上进入接收LFSR时,都会初始化接收端的 LFSR0

- 只能在配置结束时禁用加扰(请参阅Section 4.2.6.3.5)。

- 加扰不用于loopback。

- 在Detect状态下,加扰默认开启。

Figure 4-10 LFSR with 8b/10b Scrambling Polynomial

IMPLEMENTATION NOTE

Disabling Scrambling

禁用加扰旨在帮助简化测试和调试设备。精确 data pattern的控制在测试和调试环境中非常有用。由于在物理层复位了加扰,因此没有合理的方法通过软件可靠地控制数据转换的状态。因此,为了这些目的而在TS1和TS2有序集中添加 Disable Scrambling 字段。

数据链路层用来通知物理层禁用加扰的机制和/或接口是特定于实现的,超出了本规范的范围。

关于加扰的更多信息,参阅Appendix C,AppendixC给出了8b/10b加扰的c代码实现实例和128b/130b加扰的c代码实例。

4.2.2 Encoding for 8.0 GT/s and Higher Data Rates

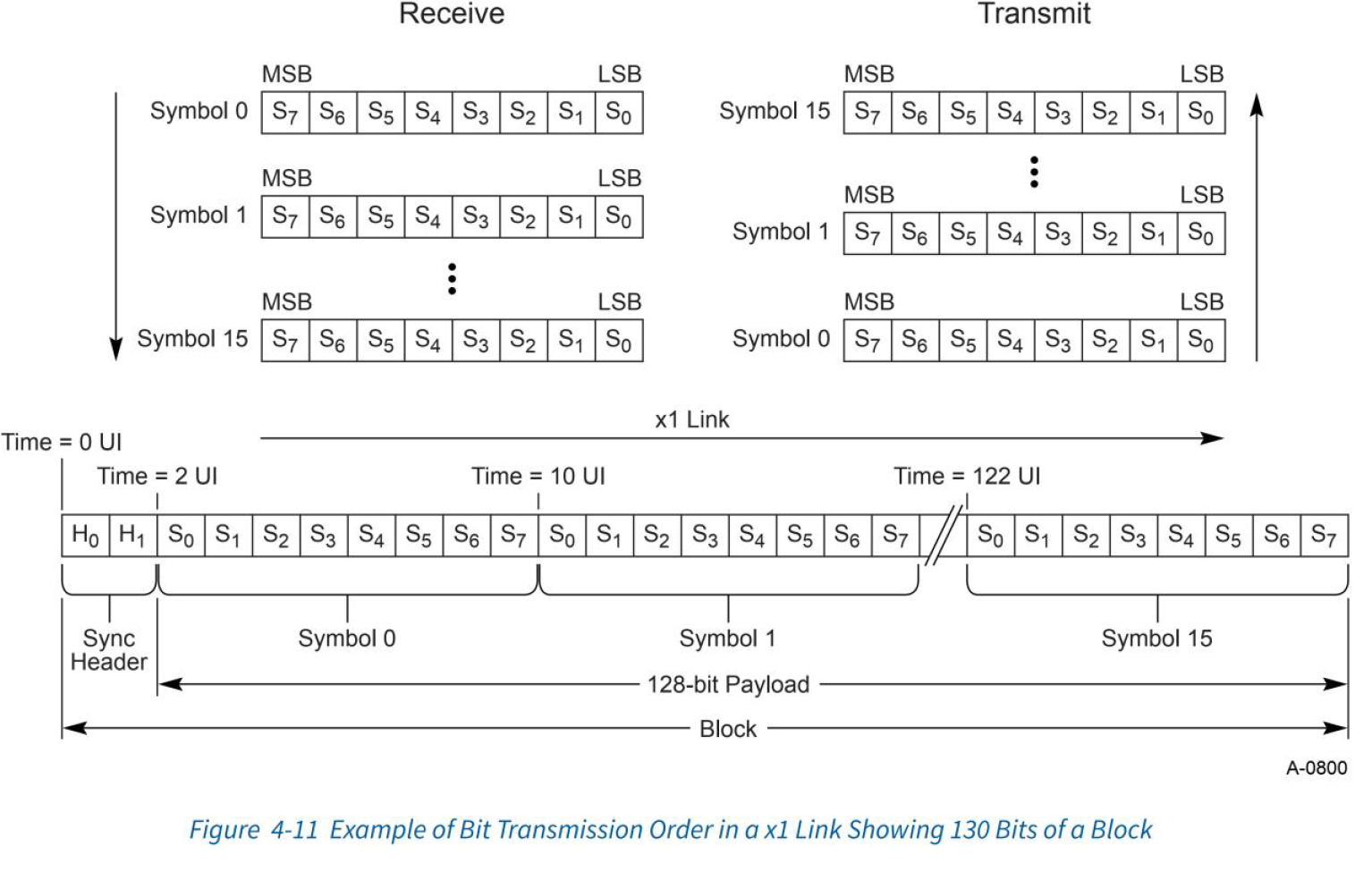

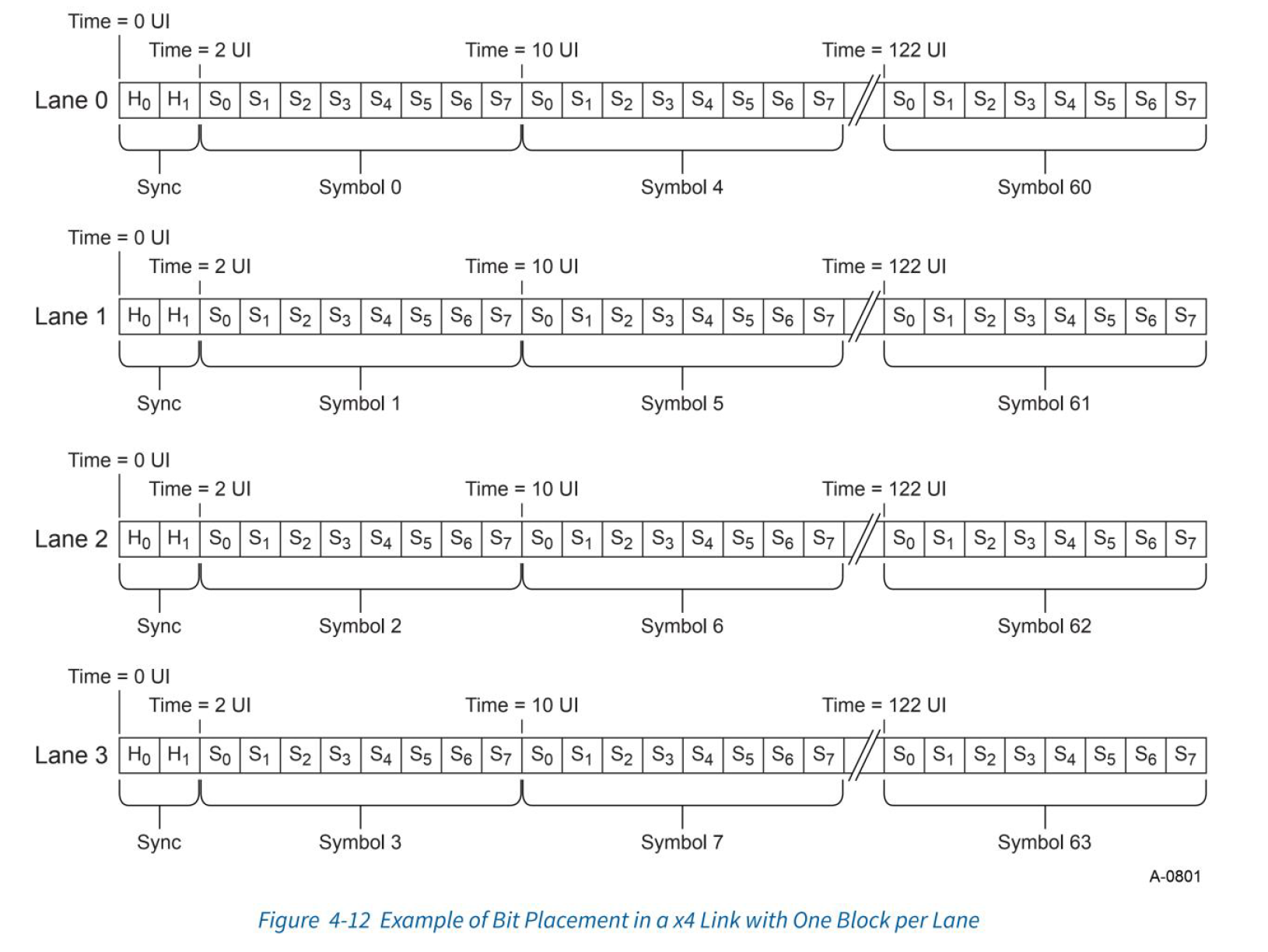

当PCI Express链路以8.0 GT/s或更高的数据速率运行时,它将使用本小节中描述的编码规则:128b/130b编码。为了向后兼容,链路最初按照Section 4.2.1节中所述使用8b/10b编码以2.5 GT/s的数据速率训练到L0,然后将数据速率更改为8.0GT/s或更高时,使用128b/130b编码。128b/130b编码是一种链路范围的打包机制,并且是具有加扰功能的每Lane的block编码机制。数据传输的基本实体是8位数据字符,称为符号,如Figure 4-11和Figure 4-12所示。

IMPLEMENTATION NOTE

Symbol in 128b/130b Encoding Scheme

在128b/130b编码方案中,Symbol定义为一个字节长度,类似于8b/10b编码的10-bit Symbol。

4.2.2.1 Lane Level Encoding

物理层使用每Lane的block编码机制。每个block均包含一个2位同步头(Sync Header)和一个有效负载。有效的同步头编码有两种:10b和01b。同步头定义了该block包含的有效载荷的类型。

同步头为10b表示数据块(Data block)。每个数据块具有128bit有效载荷,因而块大小为130bit。有效负载是Section 4.2.2.3中描述的数据流。

同步头为01b表示有序集块(Order Set Block)。每个有序集块都有一个128bit有效载荷,因此块大小为130bit,但SKP有序集可以是可变长度的。

多Lane链路的所有Lane必须同时发送具有相同同步头的块,但在Polling.Compliance 中传输 Jitter Measurement Pattern时除外。

比特发送顺序如下。用 “H1H0"表示的Sync Header放置在以"H0"开头并以"H1"结尾的Lane 上。用“S7S6S5S4S3S2S1S0"表示的Symbol 放置在以"S0"开头并以"S7””结尾的Lane上。在显示时间刻度的图中,比特表示传输顺序。在布局图中,比特以低字节序格式排列,这与本规范其他章节中的数据包布局图一致。

4.2.2.2 Ordered Set Blocks

一个Ordered Set Block包含一个同步头,后跟一个有序集。多通道链路的所有Lane必须同时传输相同的有序集。有序集的第一个符号定义有序集的类型。有序集在Section 4.2.4和Section 4.2.7中有详细描述。

4.2.2.2.1 Block Alignment

在链路训练期间,130bit的Electrical Idle Exit Ordered Set (EIEOS)是接收器用来确定Block Sync Headers的唯一比特流数据。从概念上讲,接收端可以处于Block Alignment的三个不同阶段:Unaligned,Aligned和 Locked。定义这些阶段是为了说明所需的行为,但并不意味着要这样实现。

Unaligned Phase:接收器经过一段时间的电气空闲后进入此阶段,例如,当数据速率更改为使用128b/130b编码的速率时,或者当它们退出低功耗链路状态时,或者在链路定向时。在此阶段,接收器检测接收到的比特流中的EIEOS bit pattern。当检测到一个时,他们调整其对齐方式并进入Aligned Phase。

Aligned Phase:接收器检测接收到的EIEOS比特流和接收到的Start of Data Stream(SDS)有序集的Block。如果在与当前对齐方式不匹配的对齐方式上检测到EIEOS比特流,则接收方必须将其对齐方式调整为新接收到的EIEOS比特流。如果接收到SDS有序集,则接收器进入Locked Phase。如果接收到未定义的同步头(00b或11b),则允许接收端返回Unaligned Phase。

Locked Phase:在此阶段,接收方不得调整其块对齐方式。希望在SDS有序集之后接收数据块,并且调整块对齐方式会干扰这些块的处理。如果接收到未定义的同步头,则接收器必须返回到Unaligned Phase 或Aligned Phase。

IMPLEMENTATION NOTE

Detection of Loss of Block Alignment

在训练序列中发送的EIEOS和TS有序集的序列将导致未对准的接收器检测到未定义的Sync Header。

其他要求:

- 在对齐或锁定阶段,接收器必须在收到SKP有序集时根据需要调整其对齐方式。有关SKP有序集的更多信息,请参见Section 4.2.7。

- 从任何LTSSM状态转换到Recovery状态之后,接收器必须忽略所有收到的TS有序集,直到收到EIEOS。从概念上讲,接收EIEOS可以验证接收器的对齐方式,并允许进行TS有序集处理。如果收到的EIEOS发起了从LO到Recovery的LTSSM转换,则允许接收器处理跟随EIEOS的任何TS有序集,或者忽略它们,直到收到另一个EIEOS。

- ·只要停止数据流处理,就可以将接收方从Locked Phase 定向到Unaligned Phase或 Aligned Phase。有关数据流要求的更多信息,请参见Section 4.2.2.3。

- Loopback Masters :在Loopback.Entry状态下,Master必须能够调整接收器的块对齐方式以接收EIEOS比特流。进入Loopback.Active状态时,允许主机发送EIEOS并将其接收方的块对齐方式调整为环回比特流。

- Loopback Slaves:在进入Loopback.Entry时,Slave必须能够调整接收器的块对齐方式以接收EIEOS比特流。Slave处于Loopback.Active时,Slave不得调整其接收方的块对齐方式。从概念上讲,当从设备开始环回接收到的bite流时,将接收器定向到Locked Phase。

4.2.2.3 Data Blocks

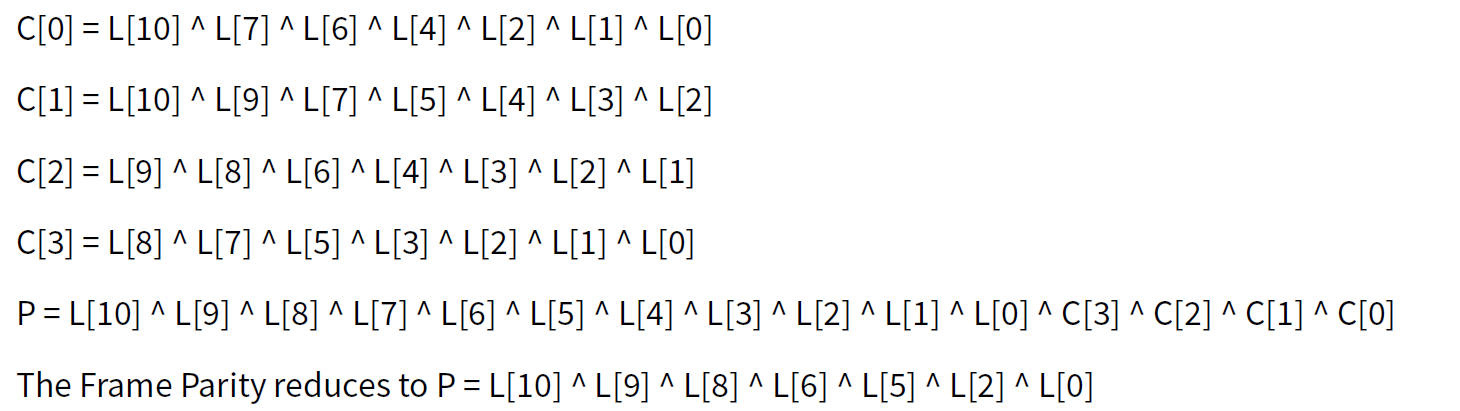

Data Block的有效载荷是符号流(Symbol Stream),定义为“Data Stream”,它由Framing Tokens,TLP和DLLP组成。数据流的每个符号都放置在链路的单个Lane中,并且符号流在链路的所有Lane上分布,并跨越Block边界。

数据流从紧随SDS有序集的Data Block的第一个符号开始。当检测到帧错误时,或者以除SKP有序集以外的有序集之前的数据块的最后一个符号时,该数据流结束。数据流中出现的SKP有序集具有特定要求,如以下各节所述。

4.2.2.3.1 Framing Tokens

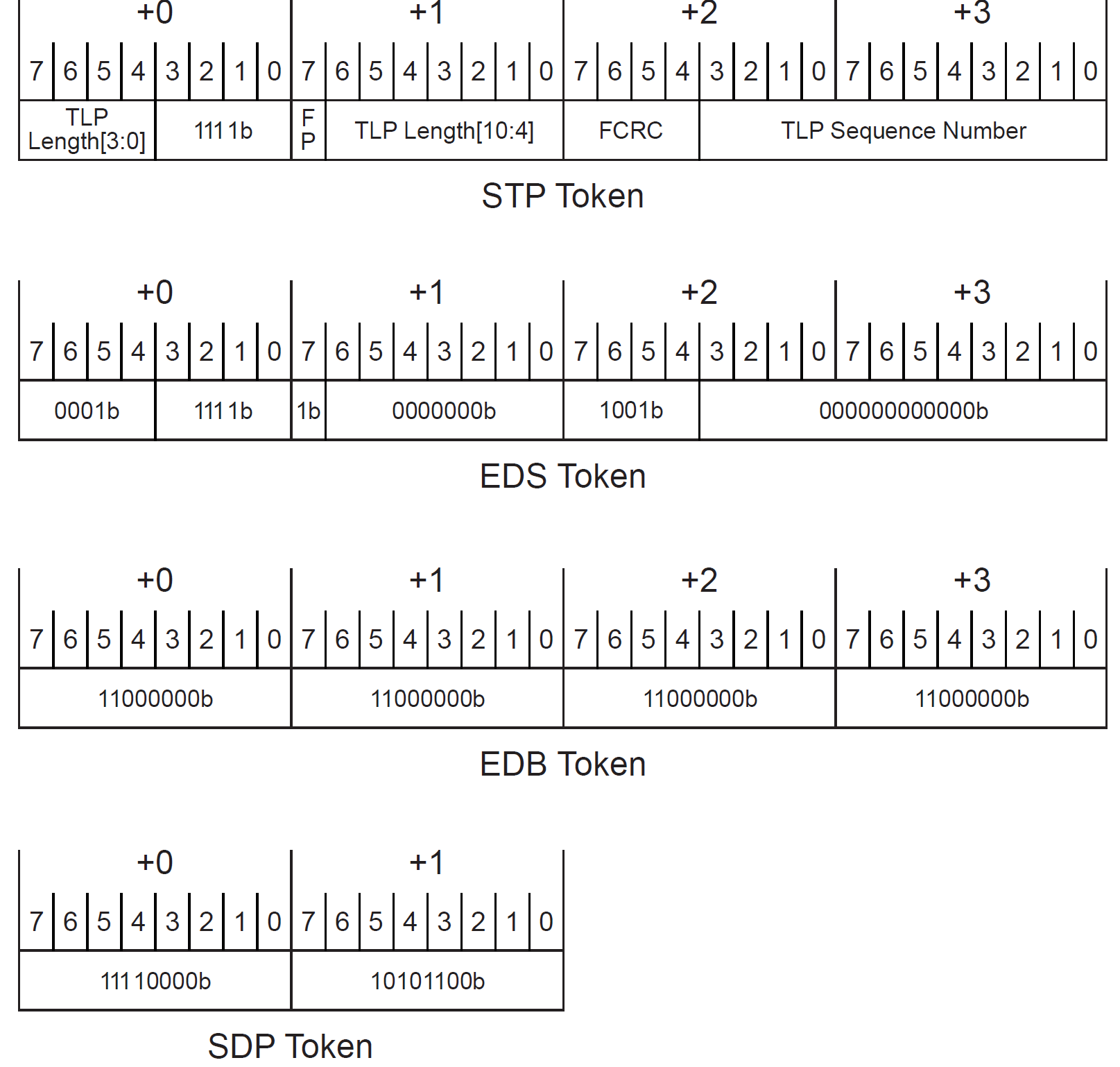

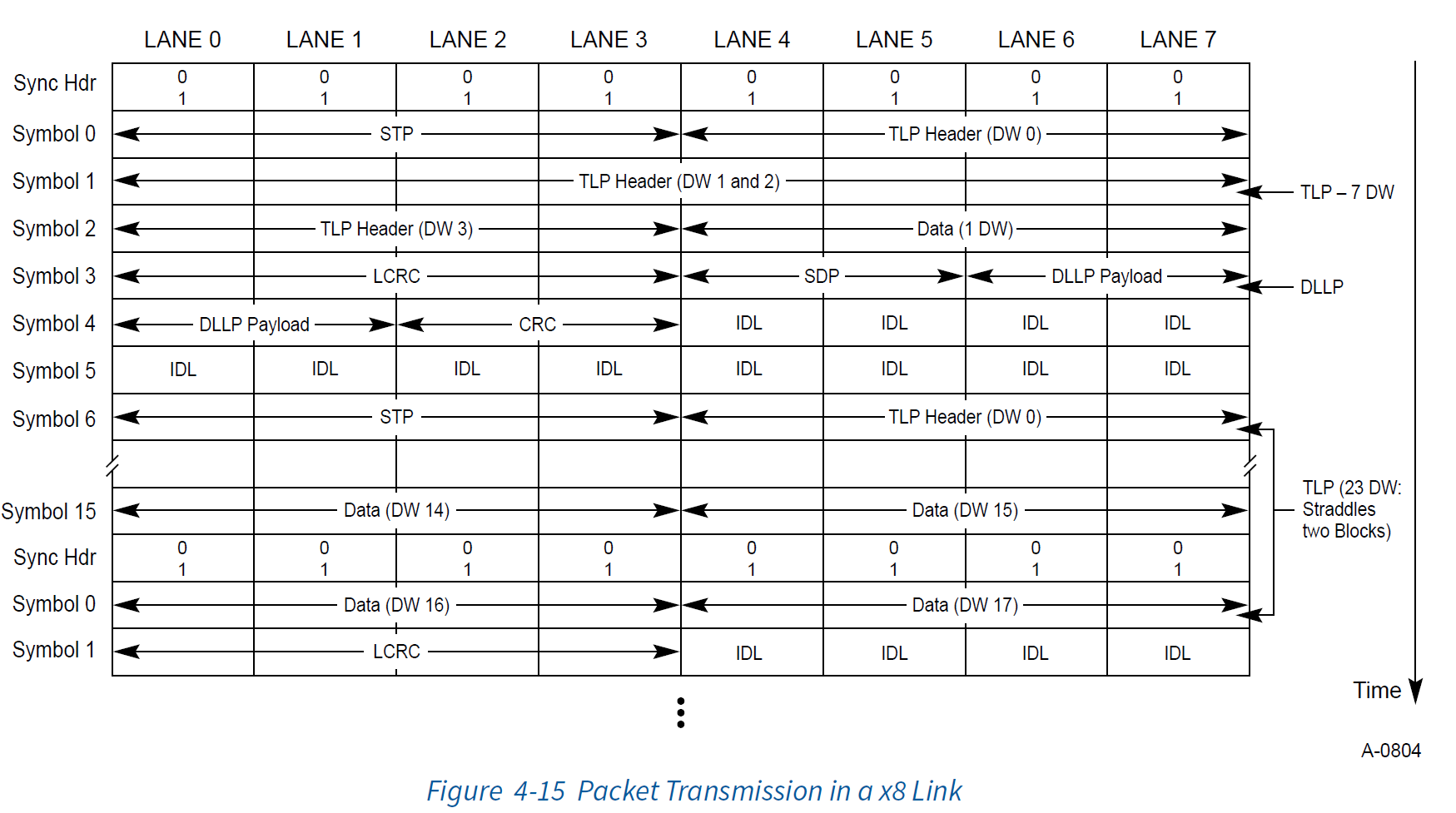

Table 4-2 中显示了物理层使用的Framing Tokens。每个Framing Tokens 指定或暗示与该Tokens相关联的符号的数量,并因此指定下一个Framing Tokens的位置。Figure 4-15显示了在x8链路上传输的TLP,DLLP和IDL的示例。

数据流的第一个Framing Token始终位于数据流的第一个数据块的Lane 0的Symbol0中。在本章的其余部分,术语Framing Token 和Token可互换使用。

Table 4-2 Framing Token Encoding

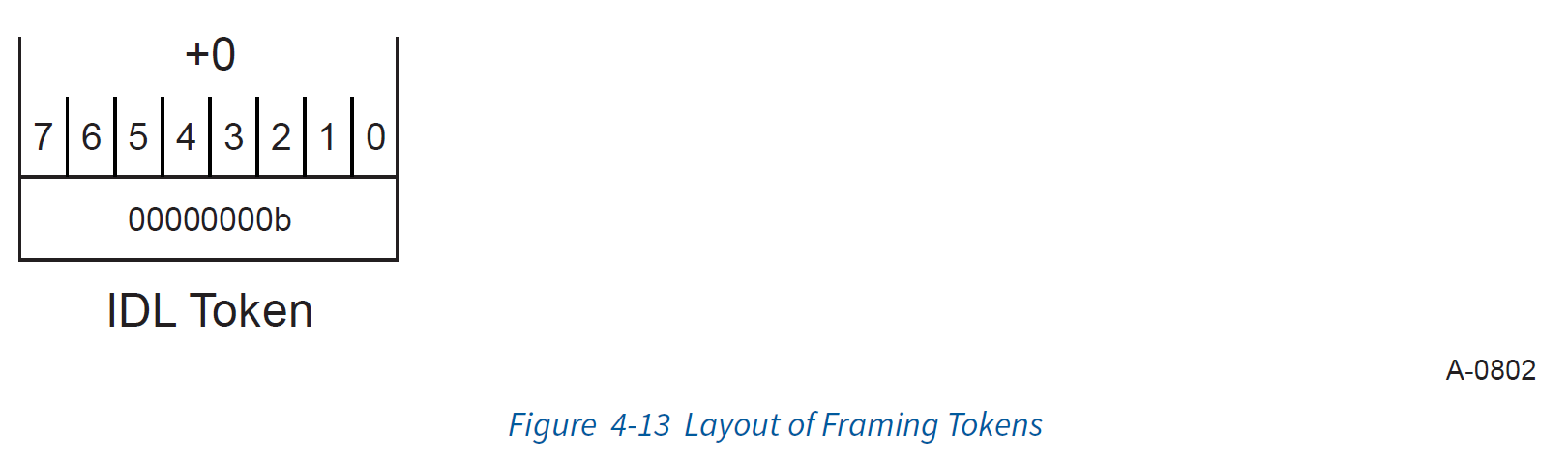

物理层DLLP布局如Figure 4-14所示。Symbol 0和1是SDP Token,Symbol 2至7是数据链路层DLLP信息。

物理层的TLP布局如Figure 4-14所示。详细的信息要结合Figure 4-13一起理解。TLP length的单位是DW,包括Framing Tokens、TLP Prefixes(如果有)、TLP Header、TLP data payload(如果有)、TLP digest(如果有)以及TLP LCRC等信息。例如,如果TLP 具有一个3DW头,1个DW数据有效载荷,并且不包含TLP摘要,则TLP length字段值为6:它包括1(Framing Token)+0(TLP 前缀)+3(TLP头)+1(TLP数据有效负载)+0(TLP摘要)+1(TLP LCRC)。如果同-TLP包含TLP摘要,则TLP长度字段值将为7。 当TLP无效时,EDB令牌被视为TLP的扩展,但不包括在TLP长度字段的计算中。

Figure 4-14 TLP and DLLP Layout

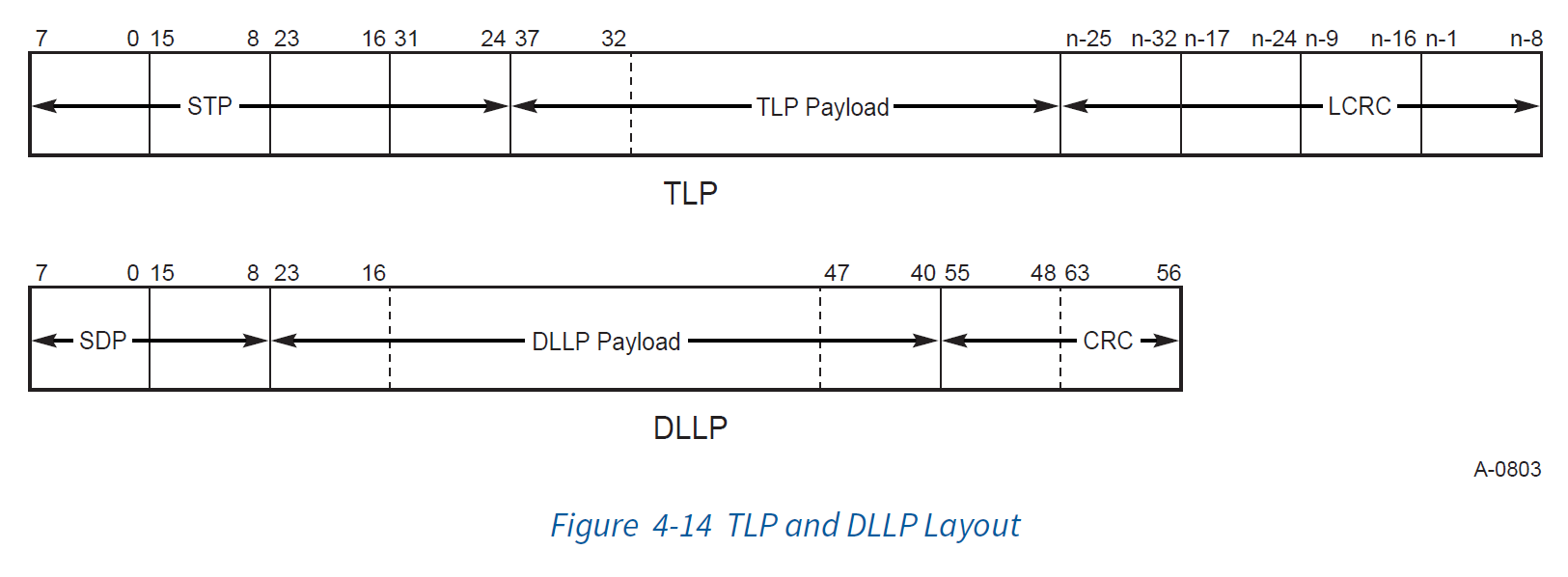

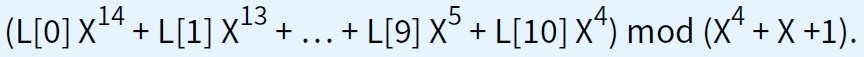

TLP length 字段受4位CRC(Frame CRC,即上述FCRC字段)保护,偶校验位(Frame Parity,即上述FP字段)保护TLP长度和FCRC字段。FCRC和FP计算如下:

在上述等式中,TLP长度字段表示为L[10:0],其中L[0]是最低有效位,L[10]是最高有效位。发送器在发送之前计算 Frame CRC 和Frame Parity。接收器必须使用与发送器相同的算法来计算Frame CRC和Frame Parity,然后将计算出的值与接收到的值进行比较。

STP Token的TLP length 字段值不为1。如果接收到的符号序列与TLP length字段值为1的STP Token格式匹配,则将评估这些符号以确定它们是否与EDS Token匹配。

IMPLEMENTATION NOTE

Frame CRC and Frame Parity

Frame CRC有效地计算为

应该注意的是,X4+X+1是一个原始多项式,CRC可以检测到两个误码。Frame Parity 字段可以检测到奇数个误码。因此,Frame CRC和Frame Parity 共同保证了 TLP length 字段的三比特错误检测。必须注意的是,即使在简化的帧奇偶方程中,并非所有项都存在,它仍然保持了检测奇数位错误的特性。计算中仅使用偶数个CRC项中存在的那些TLP长度字段位。

请注意,对于TLP,在计算LCRC之前,数据链路层会在TLP序列号字段前添加4个保留位(0000b)。当使用128b/130b编码时,这些保留位未明确发送,并且接收器在计算LCRC时假定接收到的4位为0000b。

TLP length 字段大于1535的数据包是PMUX数据包。对于此类数据包,实际数据包长度的计算方法有所不同,STP Token中的TLP序列号字段包含其他信息,并且使用不同的规则计算链路 CRC0 有关详细信息,请参见Appendix G。

TLP length 字段介于1152和1535(含)之间的的数据包保留以供将来标准化。

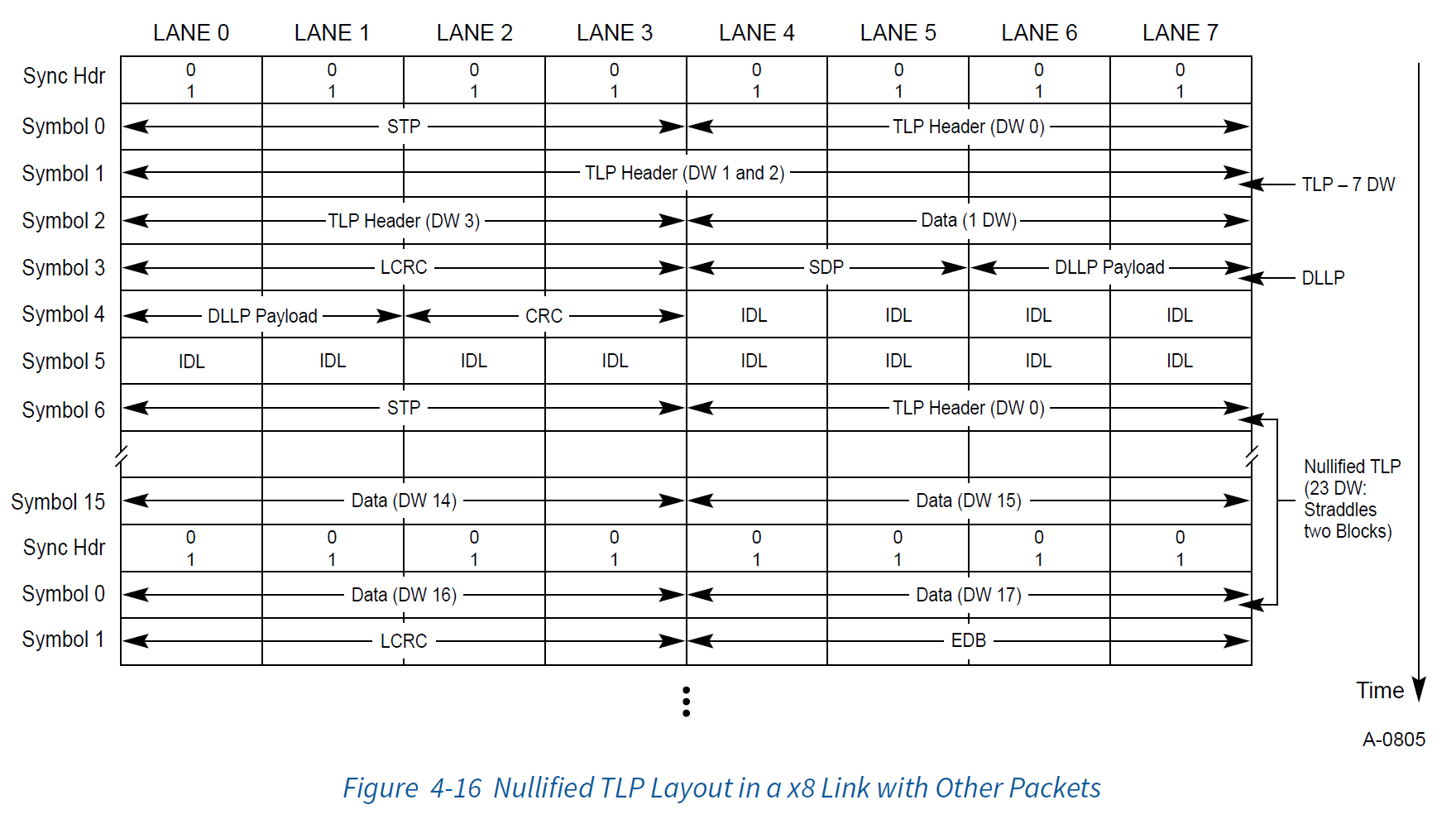

发射机必须发送由STP Frame Token的TLP length 字段指定个数的 DW∘ 使用128b/130b编码时,即使TLP无效,也不会将它截断。Figure 4-16显示了无效的23 DW TLP的示例。

Figure 4-16 Nullified TLP Layout in a x8 Link with Other Packets

Figure 4-17显示了TLP,DLLP,IDL和EDS令牌以及后跟SKP有序集的示例。SKP有序集在Section 4.2.7.2中定义。

Figure 4-17 SKP Ordered Set of Length 66-bit in a x8 Link

4.2.2.3.2 Transmitter Framing Requirements

发送端的Data Stream需要遵循以下规则。

-

为了发送一个TLP:

-

发送STP Token,然后立即发送数据链路层提供的完整TLP信息。

-

即使TLP无效,也必须发送STP Token中TLP length字段所指定的TLP的所有DW。

-

如果TLP为空,则必须在TLP之后立即发送EDB Token。TLP的最后一个符号和EDB Token的第一个符号之间不得有别的符号。考虑到EDB Token的原理,一个无效的TLP的STP Token的TLP length字段的值不能进行调整。

-

每个Symbol Time 发送STP Token的频率不得超过一次。

-

-

为了发送一个DLLP:

-

发送SDP令牌,然后立即发送数据链路层提供的完整DLLP信息。

-

必须传输DLLP的所有的6个符号。

-

每个Symbol Time发送SDP令牌的频率不得超过一次。

-

-

为了在Data Stream中发送一个SKP有序集:

-

在当前数据块的最后一个DW中发送EDS Token。例如,对于x1链路,Token在块的Symbol Time为12-15的Lane0上传输,对于x16链路在块的Symbol Time为15的Lane 12-15上传输。

-

在当前数据块之后发送SKP有序集。

-

在SKP有序集之后发送数据块。数据流从数据块的第一个符号恢复。如果计划发送多个SKP有序集,则每个SKP有序集必须在其后带有一个EDS Token的数据块。

-

-

如果要结束一个Data Stream:

- 在当前数据块的最后一个DW中发送EDS Token,然后在下一个块中发送EIOS或EIEOS。对于LTSSM电源管理状态转换,需要发送EIOS;对于所有其他情况需要发送EIEOS。例如,对于x1链路,Token在块的Symbol Time为12-15的Lane 0上传输,对于x16链路,在块的Symbol Time为15的Lane 12-15上传输。

-

不传输TLP,DLLP或其他Frame Tokens时,必须在所有Lane上传输IDL Token。

-

对于多Lane的链路:

-

传输一个IDL Token后,必须在之后的Symbol Time的Lane 0中传输下一个STP或SDP Token的第一个符号。可以在相同的Symbol Time内在IDL Token之后发送EDS Token,因为它必须在块的最后DW中发送。

-

对于N为8或更大的xN链路,如果EDB Token、TLP或DLLP结束于Lane K,其中K不等于N-1,并且其后没有STP,SDP或EDB Token 位于Lane K+1中,那么IDL Token 必须放在Lane K+1到N-1中。例如,在x8链路上,如果TLP或DLLP在Lane 3中结束,则必须将IDL Token放在Lane 4至Lane7中。EDS Token是此要求的例外,可以在IDL Token之后传输。

-

Tokens、TLP和DLLP允许相继出现,以便可以在同一Symbol

Time内传输一个以上的Token,只要它们的传输符合本节所述的其他要求即可。- 宽度大于x4的链路可以将Token放置在Lane 4*N上,其中N是一个正整数。例如,可以将Token放置在x8链路的Lane 0和Lane4中,并且可以将Token放置在x16链路的Lane 0、Lane 4、Lane 8或Lane 12中。

-