PI 思维升级 解密电容器的选择与布局策略,带您追求极致平坦的电源阻抗

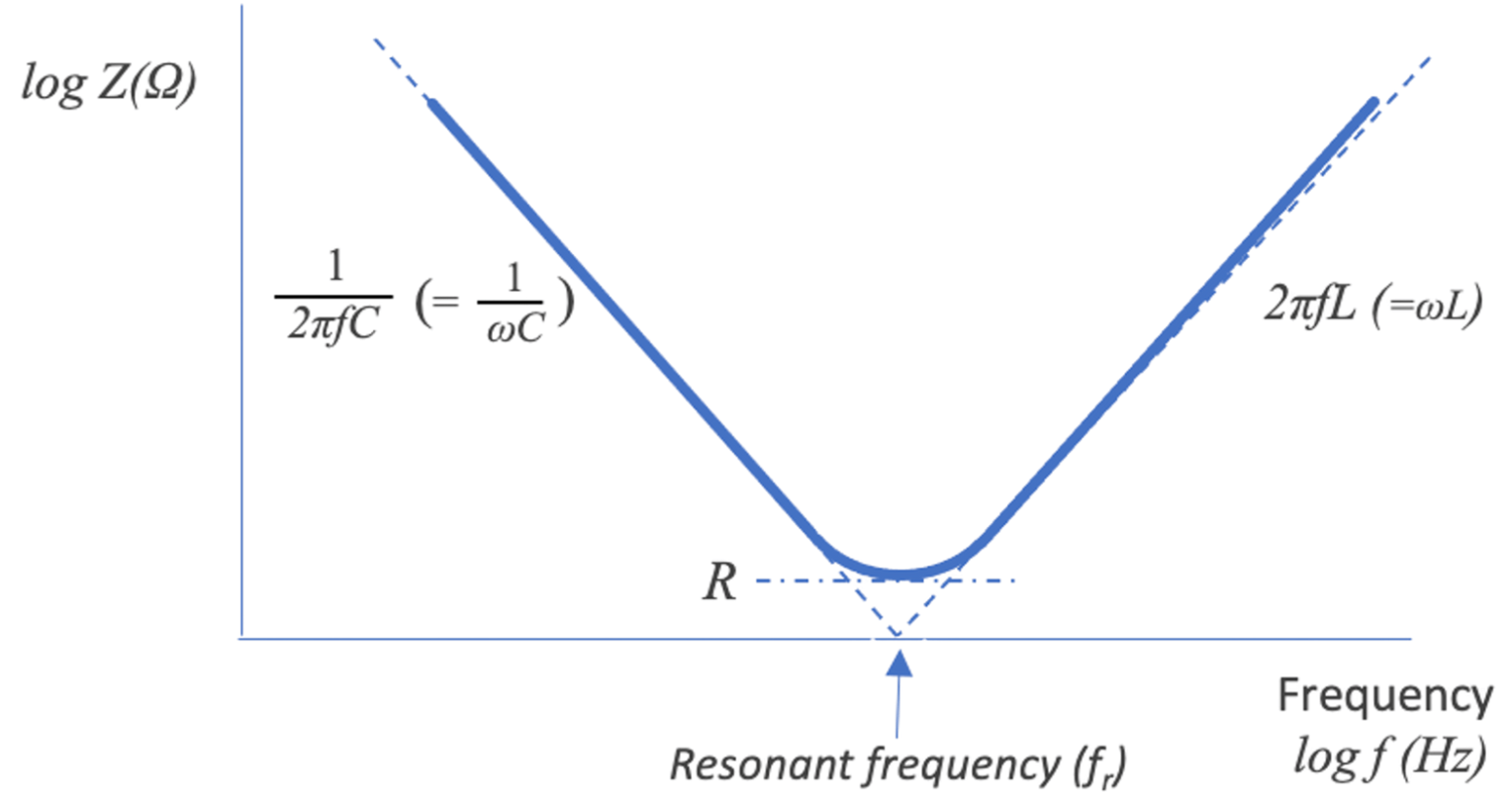

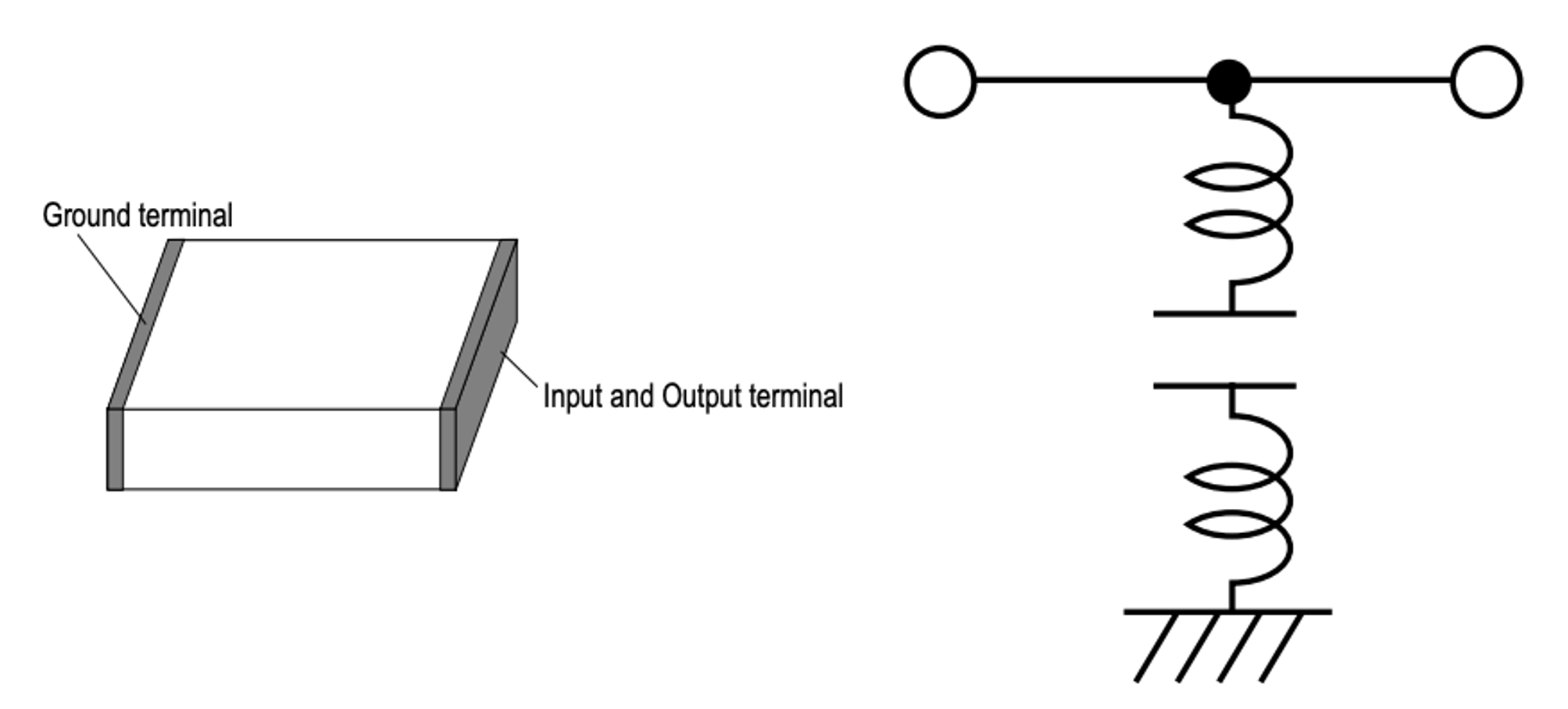

电容器的阻抗模型,可以看到就是个串联谐振,谐振频率以下由电容器本身的电容所贡献,谐振频率以上则由电容器的寄生电感与“路径的ESL”所贡献,谐振频率时的阻抗则为直流电阻DCR。

高频带有低阻抗的特性,电容对于拉低系统阻抗是很有帮助的,透过将高频噪声导移开主要路径,降低噪声。 对系统设计的人来说,我们没办法改变电容器本身的特性,也就是说电容器的阻抗是没办法控制的,可是我们可以尽量让电容器在系统上运行时的阻抗不要变得更差,这可以透过以下几点来改善:

- 电容器的摆放位置

- 解耦芯片与电容器之间的路径改善

- 容值选择与搭配

- 不同类型的MLCC

电容器的摆放位置

电容器要放的离芯片越近越好,进而改善路径的ESL,改善高频阻抗,这点无庸置疑!

(不过... 前提是芯片跟电容器中间的路径不要乱做加工...)

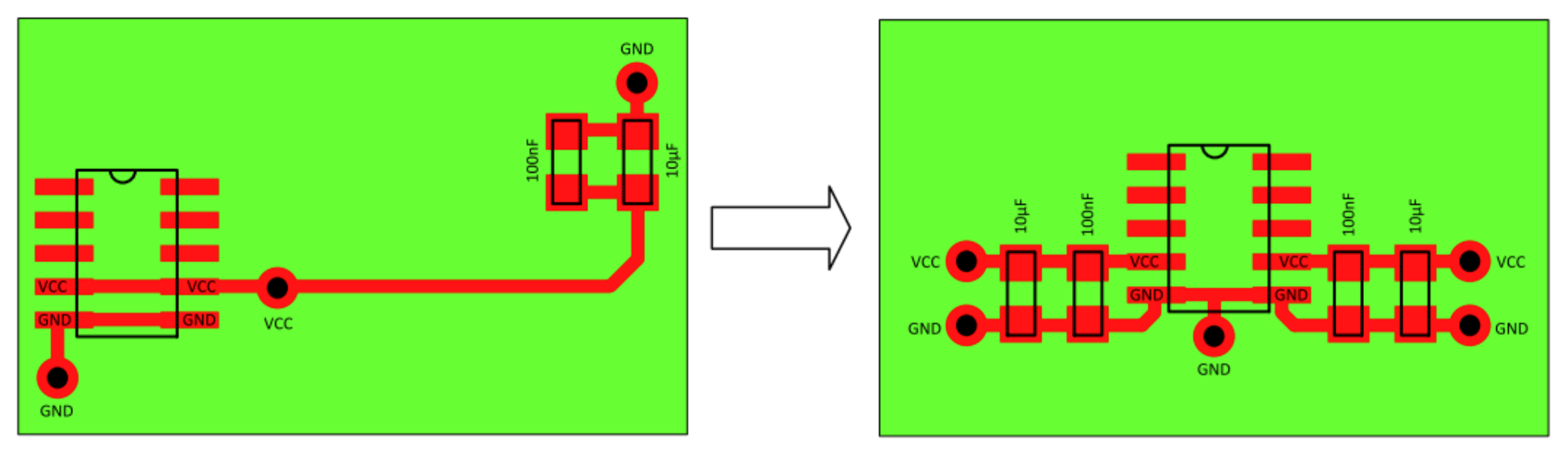

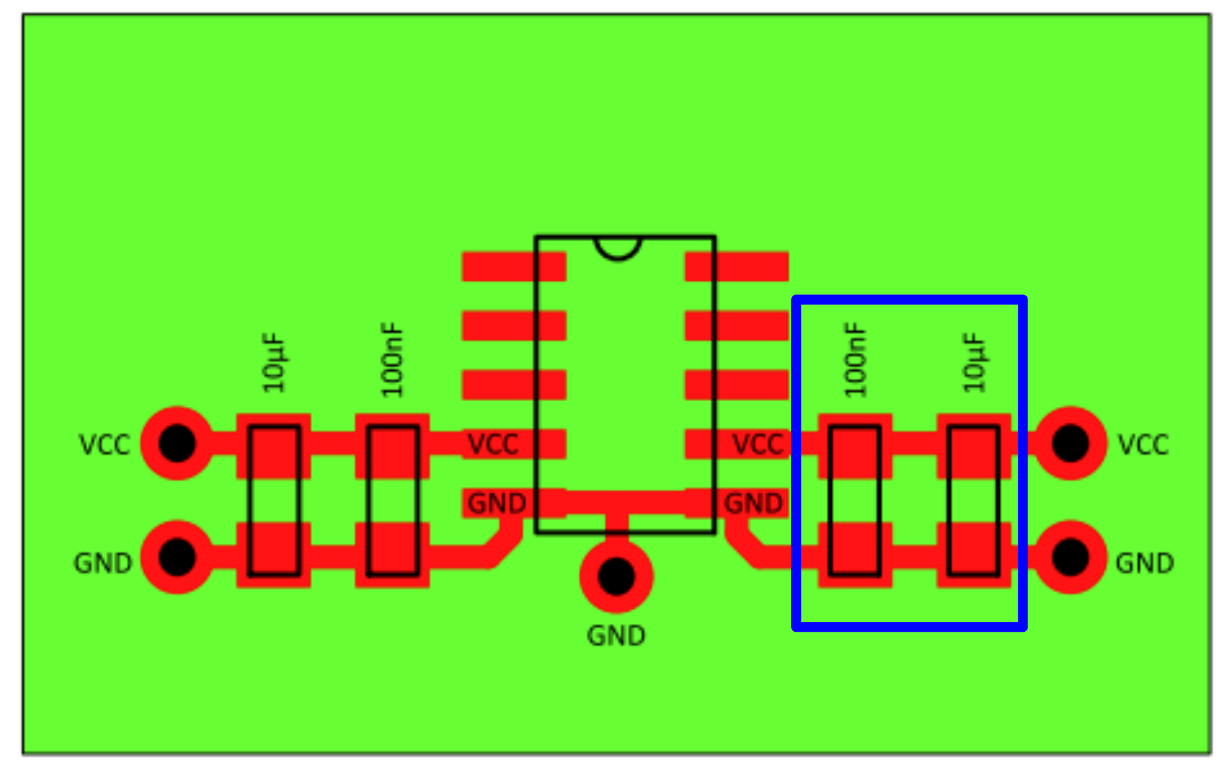

通常,容值较大的电容器,会有较大的解耦范围,换句话说,由于电容所储存的电荷较多,可以对较远的芯片做解耦合。 所以当有不同容值的电容对同一个Power Rail解耦合时,大电容值的要摆远一点,小电容值的摆进一点,当然都塞的离芯片越近越好。

解耦芯片与电容器之间的路径改善

缩短电容器与芯片间的路径长度是首要任务,这绝对可以大大减少寄生电感。

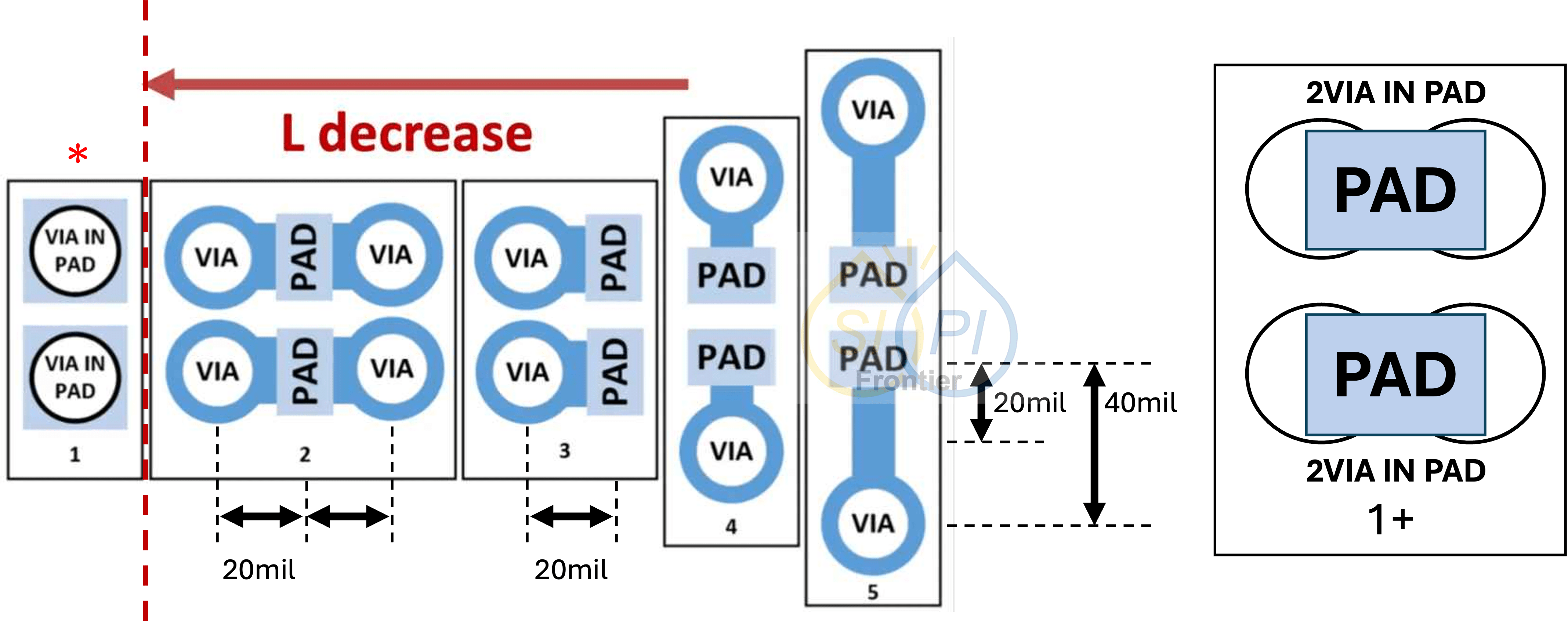

当然路径上少不了过孔Via,除了将走线缩短,还可以透过将Power/Ground Via两两靠近,以减少回路电感!

电容器的容值选择与搭配

一般传统上的认知,电容选择有两种派系:

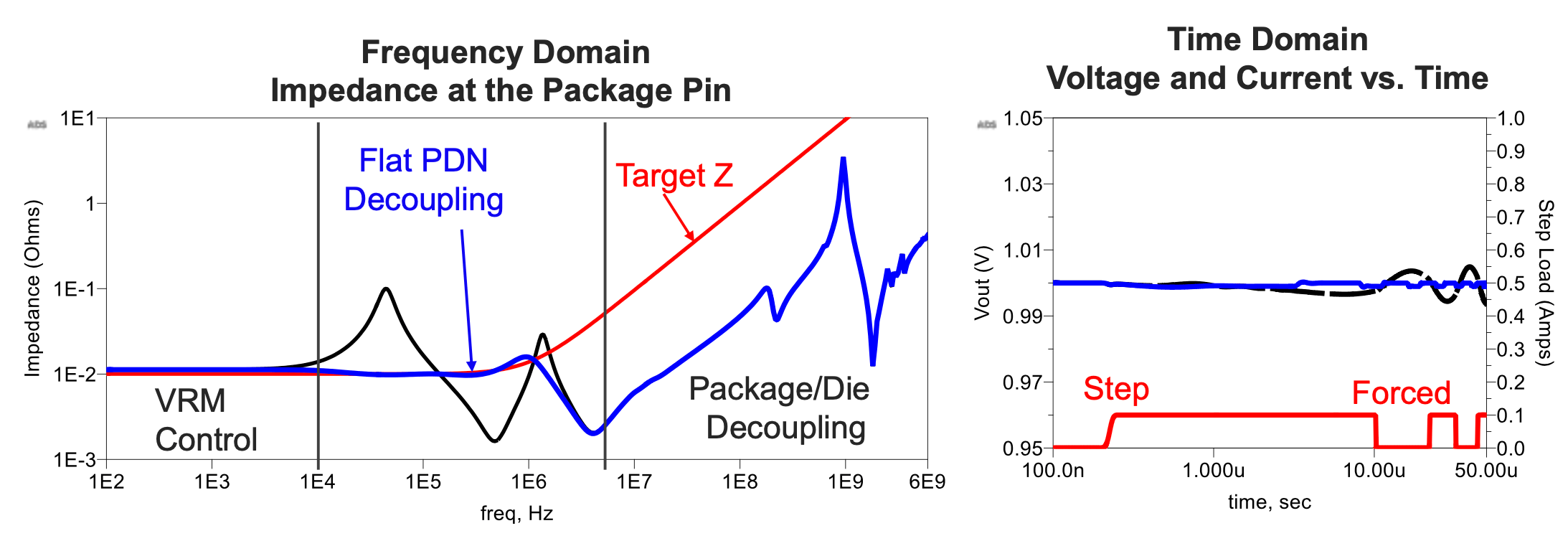

- 选择3种容值,每个容值互相差10倍,例如0.1uF、1uF、10uF的安排或是0.47uF、4.7uF、47uF

- 所有电容都使用相同的容值

事实上,都不是最佳解,又或是说没有最佳解! (很遗憾,SI/PI产业真的没有所谓最好的方法,总是It depends! )

理论上我们追求的是一个平坦的阻抗曲线(我知道看到这里你会觉得我们在鬼扯,因为真的很难搞,但还是请看下去),阻抗平坦代表呈现的是一个等效的电阻效应,表示电压在这个平坦的频段内,不管高频还是低频,只会有相等压降,换句话说就不会有Ripple。

(SI领域其实也是这个目标,知道的就知道,不知道的... 以后再写文章描述了,或是寄信来问我们啰~)

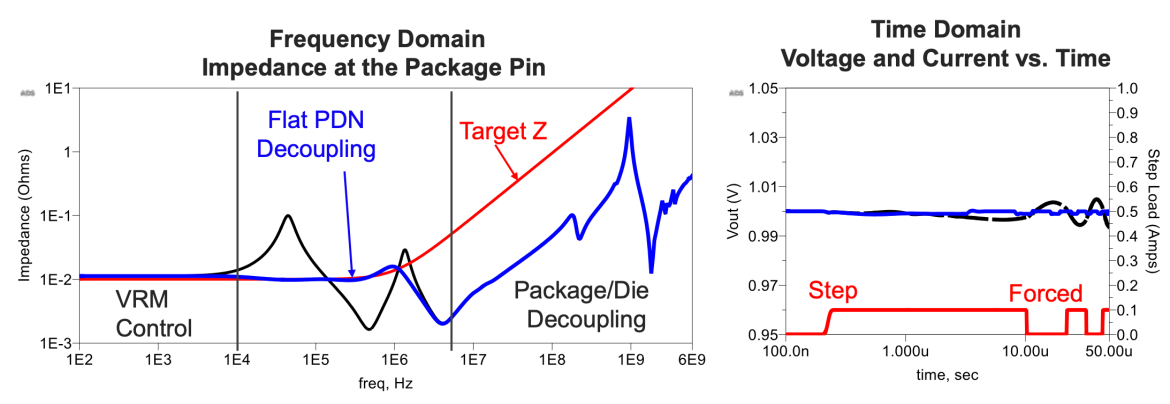

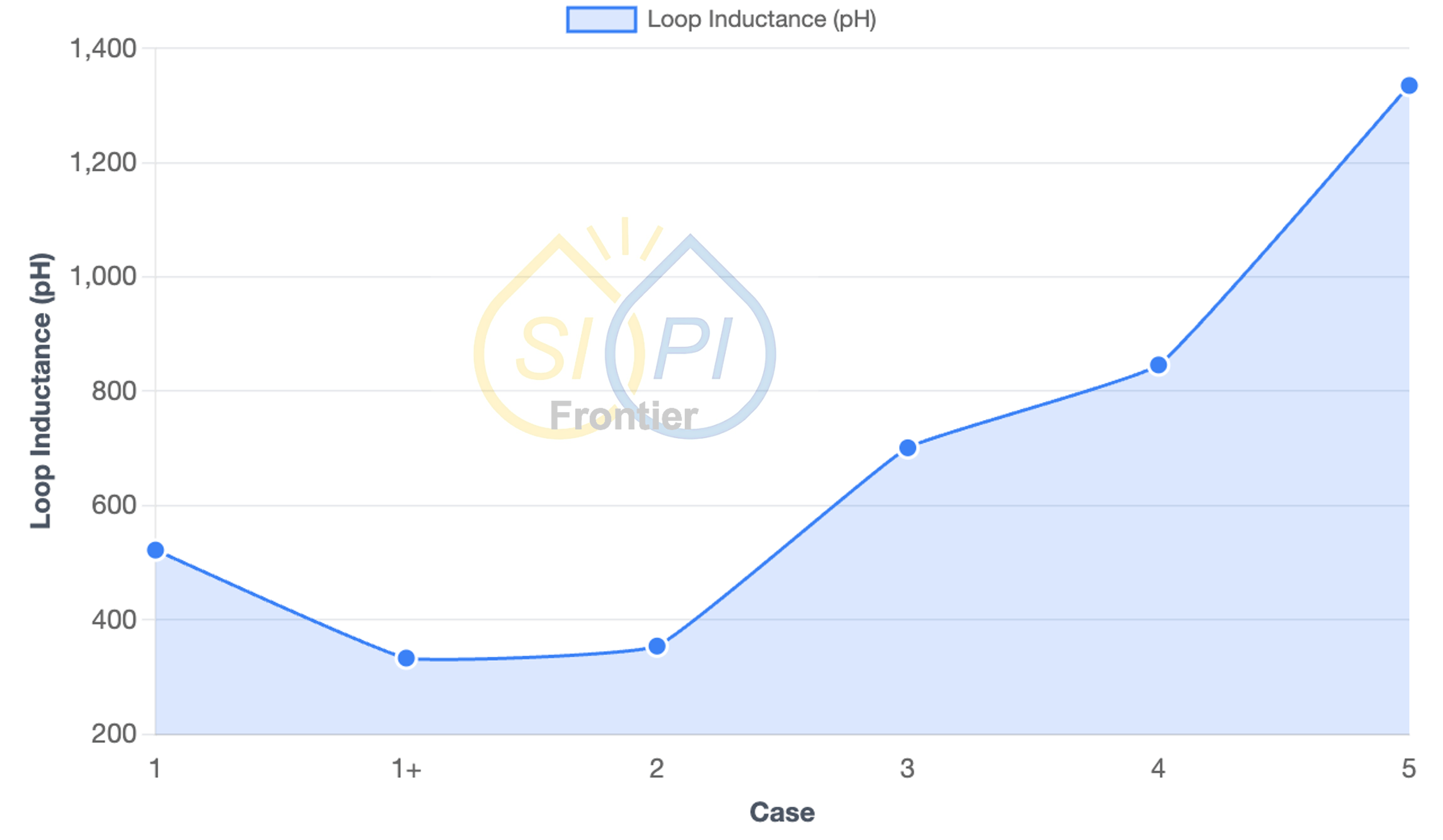

下图,黑色的PDN阻抗结果在KHz有个很明显的并联谐振,这个谐振由VRM的电容器与VRM到解耦芯片的路径电感所造成,对应到右边那张图的黑色Ripple,当红色的电流波形稍有震荡,Ripple就会很明显; 当我们借由设计上的改善,例如调整容值、透过优化路径改善寄生电感等等,将黑色曲线改成蓝色曲线,阻抗变平坦了,电压震荡就小了!

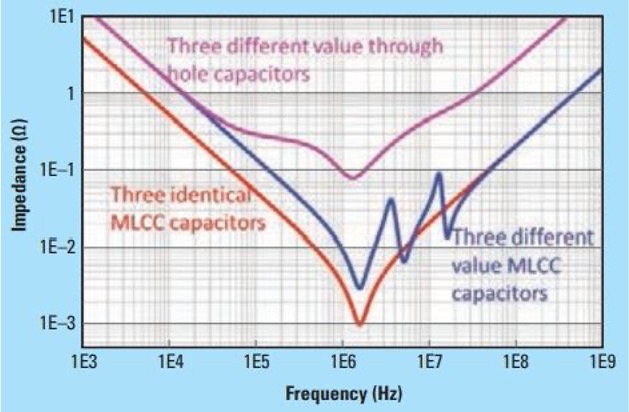

如果像开头我们所说,很多的Design guide会推荐三种容值的摆法,那就会像这张图,当我们选择三种不同的MLCC电容值,每个皆间隔10倍,就会发生右图蓝色曲线这样,阻抗跳来跳去,结果就是Ripple很震! 当然这不代表电压测试会出事,或许只是丑了点罢了!

顺带一题,如果所有电容都选择相同容值,就会看到像右图红色曲线,阻抗掉很低,结果就是Q值过大,当遇到相同频率的能量时,电压很容易炸锅!

或许你现在就想问,这个也不行那个也不行,怎么办?

唯有通过良好的PI分析,将系统的PDN model萃取出来,在适当的位置上放上电容,在一个一个优化电容器的容值与型号,才有可能办得到所谓的平坦阻抗,现在其实也有很多软件可以支持自动化优化所有电容的选择,例如Cadence OptimizePI,很方便的!

不同类型的MLCC

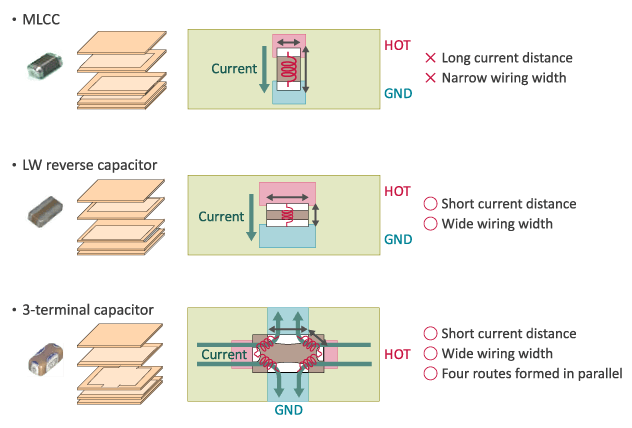

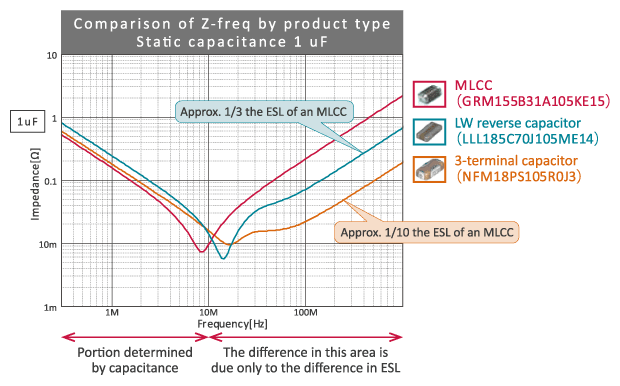

其实MLCC也分成好几种,一般我们在用的、最常看到的,是下图写的MLCC,与Substrate/PCB的焊接点在电容器的短边,这种MLCC在制程上较为简单,且制造流程已经发展了数十年,且PCB SMT生产线也都是为这种MLCC量身定做,机械强度也较强,容易在各个供应商之间替换料等等优势。 可是由于内部电流路径较长与较窄的焊接空间,导致寄生电感ESL较大,所以才有几种改良版本:

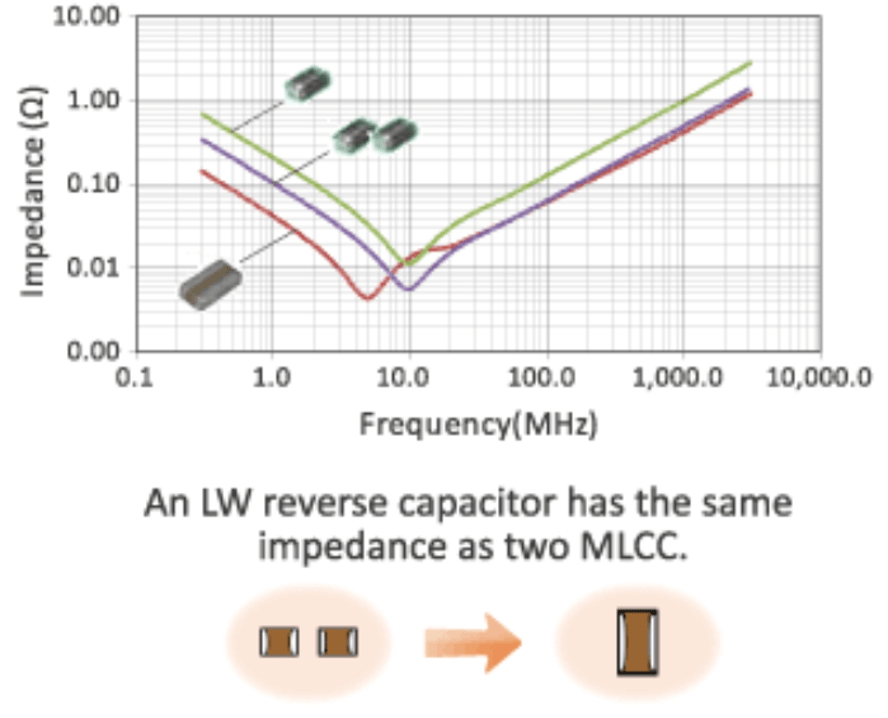

LW Reverse

顾名思义就是将MLCC的长边跟短边互换,让长边去扛焊接点位,这样电流路径就可以变短,焊接面积也较宽,寄生电感就可以下降,高频阻抗变好! 其实就是想象成Power trace变粗的概念!

看上面的阻抗图,可以知道LW reverse的电容器,ESL可以缩小3倍。

在板子设计上,我们可以利用这种组件的优势,替代掉一倍的传统MLCC,减少MLCC的使用,优化Placement,让Layout更干净!

当然,要不是在很极致的应用层面上,我们是不建议用这种料的,撇除成本不谈,还得考量SMT产线的能力,当PCB板弯翘时,LW reverse的电容是否容易断裂? 且电性上ESL是否真的需要这么好?

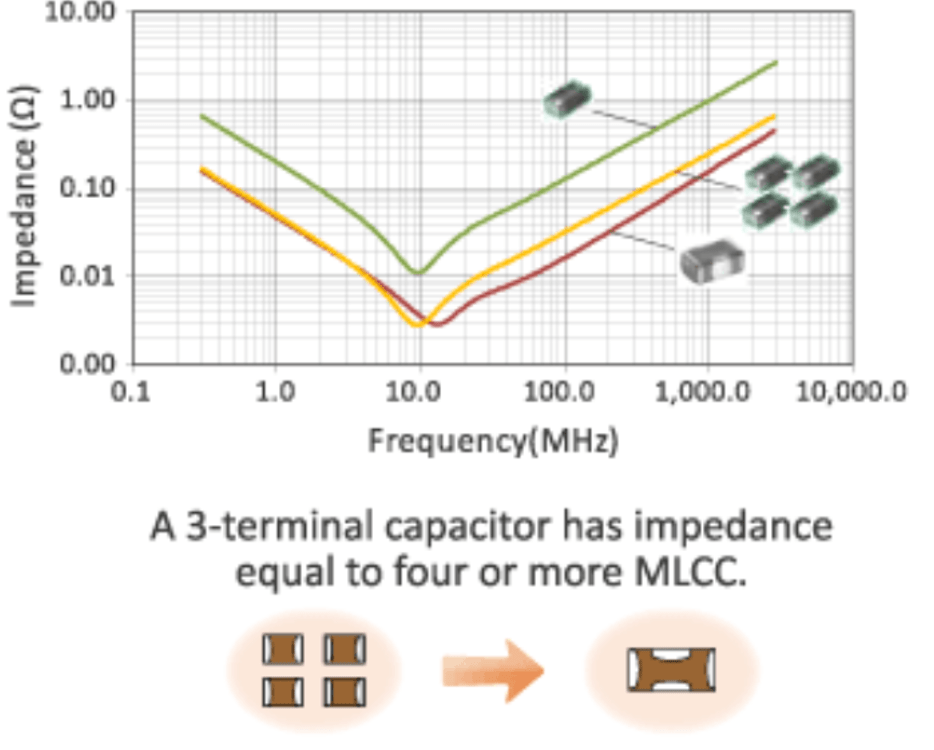

3T Terminal 电容器

这种三端子电容器通过增加电流在电容器内部的并联路径,降低总体电感,并且优化高频阻抗。 从阻抗结果来看,ESL可以比传统的MLCC还好上10倍。 对标到传统的MLCC,如果真的拿来做替换工程的话,大概就是一颗的3端子电容器可以替换成四颗MLCC。

这种三端子电容器非常适合用于处理对电源灵敏度要求极高的系统,特别是RF系统。 由于RF系统需要接收非常微弱的能量信号,即使是极小的电源噪声也可能造成信号失真或接收灵敏度下降,因此必须确保电源质量极度干净且稳定。 三端子电容器凭借其卓越的高频特性和极低的寄生电感,能够有效滤除宽带噪声,维持Power Rail的完整性,这正是此类电容器在高敏感度应用中的关键优势所在。 在实际应用中,这类电容器可以大幅减少设计复杂度,同时提升系统整体性能表现。

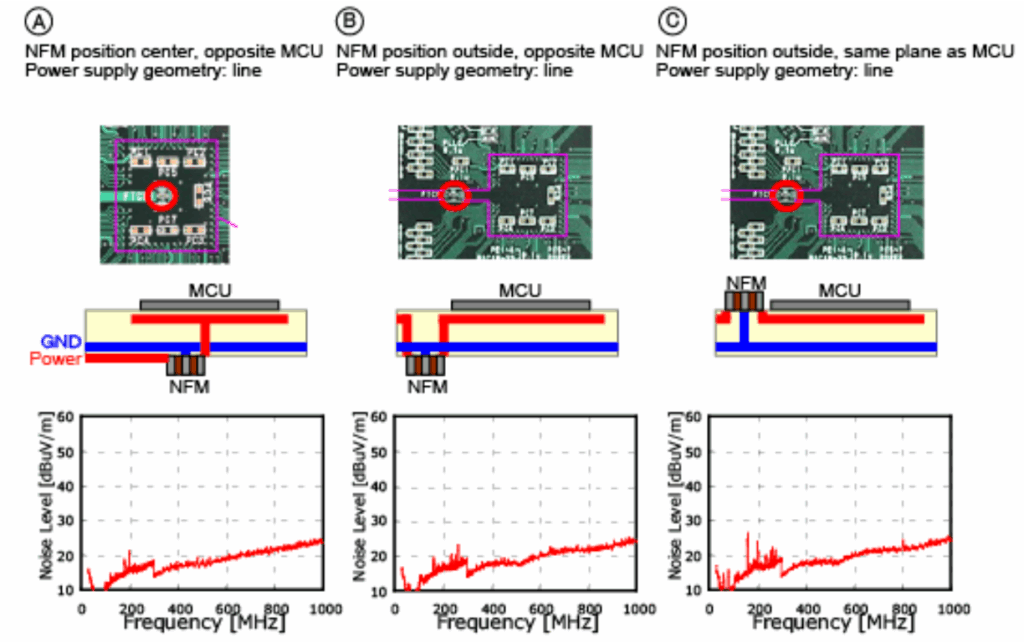

三端子电容器设计案例分享

Murata有给一个利用3-Terminal Capacitor用来滤波MCU的案例,Case A的三端电容(Murata NFM Series)放在MCU的正下方,Case C的三端电容则放在MCU旁边,纯看Power来讲Case C应该是比较好,毕竟Case A多了Power Via的电感,可是由于Case C的GND Via设计得特别长, 所以从Noise来看结果并没有比较好。

不能只单看Power本身的设计,GND的设计或许才是你该注意的!

而Case B则是比Case A的路径还稍远一些,所以噪声会较高,在这里要注意Power Via的摆放位置,由于噪声的滤波要经过三端子电容才有用,可是两个Power Via摆很近的情况下,很有可能噪声会透过Power Via耦合,进而跳过电容器。 (可能啦... 可是这个耦合量应该低低低到不行才是... 但不能说完全沒影響)

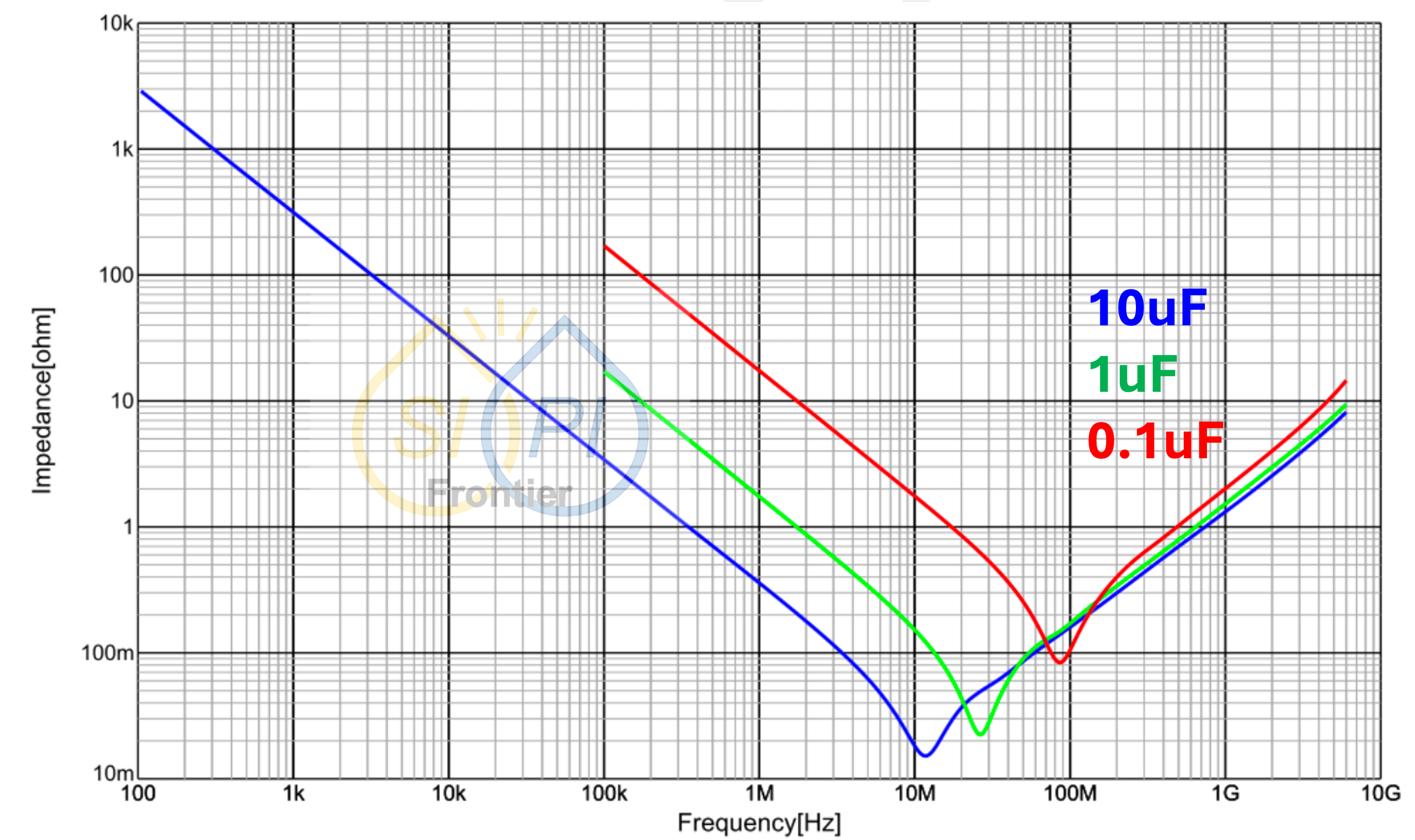

利用三端子电容器拿来滤波DC/DC Converter的输出噪声,真的是差了不少喔: