怎么理解锁相环主时钟(PLL)怎么做到对时钟进行倍频?

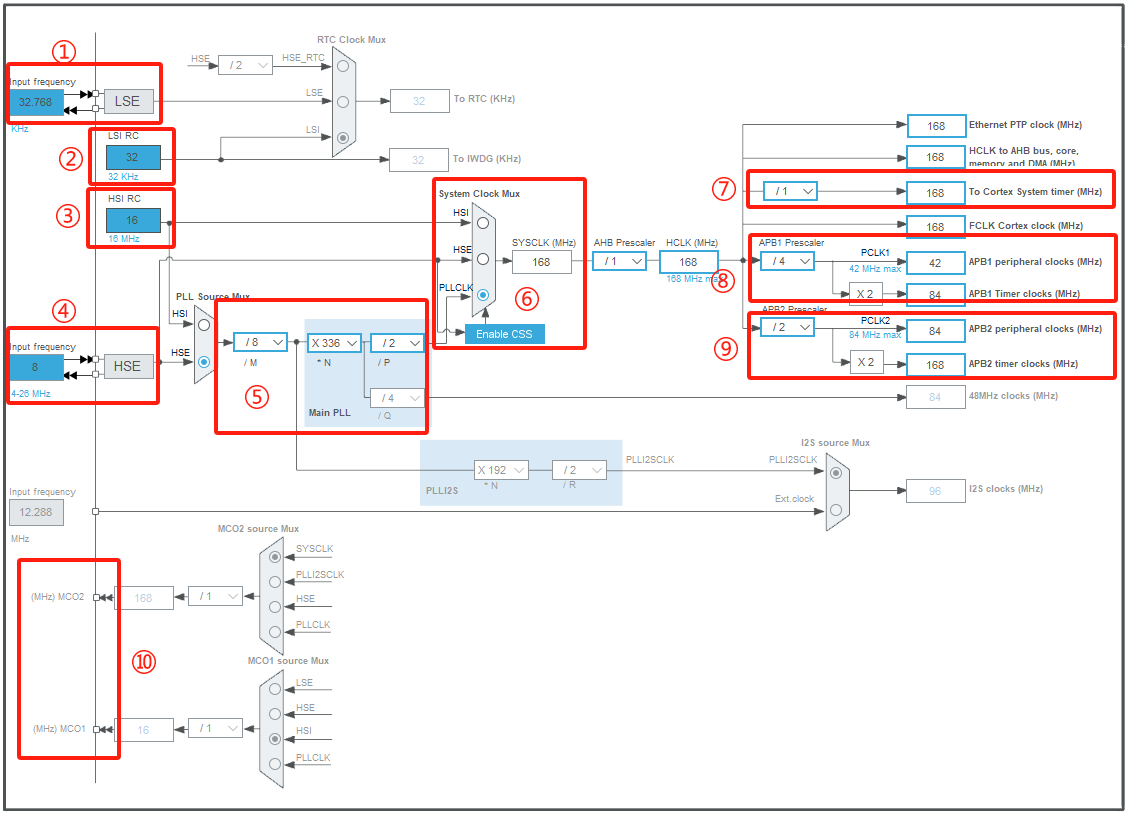

⑤ 锁相环主时钟(PLL)

STM32F4xx具有两个PPL时钟,PLL 的主要作用是对时钟进行倍频,然后把时钟输出到各个功能部件。 PLL 有两个,一个是主 PLL,另外一个是专用的 PLLI2S,他们均由 HSE 或者 HSI 提供时钟输入信号。

我用更通俗的方式给你解释一下 PLL 是怎么给时钟 "加速" 的:

想象你在玩一个 "模仿游戏":

- 你(VCO)负责拍手,一开始节奏随便

- 你的朋友(参考时钟)有一个固定节奏的拍手(比如每秒 2 下)

- 另一个朋友(分频器)会把你拍的手数 "除以 N" 再告诉你

- 裁判(相位比较器)会对比你朋友的节奏和经过除法后的你的节奏

游戏规则:

- 如果你的节奏太慢,经过除法后比朋友的慢,裁判就喊 "快点"

- 如果你的节奏太快,经过除法后比朋友的快,裁判就喊 "慢点"

- 直到你拍的节奏除以 N 后,正好等于朋友的节奏(比如你每秒拍 4 下,N=2,4/2=2)

这时候你的节奏就是朋友的 N 倍(4=2×2),这就是 PLL 的倍频原理!

简单说,PLL 就像一个 "自动调速器":

- 通过不断比较和调整

- 让输出节奏(频率)稳定在输入节奏的 N 倍

- N 是可以设置的(比如 2 倍、5 倍、10 倍)

这样一来,我们就能用一个低频时钟信号,通过 PLL 得到稳定的高频时钟信号了。

咱们用更具体的例子一步步说清楚 PLL 是怎么实现倍频的,就拿 "把 10MHz 的时钟变成 50MHz" 来说(也就是 5 倍频):

第一步:准备三个核心 "工具"

- VCO(压控振荡器):相当于一个 "可调速的马达",给它的电压越高,转得越快(输出频率越高)。

- 分频器:相当于一个 "计数器",设定为 "5 分频"—— 每收到 5 个 VCO 的信号,才输出 1 个信号。

- 相位比较器:相当于一个 "检测器",能同时看两个信号:

- 输入的原始时钟(10MHz)

- 分频器送回来的信号

第二步:开始 "调速" 过程

假设一开始 VCO 输出的是 30MHz(还没到目标 50MHz):

- 分频器对 30MHz 进行 5 分频,得到 30÷5=6MHz,送回给相位比较器。

- 相位比较器发现:送回的 6MHz 比 原始的 10MHz 慢(节奏跟不上)。

- 于是它输出一个 "升压信号",给 VCO 的电压升高一点。

- VCO 电压升高后,输出频率变快,比如升到 40MHz。

第三步:继续调整直到稳定

- 40MHz 经过 5 分频,得到 8MHz,还是比 10MHz 慢。

- 相位比较器继续 "升压",VCO 输出升到 50MHz。

- 50MHz 经过 5 分频,正好是 10MHz,和原始时钟节奏完全一致。

- 这时候相位比较器觉得 "没问题了",不再调整电压,VCO 就稳定输出 50MHz。

关键:为什么能稳定在 5 倍?

因为分频器设定了 "5",所以只有当 VCO 输出是原始时钟的 5 倍时,分频后的信号才能和原始时钟 "对齐"。就像拼图一样,只有这一种情况能严丝合缝,PLL 会自动找到这个状态并保持住。

只要改变分频器的数值(比如改成 3),就能得到原始时钟 3 倍的输出,这就是 PLL 能灵活实现倍频的原因。