《计算机组成原理与汇编语言程序设计》实验报告一 基本数字逻辑及汉字显示

目 录

一、实验学时

二、实验目的

三、实验要求

四、实验内容

五、实验步骤

1、打开Logisim软件,列出异或逻辑电路真值表,并使用与、或、非基本原件实现异或逻辑电路。

2、打开Logisim软件,列出同或逻辑电路真值表,并使用与、或、非基本原件实现同或逻辑电路。

3、打开Logisim软件,列出一位二进制数据比较器真值表,并使用与、非、异或非原件实现一位二进制数据比较器逻辑电路。

4、打开Logisim软件,列出全加器逻辑电路真值表,并使用与、或、异或原件实现全加器逻辑电路。

5、打开Logisim软件,列出3-8译码器逻辑电路真值表,并使用非、或原件实现3-8译码器逻辑电路。

6、打开Logisim软件以及机内码与汉字转换软件,并打开电路文件分析和理解相关的电路功能。

六、实验小结

1、问题和解决方法

2、心得体会

一、实验学时

课堂2学时,课后2学时

二、实验目的

1) 熟悉Logisim软件的使用方法。

2) 掌握基本数字逻辑电路实现方法。

3) 熟悉汉字字库及显示电路。

三、实验要求

1)做好实验预习,复习基本数字逻辑电路的原理,掌握实验元器件的功能特性。

2)按照实验内容与步骤的要求,独立思考,认真仔细地完成实验。

3)书写实验报告。

四、实验内容

1、本次实验使用Logisim软件实现基本的数字逻辑电路,与、或、非等基本原件的使用,及异或(XOR)、同或逻辑的实现。

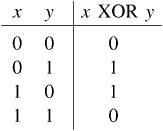

(1)异或电路及真值表示意如下:

图4-1 异或真值表及电路图

(2)在完成基本数字逻辑测试的基础上,完成3-8译码器,一位二进制数据比较器设计。

(3)请列出上述提到基本数字逻辑电路真值表,最后在Logisim中实现连线,并测试逻辑是否正确。

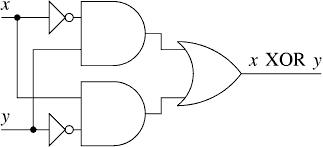

2、利用给出的电路文件,熟悉汉字显示电路,分析相关子电路的功能,理解GB2312编码与区位码的转化规则和电路实现,熟悉Logisim中存储器ROM、LED点阵的使用。最后利用机内码与汉字转换工具,或者自己编程实现转化,将自己名字写进GB2312 存储器中,实现将自己的名字在LED点阵中显示。

图4-2 所需电路及工作区

五、实验步骤

1、打开Logisim软件,列出异或逻辑电路真值表,并使用与、或、非基本原件实现异或逻辑电路。

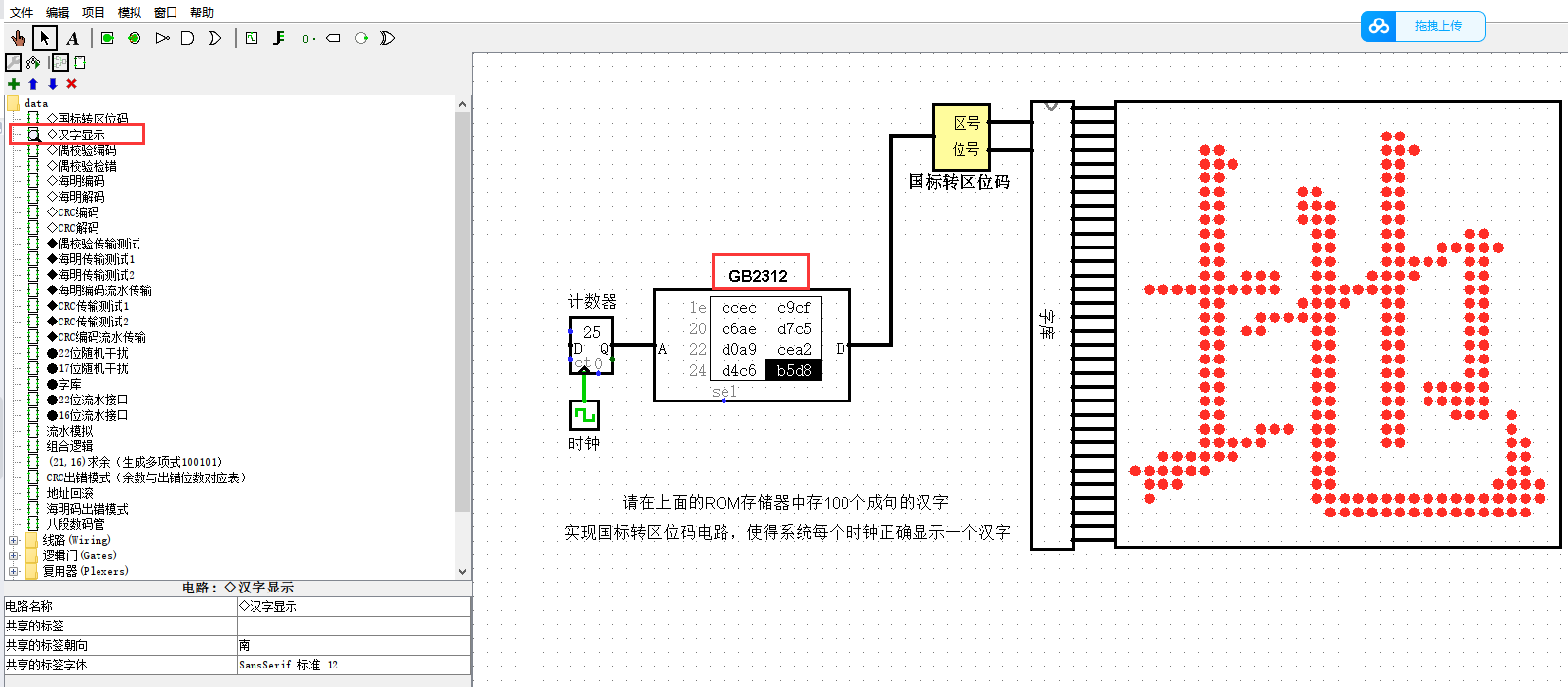

(1)使用异或逻辑公式F=A⊕B=AB’+A’B(F为A异或B的结果值,⊕为异或符号,A’和B’分别表示对A、B进行非操作后的结果)完成对异或逻辑电路的实现,对应的异或逻辑电路真值表如图5-1-1所示:

图5-1-1 异或逻辑电路真值表

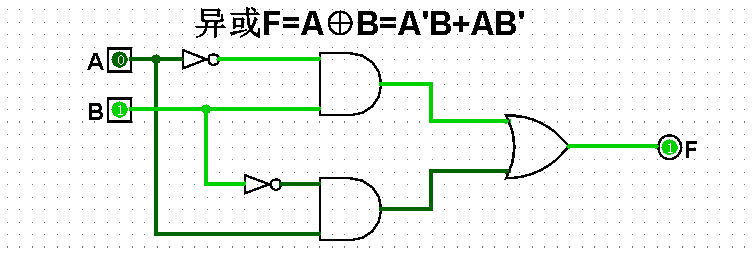

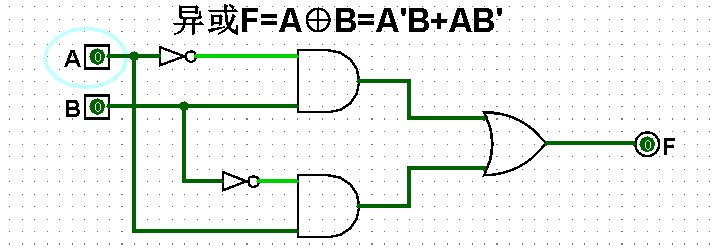

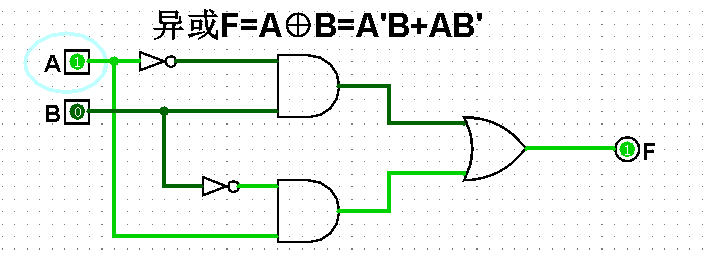

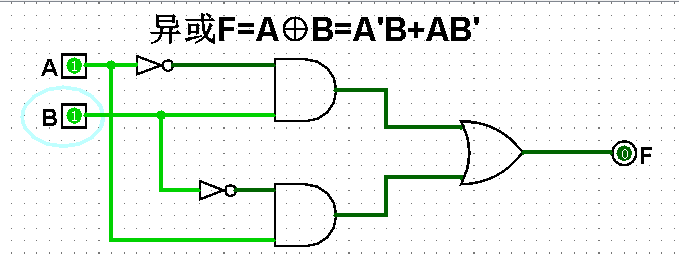

(2)依据异或逻辑公式完成异或逻辑电路的架构,输入端A、B,先进行A的非操作,然后与B进行与操作得到A’B;再进行B的非操作,然后与A进行与操作得到AB’,最后将A’B和AB’进行或操作,得到最后的异或逻辑运算结果F,对应的异或逻辑电路如图5-1-2所示:

图5-1-2 异或逻辑电路

(3)异或逻辑电路铺设完毕后进行测试,进而判断自己的电路是否铺设成功,经过测试后此电路状态一切正常,对应的异或逻辑电路测试如图5-1-3至5-1-5所示:

图5-1-3 异或逻辑电路测试0⊕0

图5-1-4 异或逻辑电路测试1⊕0

图5-1-5 异或逻辑电路测试1⊕1

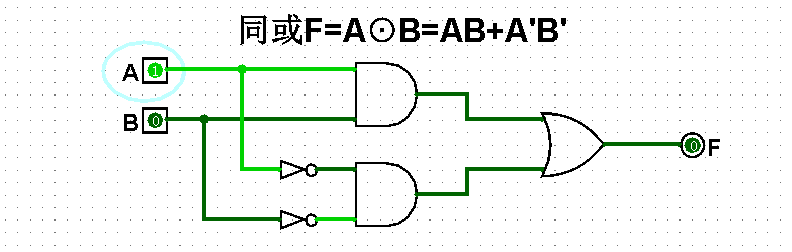

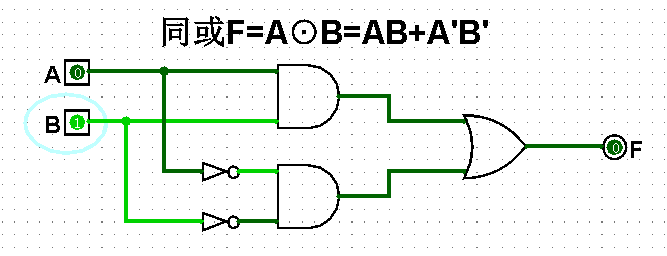

2、打开Logisim软件,列出同或逻辑电路真值表,并使用与、或、非基本原件实现同或逻辑电路。

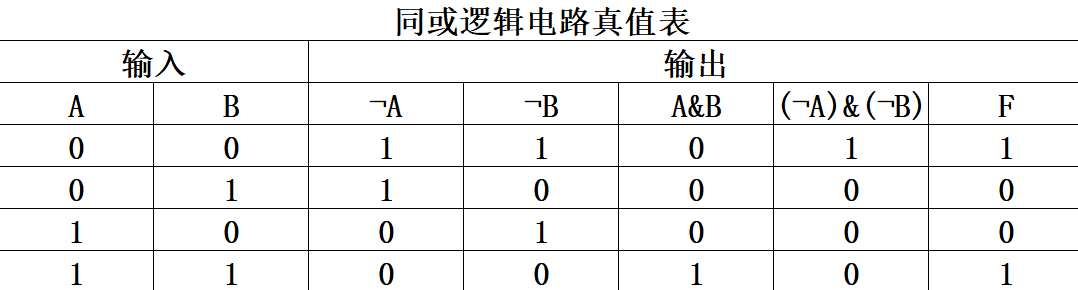

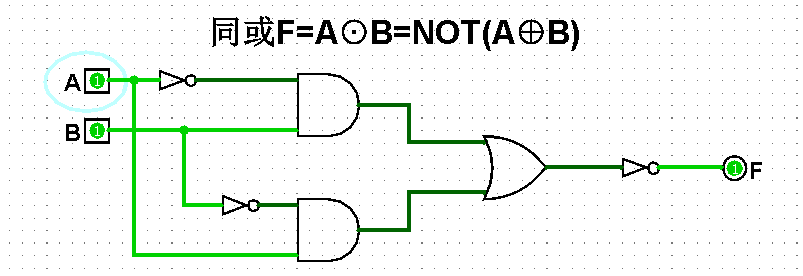

(1)使用同或逻辑公式F=A⨀B=AB+A’B’(F为A同或B的结果值,⨀为同或符号,A’和B’分别表示对A、B进行非操作后的结果)完成对同或逻辑电路的实现,对应的同或逻辑电路真值表如图5-2-1所示:

图5-2-1 同或逻辑电路真值表

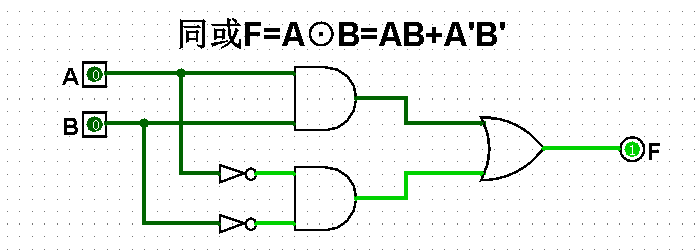

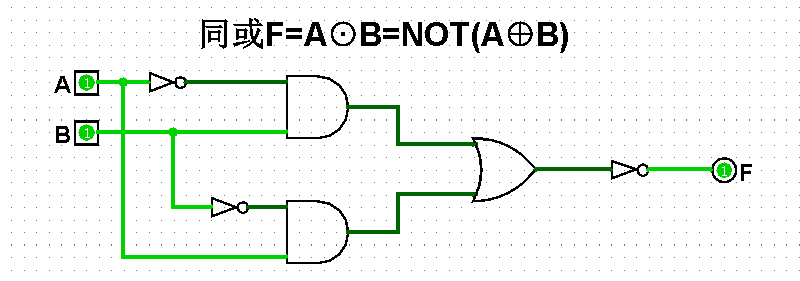

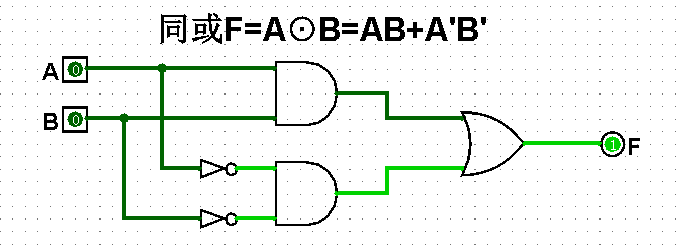

(2)依据同或逻辑公式完成同或逻辑电路的架构,输入端A、B,先进行A和B的与操作后得到AB;然后分别进行A和B的非操作后并进行与操作得到A’B’;最后将AB和A’B’进行或操作,得到最后的同或逻辑运算结果F,对应的同或逻辑电路如图5-2-2所示:

图5-2-2 同或逻辑电路

(3)同或逻辑电路铺设完毕后进行测试,进而判断自己的电路是否铺设成功,经过测试后此电路状态一切正常,对应的同或逻辑电路测试如图5-2-3至5-2-5所示:

图5-2-3 同或逻辑电路测试1⨀0

图5-2-4 同或逻辑电路测试0⨀1

图5-2-5 同或逻辑电路测试1⨀1

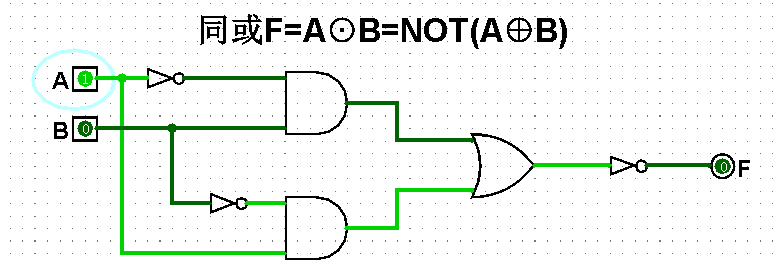

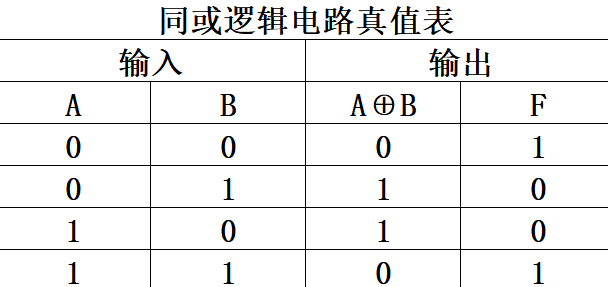

(4)使用同或逻辑公式F=A⨀B=A⨁B(____________)(F为A同或B的结果值,⨀为同或符号,⨁为异或符号)完成对同或逻辑电路的实现,对应的同或逻辑电路真值表如图5-2-6所示:

图5-2-6 同或逻辑电路真值表

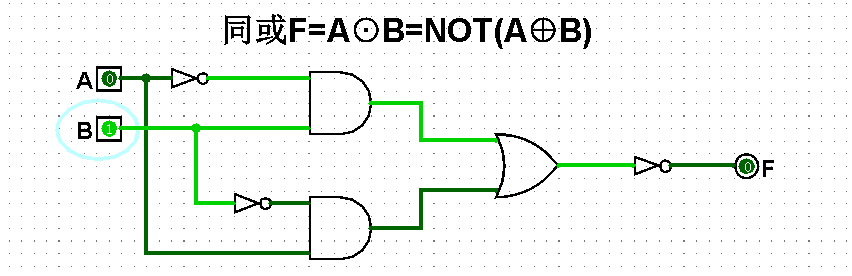

(5)依据对异或操作进行非操作后得到同或逻辑完成同或逻辑电路的架构,在异或的基础之上进行非操作得到最后的同或逻辑运算结果F,对应的同或逻辑电路如图5-2-7所示:

图5-2-7 同或逻辑电路

(6)同或逻辑电路铺设完毕后进行测试,进而判断自己的电路是否铺设成功,经过测试后此电路状态一切正常,对应的同或逻辑电路测试如图5-2-8至5-2-10所示:

图5-2-8 同或逻辑电路测试0⨀0

图5-2-9 同或逻辑电路测试1⨀0

图5-2-10 同或逻辑电路测试0⨀1

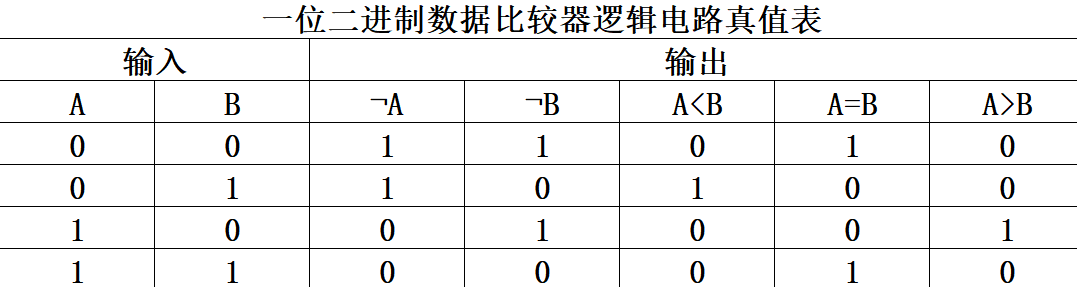

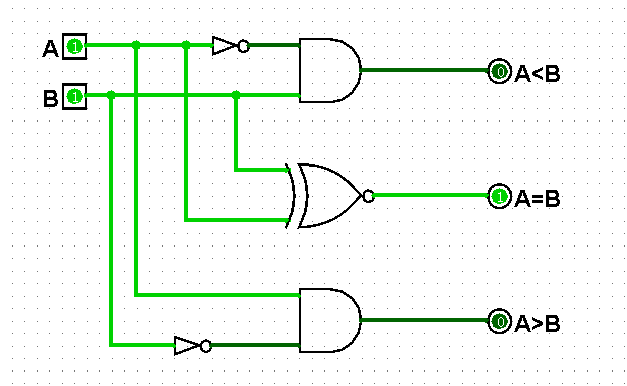

3、打开Logisim软件,列出一位二进制数据比较器真值表,并使用与、非、异或非原件实现一位二进制数据比较器逻辑电路。

(1)使用一位二进制数据比较器逻辑公式(A<B)=A’B、(A=B)=A⨀B、(A>B)=AB’(⨀为同或符号,A’和B’分别表示对A、B进行非操作后的结果)完成对一位二进制数据比较器逻辑电路的实现,对应的一位二进制数据比较器逻辑电路真值表如图5-3-1所示:

图5-3-1 一位二进制数据比较器逻辑电路真值表

(2)依据一位二进制数据比较器逻辑公式完成一位二进制数据比较器逻辑电路的架构,输入端A、B,先进行A的非操作,然后与B进行与操作得到A’B,A’B=1则表示A<B;再进行B的非操作,然后与A进行与操作得到AB’,AB’=1则表示A>B;最后A和B进行同或操作结果为1则表示A=B,对应的一位二进制数据比较器逻辑电路如图5-3-2所示:

图5-3-2 一位二进制数据比较器逻辑电路

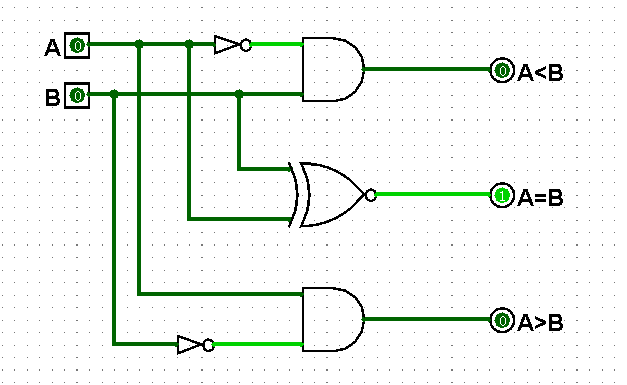

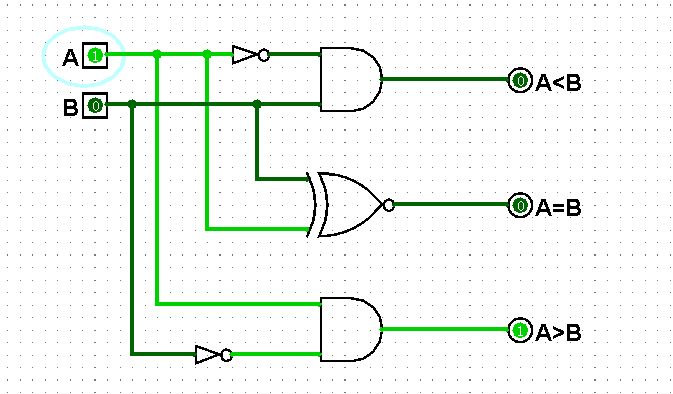

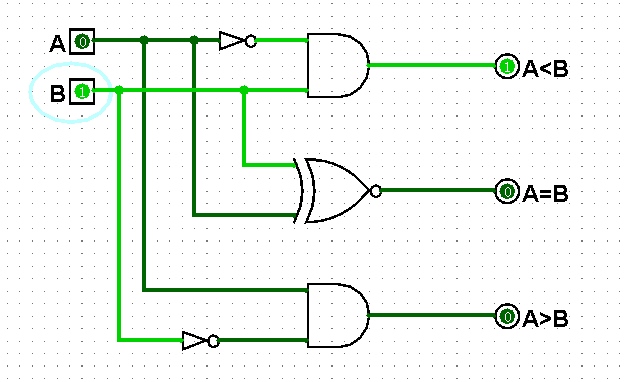

(3)一位二进制数据比较器逻辑电路铺设完毕后进行测试,进而判断自己的电路是否铺设成功,经过测试后此电路状态一切正常,对应的一位二进制数据比较器逻辑电路测试如图5-3-3至5-3-5所示:

图5-3-3 一位二进制数据比较器逻辑电路测试0和0

图5-3-4 一位二进制数据比较器逻辑电路测试1和0

图5-3-5 一位二进制数据比较器逻辑电路测试0和1

4、打开Logisim软件,列出全加器逻辑电路真值表,并使用与、或、异或原件实现全加器逻辑电路。

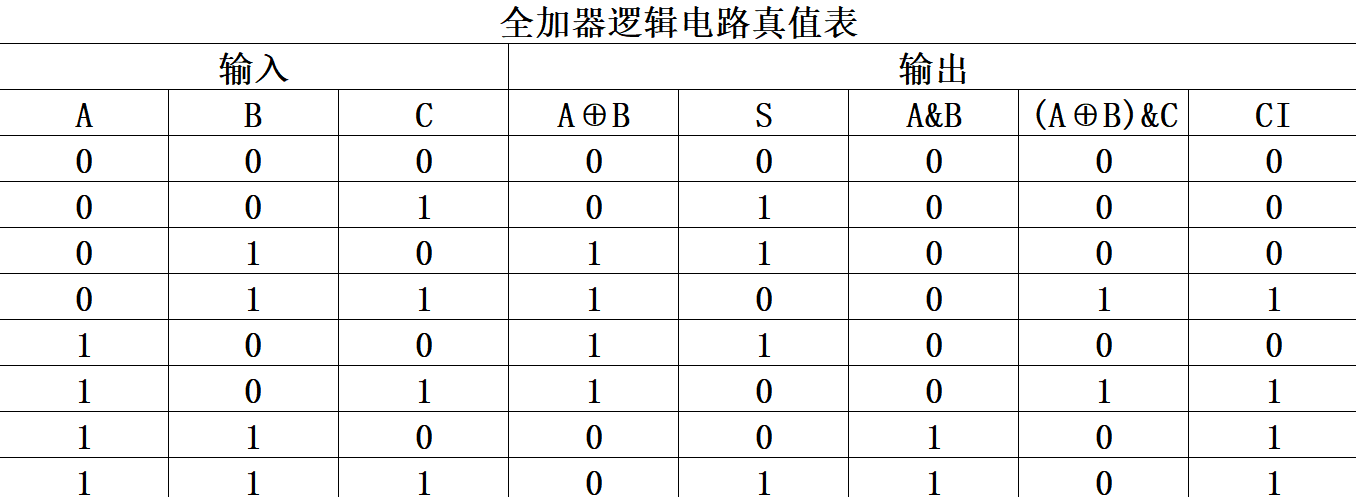

(1)使用全加器逻辑公式G=AB、P=A⊕B、CI=G+PC(G为A与B的结果值,P为A异或B的结果值,⊕为异或符号,CI为G或PC的结果值)完成对全加器逻辑电路的实现,对应的全加器逻辑电路真值表如图5-4-1所示:

图5-4-1 全加器逻辑电路真值表

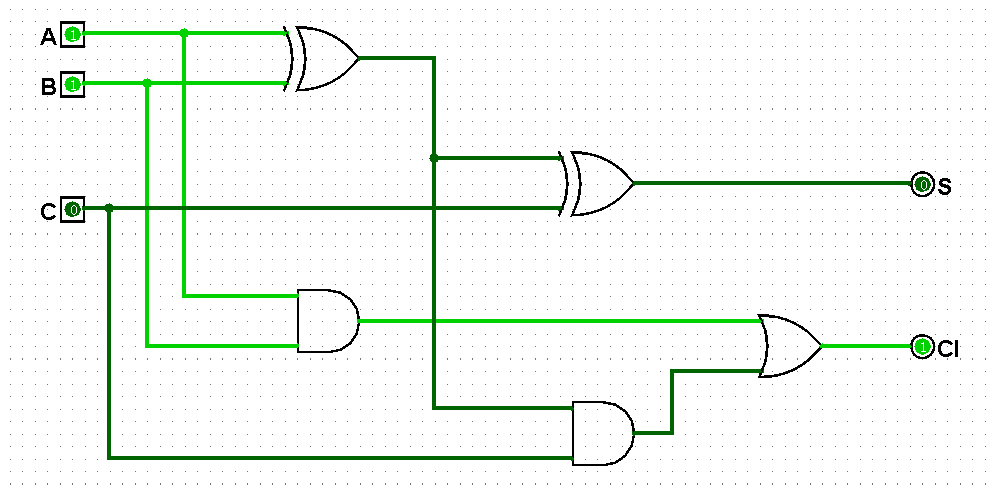

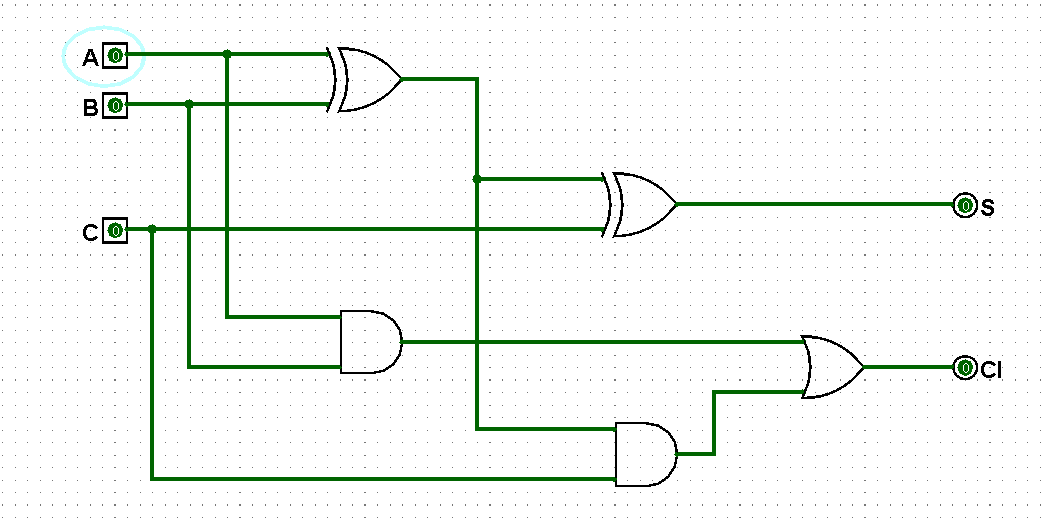

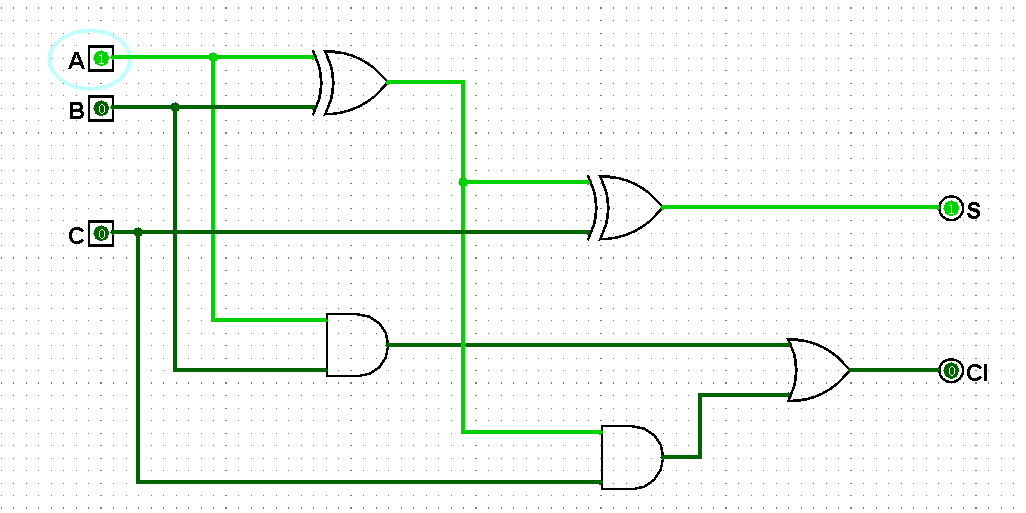

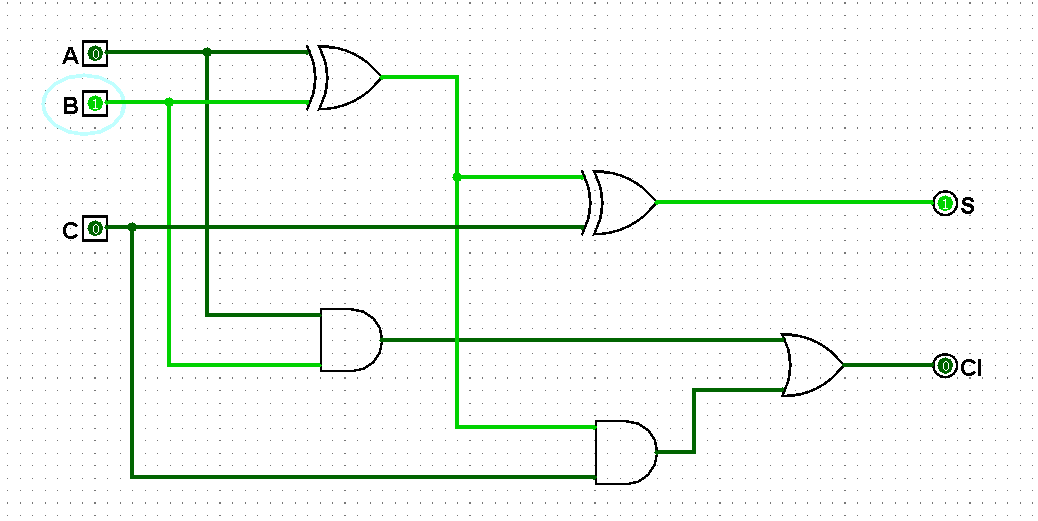

(2)依据全加器逻辑公式完成全加器逻辑电路的架构,输入端A、B、C,先进行A和B的异或操作得到P;然后进行A和B的与操作得到G;再进行P和C的异或操作得到S;最后将P和C进行与操作后再和G进行或操作,得到最后的全加器逻辑运算结果CI,对应的全加器逻辑电路如图5-4-2所示:

图5-4-2 全加器逻辑电路

(3)全加器逻辑电路铺设完毕后进行测试,进而判断自己的电路是否铺设成功,经过测试后此电路状态一切正常,对应的全加器逻辑电路测试如图5-4-3至5-4-5所示:

图5-4-3 全加器逻辑电路测试0+0

图5-4-4 全加器逻辑电路测试1+0

图5-4-5 全加器逻辑电路测试0+1

5、打开Logisim软件,列出3-8译码器逻辑电路真值表,并使用非、或原件实现3-8译码器逻辑电路。

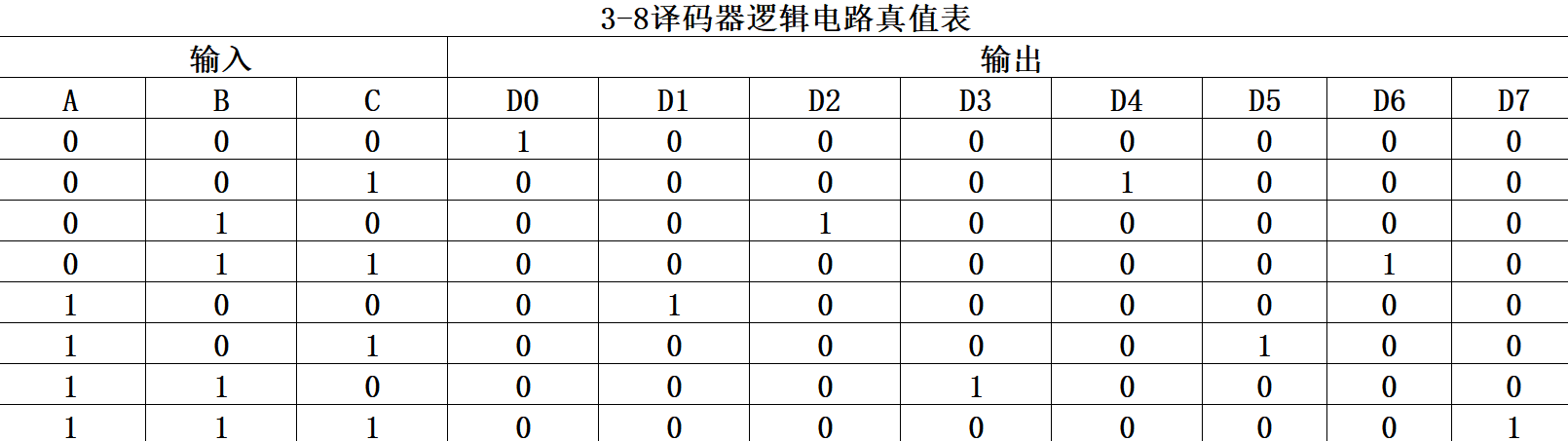

(1)使用3-8译码器逻辑公式D0=A’B’C’、D1=AB’C’、D2=A’BC’、D3=ABC’、D4=A’B’C、D5=AB’C、D6=A’BC、D7=ABC(A’、B’、C’分别为对A、B、C的非操作,D为进行与操作后的结果值)完成对3-8译码器逻辑电路的实现,对应的3-8译码器逻辑电路真值表如图5-5-1所示:

图5-5-1 3-8译码器逻辑电路真值表

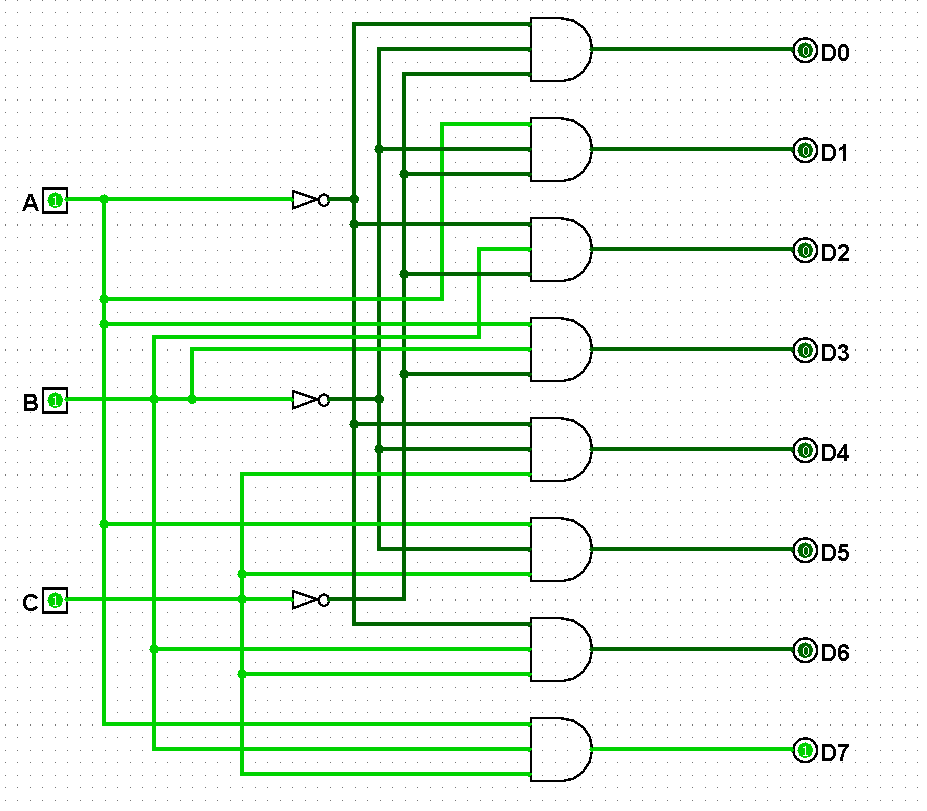

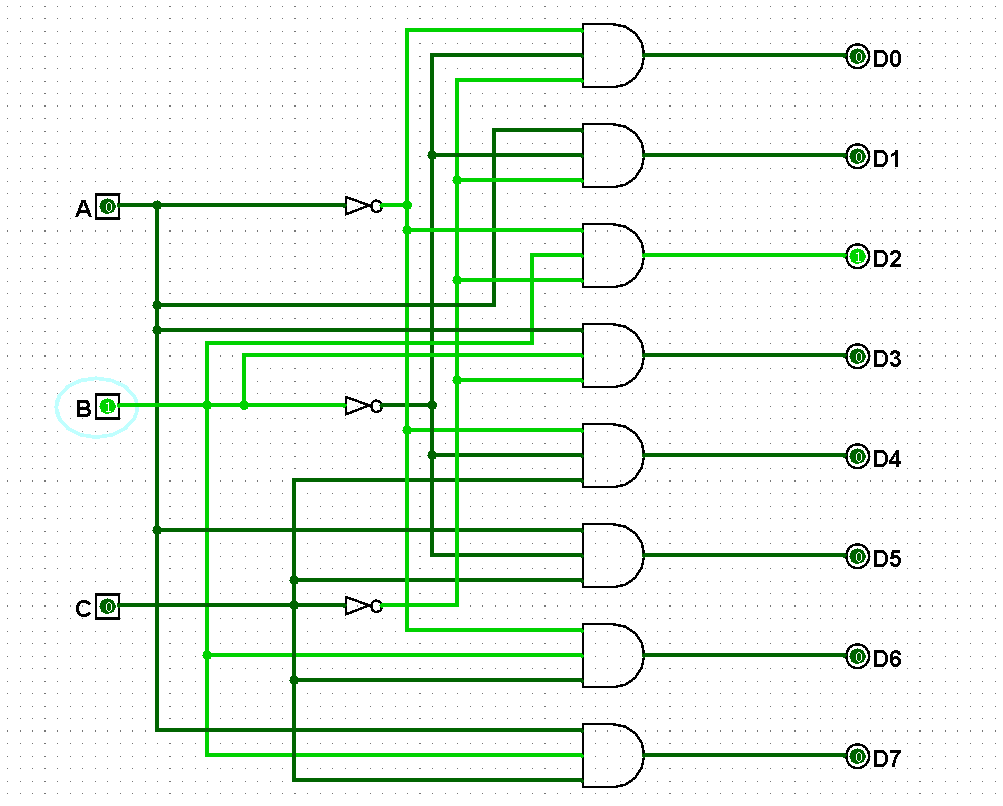

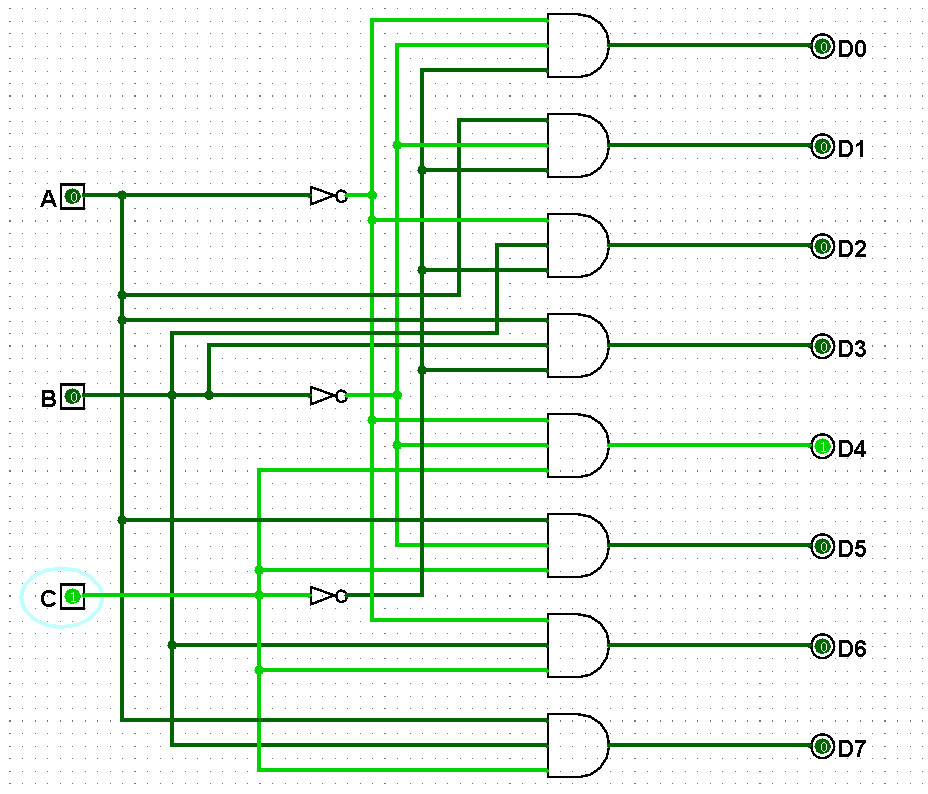

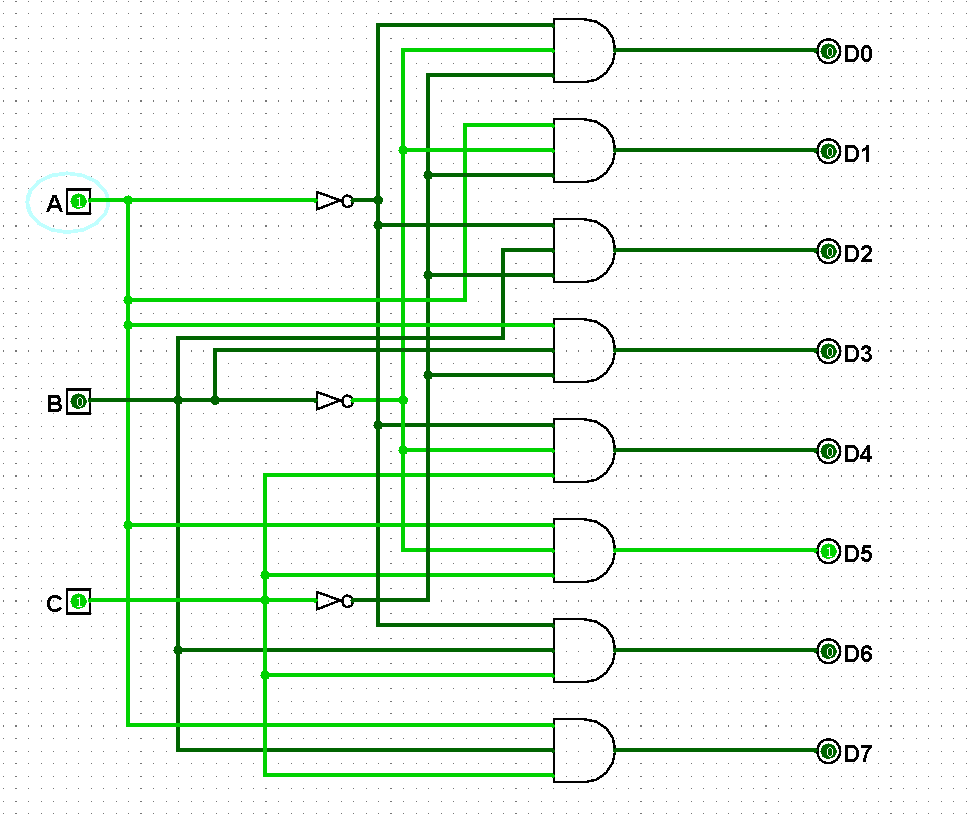

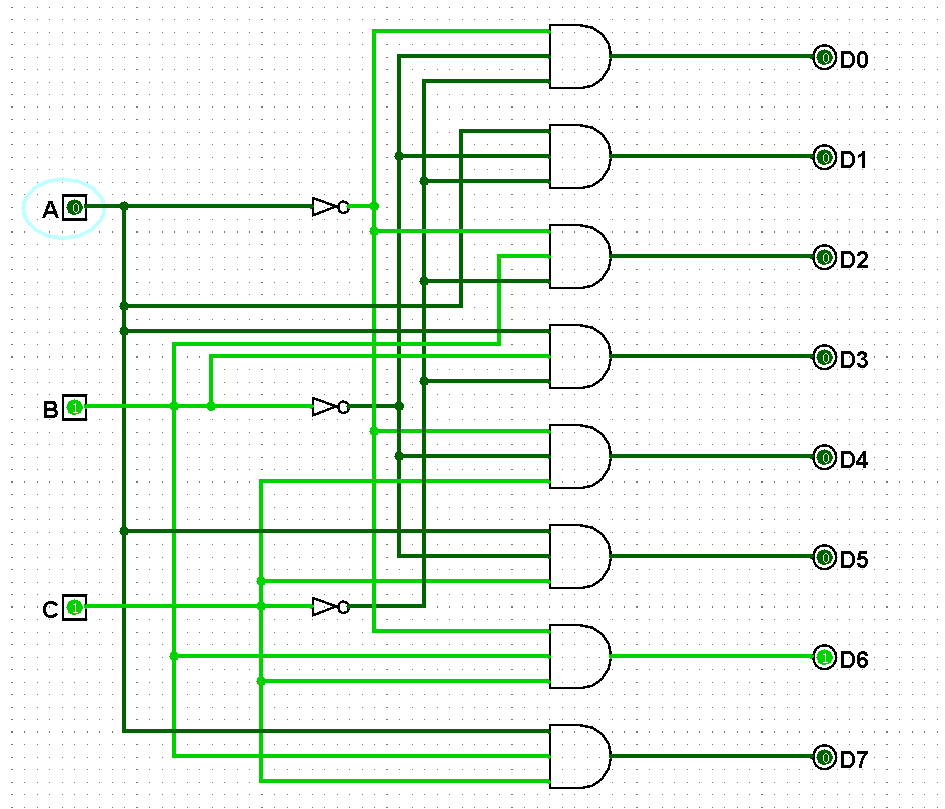

(2)依据3-8译码器逻辑公式完成3-8译码器逻辑电路的架构,输入端A、B、C,对A、B、C分别进行非操作后再进行与操作得到D0;对B、C分别进行非操作后再和A进行与操作得到D1;对A、C进行非操作后再和B进行与操作后得到D2;对C进行非操作后再和A、B进行与操作后得到D3;对A、B进行非操作后再和C进行与操作后得到D4;对B进行非操作后再和A、C进行与操作得到D5;对A进行非操作后再与B、C进行与操作得到D6;对A、B、C进行与操作后得到D7,对应的3-8译码器逻辑电路如图5-5-2所示:

图5-5-2 3-8译码器逻辑电路

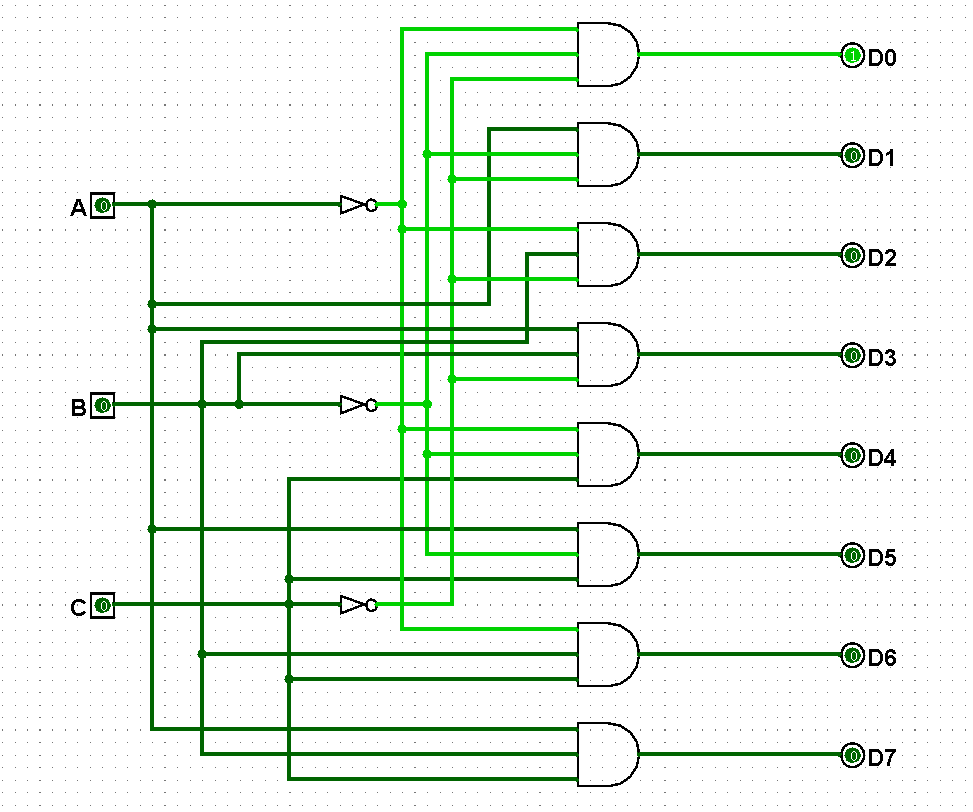

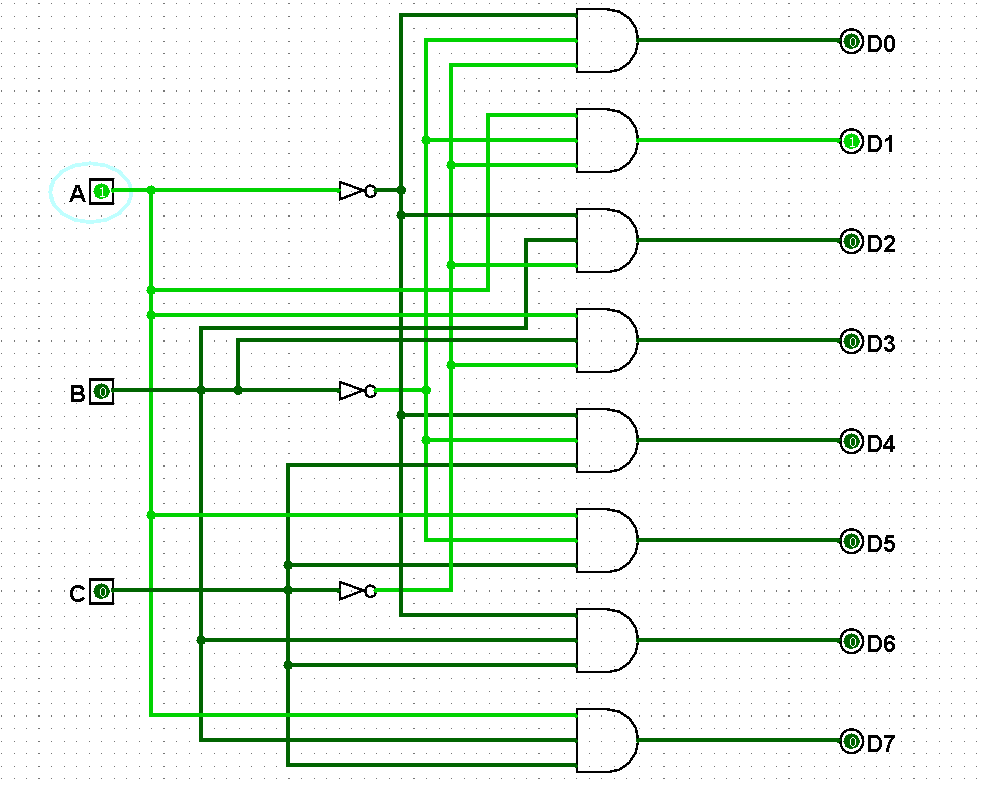

(3)3-8译码器逻辑电路铺设完毕后进行测试,进而判断自己的电路是否铺设成功,经过测试后此电路状态一切正常,对应的3-8译码器逻辑电路测试如图5-5-3至5-5-8所示:

图5-5-3 3-8译码器逻辑电路测试000

图5-5-4 3-8译码器逻辑电路测试001

图5-5-5 3-8译码器逻辑电路测试010

图5-5-6 3-8译码器逻辑电路测试100

图5-5-7 3-8译码器逻辑电路测试101

图5-5-8 3-8译码器逻辑电路测试110

6、打开Logisim软件以及机内码与汉字转换软件,并打开电路文件分析和理解相关的电路功能。

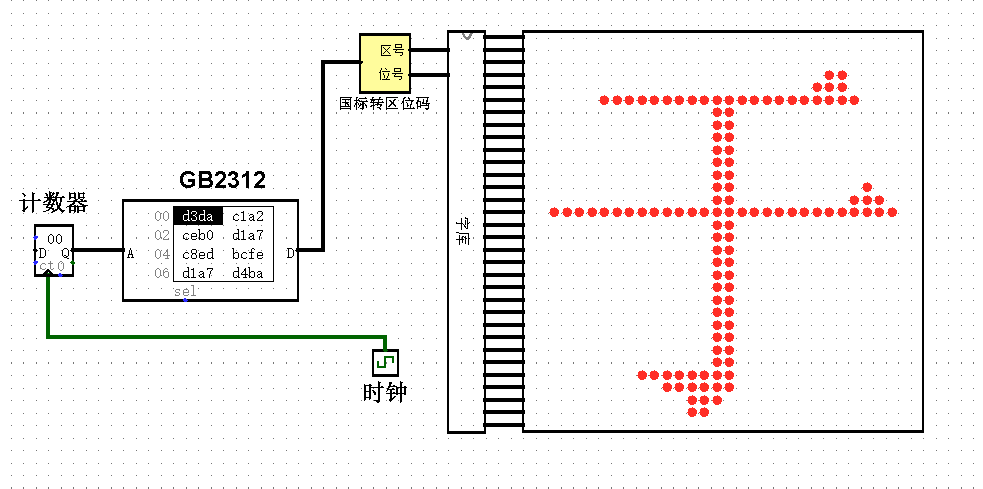

(1)使用机内码与汉字转换软件将汉字“于”转换为机内码,得到对应的机内码为D3DA,然后对只读存储器ROM中的内容进行编辑,将其写进GB2312存储器中,实现汉字“于”在LED点阵中的显示,汉字“于”LED点阵显示如图5-6-1所示:

图5-6-1 汉字“于”LED点阵显示

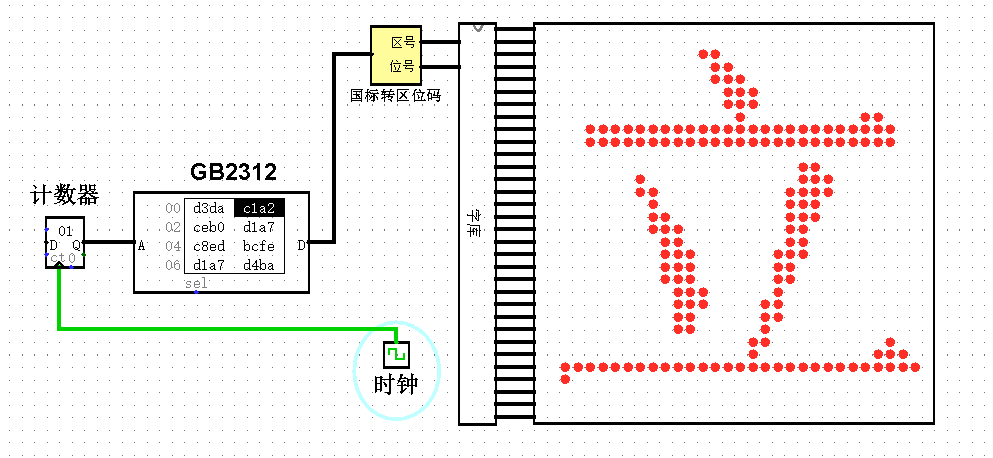

(2)使用机内码与汉字转换软件将汉字“立”转换为机内码,得到对应的机内码为C1A2,然后对只读存储器ROM中的内容进行编辑,将其写进GB2312存储器中,实现汉字“立”在LED点阵中的显示,汉字“立”LED点阵显示如图5-6-2所示:

图5-6-2 汉字“立”LED点阵显示

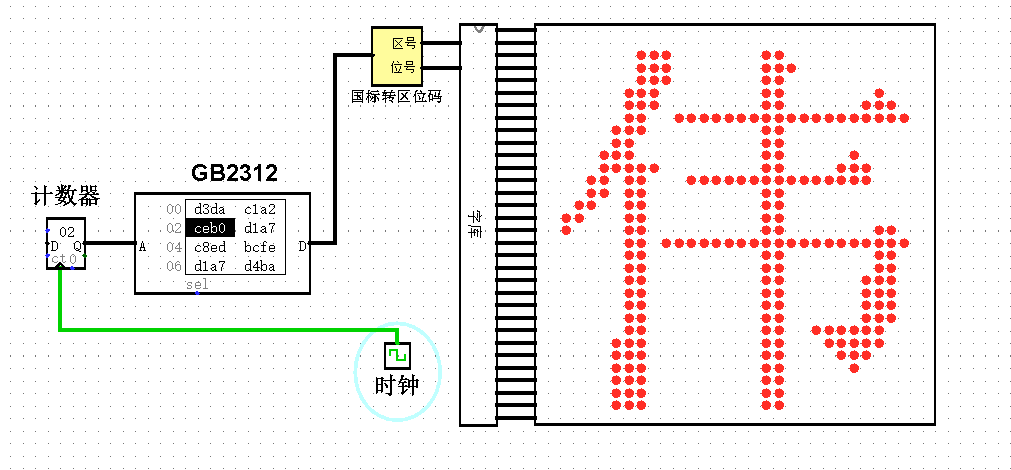

(3)使用机内码与汉字转换软件将汉字“伟”转换为机内码,得到对应的机内码为CEB0,然后对只读存储器ROM中的内容进行编辑,将其写进GB2312存储器中,实现汉字“伟”在LED点阵中的显示,汉字“伟”LED点阵显示如图5-6-3所示:

图5-6-3 汉字“伟”LED点阵显示

六、实验小结

1、问题和解决方法

(1)实验问题:使用逻辑门和相关元素构建逻辑电路后发现有时输出结果与自己的真值表内容不符。

解决方法:观察自己的逻辑电路后发现部分逻辑门的引脚过多,与、或、非等逻辑门的默认引脚的个数为5个,因此我们需要根据自己需要的引脚数量进行设置,将对应的引脚数量改为自己需要的2个引脚后对应问题得到解决。

(2)实验问题:在对逻辑门进行连线的过程中发现电路中出现了多余的连线。

解决方法:点击对应多余的连线并进行删除操作或者对该条连线重新进行勾连。

(3)实验问题:逻辑电路连接完成后发现部分输入端或者输出端是蓝色,且点击输入端进行数值切换对蓝色的输出端无影响。

解决方法:线路没有彻底连接,输入端和输出端的引脚默认朝西,所以在连接电路时要首先将对应端口的引脚方向进行设置,进而方便逻辑电路的正常连接。

(4)实验问题:逻辑电路中有部分区域的连线为红色。

解决方法:由于红色连线前方处于断路状态,逻辑信号无法正常到达后续的逻辑电路之中,因此出现了红色连线,将对应区段的电路连接通路后即可恢复正常。

(5)实验问题:在使用两个以上的异或门进行逻辑电路操作时发现出现了错误。

解决方法:由于Logisim允许指定异或门的逻辑行为,默认是当一个输入为1是输出为1,另一种是奇数个1输入时输出为1,因此在使用过程中需要对默认值进行相应的修改操作,进而避免错误的出现。

(6)实验问题:逻辑电路设计完毕以后,出现了红色或者橘红色的线条,但是自己的逻辑电路没有任何的错误。

解决方法:由于软件本身因素引起的,因此对自己的逻辑电路进行保存,关闭Logisim软件后重新打开对应的逻辑电路文件后即可恢复正常。

2、心得体会

(1)通过使用Logisim软件对逻辑电路进行操作,让我熟悉了相关的逻辑符号及逻辑运算等。其中蓝色的方框表示输入信号;蓝色的圆框表示输出信号;绿色的圆圈加上短横表示锚,主要用于移动和定位。

(2)逻辑电路是用来对数字信号进行逻辑运算,以实现逻辑命题的电路。

(3)组合逻辑电路中电路的输出只与该时刻的输入有关,而时序逻辑电路中电路的输出不仅与该时刻的输入有关,还与电路的原状态有关。

(4)真值表是描述逻辑功能的最底层工具,它是先结构而后内容的,列数据时输入部分从全0到全1,逐个递增。

(5)基本逻辑运算是与、或、非,而常用的复合逻辑为与非、或非、与或非、异或、同或。

(6)逻辑门电路(门电路)用于实现各种的基本逻辑运算、常用符合逻辑运算的电子电路。

(7)两输入异或、同或互为反函数,即非关系。

(8)两输入异或、同或的功能为:

两输入异或,输入取值不同,输出1,输入取值相同,输出0;

两输入同或,输入取值不同,输出1,输入取值相同,输出0.

(9)n输入异或的功能为当输入中有奇数个1时,输出值为1,有偶数个1时输出值为0.

(10)n为偶数时,异或、同或互为非关系;n为奇数时,异或、同或功能相同。

(11)编码器用于编码,使用二进制代码表示具有某种特定含义的信号,即输入信号输出代码。

(12)译码器用于译码,将使用一组代码表示的特定含义翻译出来,即输入代码输出信号。