两个数据表的故事:第 1 部分

在进行印刷电路板 (PCB) 叠层和信号完整性 (SI) 阻抗建模时,我们需要从正确的来源获取介电材料属性。精确阻抗建模的一个重要参数是介电材料的相对介电常数 (εr),也称为介电常数 (Dk)。最好的来源是层压板供应商的数据表。尽管这些存在问题,但我喜欢将其视为“两个数据表的故事”。

如图 1 [6] 所示的示例,营销数据表可以在层压板供应商的网站上轻松找到。它们用于快速比较介电性能,以缩小对适合您应用的层压板的搜索范围。营销数据表上的介电性能主要包括热性能和机械性能,这些特性对于材料的物理结构以及它在加工过程中与叠层中的其他材料性能如何表现非常重要。

但是,市场数据表并不能代表设计实际叠层或进行阻抗和 SI 损耗建模所需的内容。根据玻璃类型,同一层压板的不同芯和预浸料厚度的树脂含量、厚度、Dk 和耗散因数 (Df) 会有所不同。市场数据表通常只报告树脂含量为 50% 和 2 或 3 个频点的典型 Dk/Df。厚度未指定。此外,Dk 和 Df 在频率上不是恒定的。因此,使用这些数据手册中的数字将导致阻抗和相位延迟结果不准确。

图 1.从层压板供应商的网站很容易获得的“营销”数据表示例。来源:Isola Group [6]。

相反,对于传输线建模,需要使用 PCB 制造商用于构建叠层的相同 Dk/Df 表数据表。图 2 显示了一个示例 Dk/Df 表。Dk/Df 表提供了不同类型、不同频率下的实际芯材和预浸料厚度、树脂含量和 Dk/Df。根据叠层的不同,通常需要多种厚度的组合来满足阻抗要求。每种厚度将具有不同的 Dk 值。

在图 2 的示例中,Dk 从 10 GHz 时的 2.92(1080 玻璃样式)到 3.19(10 GHz 时 2116 玻璃样式)不等。这意味着 Dk 变化为 -3.3% 至 5.6%,而图 1 中所示的 10 GHz Dk 为 3.02。

图 2.典型的“工程”数据表示例,其中显示了不同玻璃样式和树脂含量随频率变化的 Dk/Df 表。来源:Isola Group [6]。

许多工程师认为 Dk 公布是材料的固有特性。但实际上,它是通过特定的行业标准测试方法测量的有效 Dk (Dkeff)。当它们与设计应用中的实际测量值进行比较时,由于表面粗糙度引起的相位延迟增加,Dkeff 通常存在差异 [1]。

Dkeff 高度依赖于测试设备和测量条件。许多层压板供应商常用的一种方法是夹紧带状线谐振器测试方法,如 IPC-TM-650 2.5.5.5, Rev C, Test Methods Manual [10] 所述。

由于所有玻璃纤维增强层压板都是各向异性的,因此任何基于带状线的测试方法,如 TM-650 2.5.5.5 或 Bereskin 带状线测试方法 [13],都会报告 Dk 值,其中电场与信号传播垂直。也就是说,如果信号传播在 x-y 轴方向上,那么用这种方法测量的 Dk 就是当 E 场在 z 轴方向上时。

对于 Isola 的 Dk/Df 表 [6],如图 2 所示,Dk 值是通过 TM-650 2.5.5.5 测试方法测量的。根据该数据,计算出大多数结构的值。执行其他验证运行以收集一段时间内的统计数据,并验证计算是否合理和准确。

测量是在带状线条件下使用精心设计的谐振元件图形卡完成的。它由要测试的相同介电材料制成。如图 3 所示,该卡夹在两片未包层的被测介电材料之间。然后将整个结构夹在两块大板之间;每个都衬有铜箔并接地。它们充当带状线的参考平面。

图 3.钳位带状线谐振器测试方法的图示,如 IPC-TM-650、2.5.5.5、Rev C、测试方法手册 [10] 所述。

该测试方法可确保产品在装配板中使用时的一致性。它不保证这些值直接对应于设计应用程序。

原因如下:

由于谐振元件图形卡和被测材料没有物理粘合在一起,因此空气被截留在各个层之间。这些小气隙是由以下原因引起的:

- 夹具中铜箔板的粗糙度

- 从测试样品中去除的箔片上留下的粗糙度剖面印记

- 在 Resonant Element Pattern 卡上去除铜

由于 TM-650 测试方法,空气滞留是使用层压板供应商的 Dk/Df 表进行仿真与设计应用程序的实际测量之间存在有效 Dk 和相位延迟差异的主要原因。小气隙导致有效 Dk 低于在实际 PCB 中测量的 Dk,因为所有东西都被压在一起,没有空气滞留,如图 4 的横截面图所示。

图 4.箔粘合到芯或预浸料电介质的示例。Rz1 比 Rz2 更粗糙,H光滑是电介质的厚度,就像去除了箔一样。

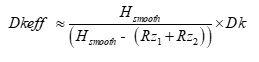

当电介质两侧的铜粗糙度不同时,如图 4 所示,Dkeff 由以下简单校正因子启发式确定:

方程 1.

哪里:

- H光滑是层压板供应商的 Dk/Df 表数据表中的介电芯厚度或 PCB 叠层图中的压制预浸料厚度。

- Rz1 和 Rz2 是箔供应商数据表中电介质各自一侧的箔的导体粗糙度。通常,Rz 是机械轮廓仪测量的 10 点平均粗糙度。

- Dk 是层压板供应商的 Dk/Df 表数据表中的介电常数。

在图 4 中,Rz1 是顶部箔的粗糙度,Rz2 是底部箔的粗糙度。在此示例中,Rz1 比 Rz2 更粗糙。H光滑是电介质的芯厚,如 Dk/Df 表中指定,或预浸料的压制厚度,通常显示在叠层图上。它是电介质的厚度,就好像箔被移除一样。

当具有相同 Rz 粗糙度的铜箔粘合到芯或预浸料的每一侧时,Dkeff 可以简化为:

方程 2

图 5 绘制了 Dkeff 随频率的变化,由 S21 相位或时间延迟 (TD) 得出;Dkeff=(TDc0 ∕ 长度)2 来自 Megtron-6 带状线案例研究 [3]。该方法与 IPC-TM-650 测试方法的不同之处在于,它根据展开的相位延迟确定 Dkeff,而不是根据规范中定义的频率范围内的谐振峰值计算 Dk/Df。

蓝色图是基于 12 GHz 下已发布的 Dk/Df 表中的纤芯和预浸料 Dk 值的模拟情况。当使用公式 2 因粗糙度而校正 Dk 并进行仿真时,Dkeff 显示为粉红色。尽管 Dkeff 有所改进,但它仍然与被测设备 (DUT) 测得的 Dkeff 不一致,如红色所示。

图 5.模拟 Dkeff 与频率与测量的比较。红色图是 DUT 中实际测量的 Dkeff。中间的粉红色图是使用 Dkeff 的模拟,由于粗糙度而进行了校正。底部的蓝色图是使用 Dk/Df 表和非因果粗糙度模型中发布的 12 GHz 的 Dk 进行模拟的。由于粗糙度,绿色虚线图是使用 Dkeff 的模拟;使用了因果 Huray-Bracken 粗糙度模型。使用 Simbeor [11] 建模,并使用 Keysight ADS [12] 进行仿真。

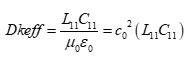

粉红色和红色曲线之间的差异是因为公式 2 中的 Dkeff 仅校正了传输线每单位长度的自电容 (C11) 引起的相位延迟。但是箔的粗糙度也会增加传输线每单位长度的自感 (L11),从而增加额外的相位或时间延迟 [4]。

这是违反直觉的,并且可能会令人困惑,因为我们通常仅将 Dkeff 与电容联系起来。根据定义,Dkeff 是实际结构的电容与电介质被空气取代时的电容之比。但这仅适用于静电场。对于时变电磁场,Dkeff 变得与频率相关 [14]。

如果单条传输线的传播延迟 (tpd)(以每单位长度的秒数为单位)由以下公式确定:

方程 3.

c0 是光速 (~3.0E8 m/s) =1/sqrt(μ0 ε0 );μ0 (4πE−7 H/m) 和 ε0 (8.8542E−12 F/m) 分别是自由空间的磁导率和介电常数,则:

方程 4.

其中:L11;C11 分别是每单位长度的亨利自感和每单位长度法拉的自电容。

公式 4 清楚地表明,随着自感的增加,Dkeff 将成比例增加。这意味着对于 PCB 传输线,计算 Dkeff=(TDc0 ∕ length)2 的计算不能被认为与介电材料的相对介电常数 (εr) 相同。这样做的后果是阻抗预测不准确和非因果时域仿真,从而导致与测量的相关性差。

因果模型在仿真时,在其输入信号发生变化之前,其输出信号不会产生任何变化。当场求解器通过将粗糙度校正因子应用于金属复阻抗的虚部 [4][5] 来正确校正自感时,模型就是因果关系。当与公式 2 中校正的纤芯和预浸料的 Dkeff 相结合时,存在极好的相关性,如图 5 中的绿色虚线图所示。不幸的是,并非所有场求解器都有因果粗糙度模型来校正仿真中的电感。

由于没有简单的方法可以从相位测量回溯以确定用于建模的正确 Dkeff,尤其是对于有损带状线构造,因此启发式方法是一种替代方法。

使用正确的 Dkeff 进行建模可确保正确的时域反射计 (TDR) 阻抗预测,如图 6 所示。红色图是测量的 TDR 差异 [3]。当 Dk/Df 表中的芯和预浸料 Dk 与模拟中的非因果粗糙度模型一起使用时,蓝色图显示阻抗的高估。当方程 2 中的 Dkeff 和非因果粗糙度模型用于仿真时,粉红色图在阻抗图中显示低估。

只有当我们应用[11]中的因果Huray-Bracken粗糙度模型以及公式2中的Dkeff时,我们才能看到自感增加的影响,如图6中的绿色虚线图所示。

乍一看图 6,人们可能会将粉红色图解释为与测得的红色图具有更好的相关性。但是,由于测量的绘图沿其长度存在阻抗纹波,因此很难仅从 TDR 绘图中得出哪个是正确的模型。只有当我们比较从图 5 的绿色虚线相位延迟图得出的 Dkeff 时,我们才能得出绿色虚线 TDR 图是正确的阻抗。

图 6.在模型中使用不同的 Dkeff 时,模拟与测量的差分 TDR 图。蓝色曲线高估了使用数据手册中的 Dk 时的阻抗。粉红色图低估了使用 Dkeff(方程 2)和非因果粗糙度模型时的阻抗。绿色虚线图是使用 Dkeff(方程 2)和因果 Huray-Bracken 粗糙度模型时。使用 Simbeor [11] 建模,并使用 Keysight ADS [12] 进行仿真。

总结:

不能相信市场数据表中的介电常数无法正确设计 PCB 叠层和模拟阻抗和相位延迟的传输线。相反,应使用层压板供应商的 Dk/Df 表。

许多层压板供应商提供源自夹紧带状线谐振器测试方法 [10] 或类似的 Bereskin 测试方法 [13] 的 Dk/Df 表。但这些数字并没有考虑箔片的实际粗糙度。当考虑基于层压板厚度和 Rz 箔粗糙度的简单校正因子时,可以使用更准确的 Dkeff 值以及因果粗糙度模型进行阻抗和传输线建模。

对于 PCB 传输线,根据相位或时间延迟测量方法计算 Dkeff 不能被认为是介电材料的相对介电常数。使用此值将导致模拟结果不准确。