XILINX JESD204B/C IP的AXI配置

高速的ADC和DAC大都是JESD204B/C接口,我们需要对其进行AXI参数配置。已在优数科技的FMC-702/FMC-704/FMC-708上应用。

- 时钟

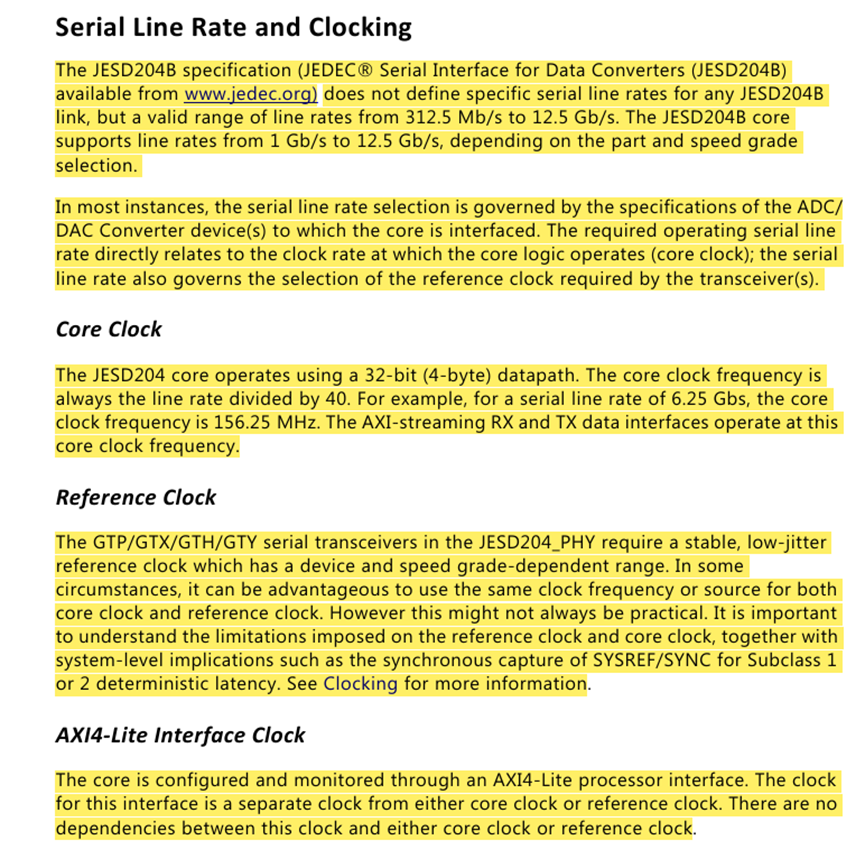

JESD204B规范(www.jedec.org 提供的 JEDEC® 数据转换器串行接口 (JESD204B) )没有定义任何JESD204B链路的特定串行线速,而是定义从 312.5 Mb/s 到 12.5 Gb/s 的有效线速范围。JESD204B 内核支持 1 Gb/s 至 12.5 Gb/s 的线速,具体取决于所选的器件和速度等级。在大多数情况下,串行线速的选择取决于内核所连接的 ADC/DAC 转换器器件的规格。所需的 operating serial line rate 与 core logic 运行的 clock rate (core clock) 直接相关;串行线速率还控制收发器所需的参考时钟的选择。

JESD204B规范(www.jedec.org 提供的 JEDEC® 数据转换器串行接口 (JESD204B) )没有定义任何JESD204B链路的特定串行线速,而是定义从 312.5 Mb/s 到 12.5 Gb/s 的有效线速范围。JESD204B 内核支持 1 Gb/s 至 12.5 Gb/s 的线速,具体取决于所选的器件和速度等级。在大多数情况下,串行线速的选择取决于内核所连接的 ADC/DAC 转换器器件的规格。所需的 operating serial line rate 与 core logic 运行的 clock rate (core clock) 直接相关;串行线速率还控制收发器所需的参考时钟的选择。

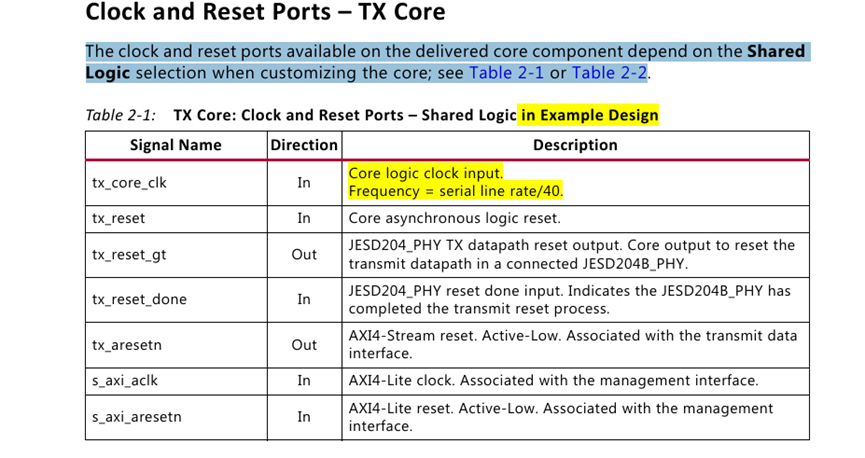

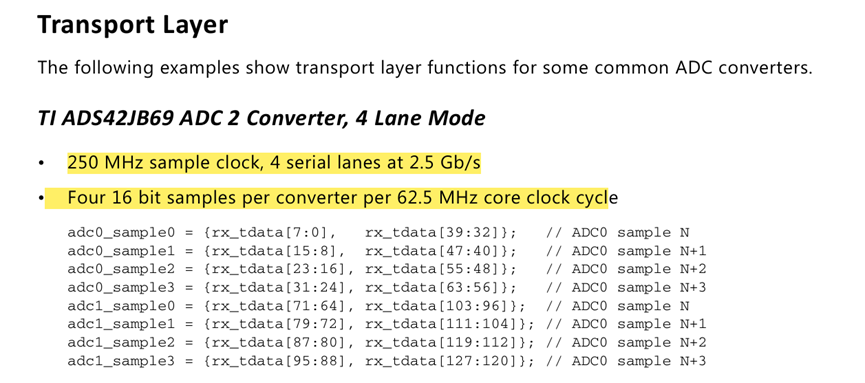

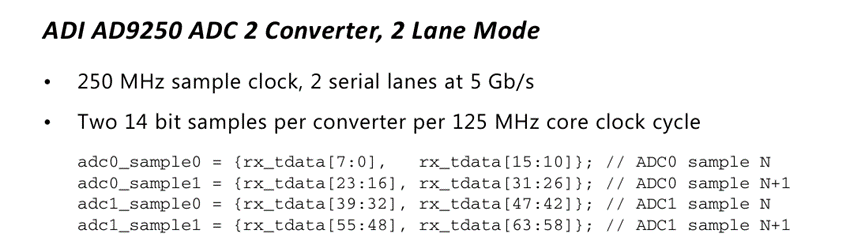

JESD204 内核使用 32 位 (4 字节) 数据路径运行。核心时钟频率始终是线速除以 40。例如,对于 6.25 Gbs 的串行线路速率,核心时钟频率为 156.25 MHz。AXI 流式 RX 和 TX 数据接口在此内核时钟频率下运行。

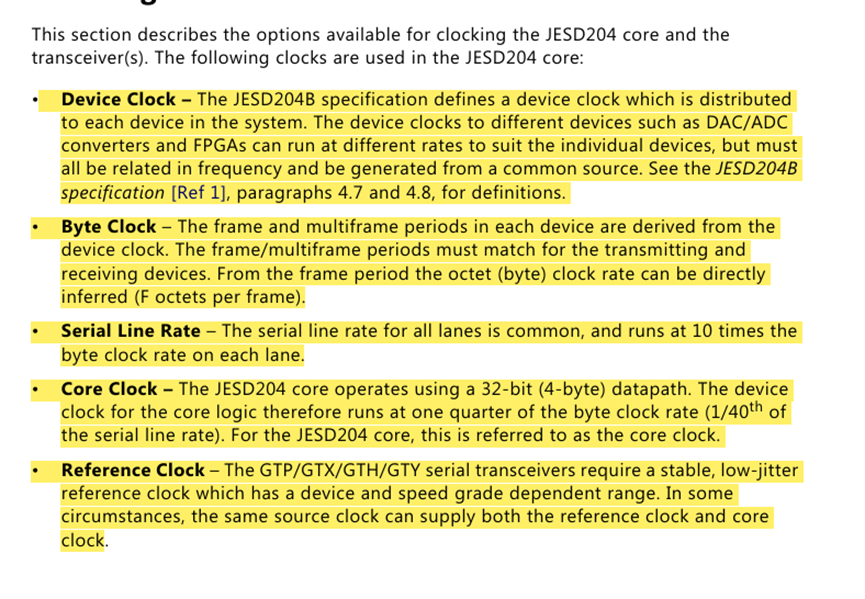

Device Clock (设备时钟) – JESD204B 规范定义了一个设备时钟,该时钟分配给系统中的每个设备。

不同器件(如 DAC/ADC 转换器和 FPGA)的器件时钟可以以不同的速率运行以适应各个器件,但必须在频率上相关,并由公共源生成。有关定义,请参见 JESD204B 规范 [参考文献 1] 第 4.7 和 4.8 段。

• 字节时钟 – 每个设备中的帧和多帧周期派生自设备时钟。帧/多帧周期必须与发送和接收设备匹配。从帧周期可以直接推断出八位字节(字节)时钟速率(每帧 F 八位字节)。

• 串行线路速率 — 所有通道的串行线路速率是通用的,并且每个通道以字节时钟速率的10倍运行。

• Core Clock – JESD204 内核使用 32 位(4 字节)数据路径运行。因此, core logic 的 device clock 以字节 clock rate 的四分之一 (serial line rate 的 1/40) 运行。对于 JESD204 内核,这称为内核时钟。

• 参考时钟 – GTP/GTX/GTH/GTY 串行收发器需要一个稳定、低抖动的参考时钟,该时钟具有与设备和速度等级相关的范围。在某些情况下,同一个源时钟可以同时提供参考时钟和内核时钟

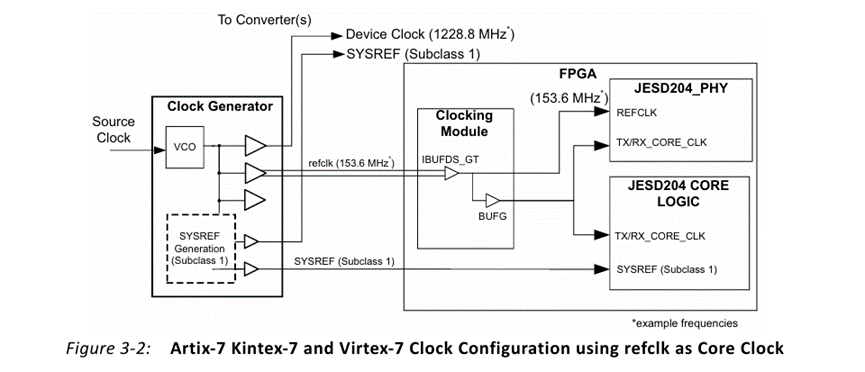

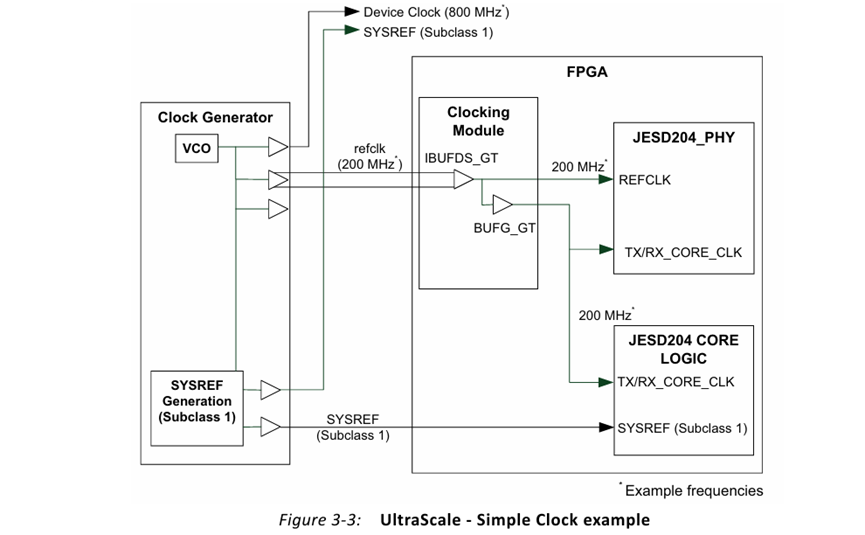

- 时钟分配

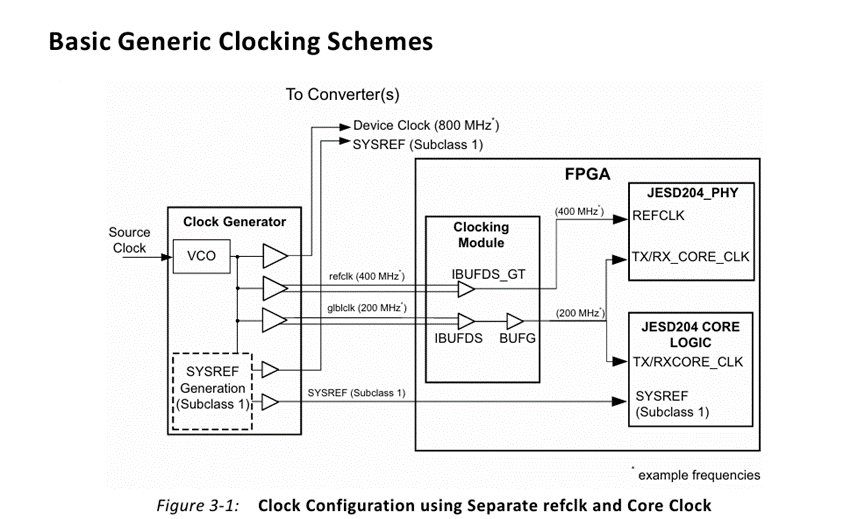

图 3-1 显示了最通用和灵活的 clocking scheme,其中单独的 refclk 和 glblclk inputs分别用于提供收发器参考时钟和核心时钟。通过这种配置, reference clock 和 core clock 在物理上是独立的 clocks,可以在独立的频率上运行,没有额外的限制。对于所选线速,reference clock 可以在 transceiver 限制内的任何频率运行。内核时钟始终以所需的速率(串行线速的 1/40)运行。

- mgt_clk

JESD204 内核使用 32 位 (4 字节) 数据路径运行。核心时钟频率始终是线速除以 40。例如,对于 6.25 Gbs 的串行线路速率,核心时钟频率为 156.25 MHz。AXI 流式 RX 和 TX 数据接口在此内核时钟频率下运行。

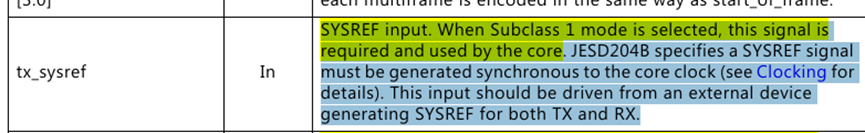

- sysref_clk

SYSREF 输入。当选择 Subclass 1 模式时,此信号是必需的,并且由 core 使用。JESD204B 指定 SYSREF 信号必须与 core clock 同步生成(有关详细信息,请参阅 Clocking )。此输入应由为 TX 和 RX 生成 SYSREF 的外部器件驱动。

- sysref握手配置

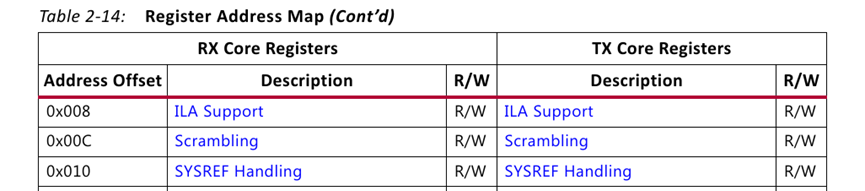

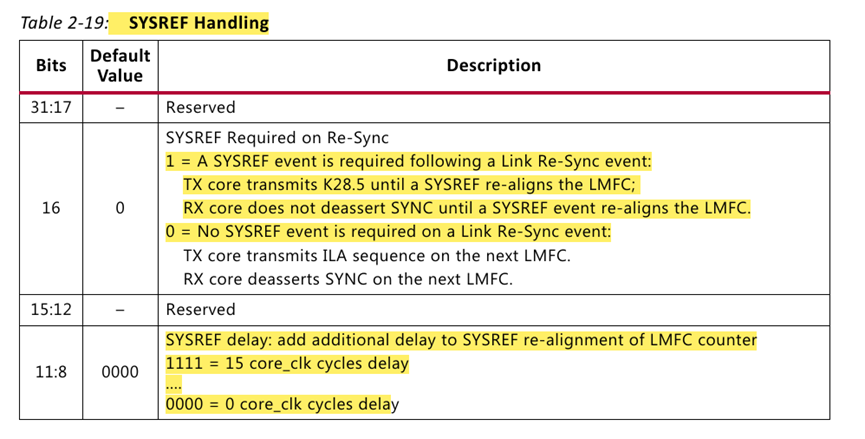

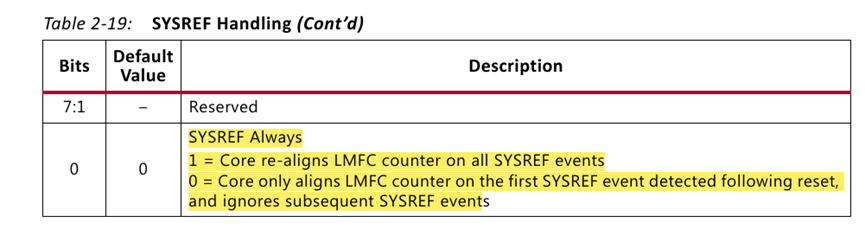

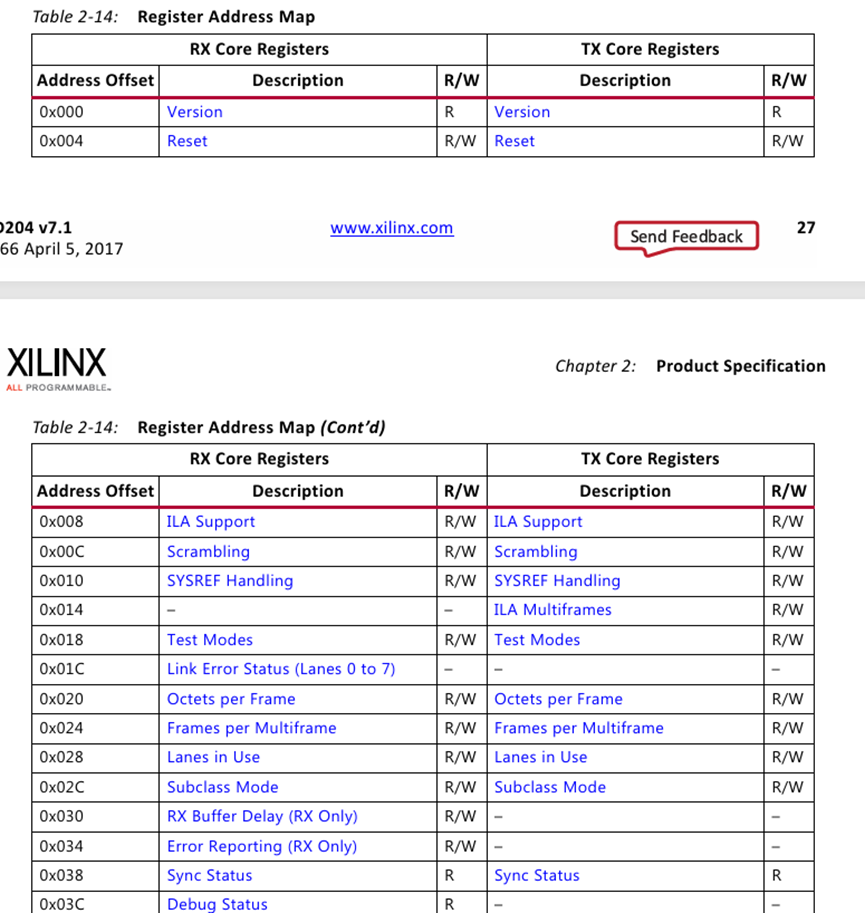

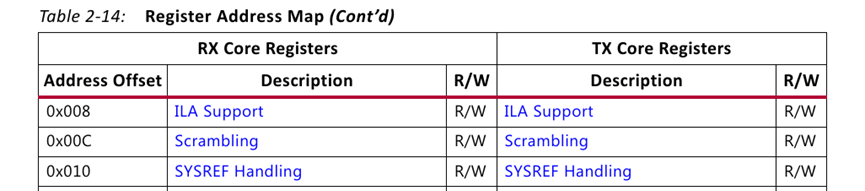

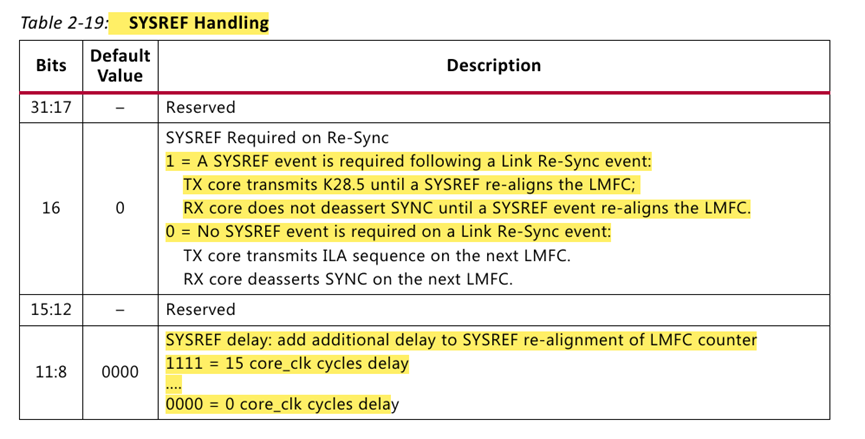

通过axis_lite总线配置寄存器0x010,来配置sysref_clk握手模式

Bit16:

1 = 链路重新同步事件后需要 SYSREF 事件:TX 内核传输 K28.5,直到 SYSREF 重新对齐 LMFC;RX core 在 SYSREF 事件重新对齐 LMFC 之前不会置低 SYNC。

0 = 链路重新同步事件不需要 SYSREF 事件:TX 核心在下一个 LMFC 上传输 ILA 序列。RX 内核在下一个 LMFC 上置低 SYNC。

Bit[11:8]:

SYSREF 延迟:为 LMFC 计数器 1111 = 15 core_clk 周期延迟的 SYSREF 重新对齐添加额外的延迟。0000 = 0 core_clk 周期延迟

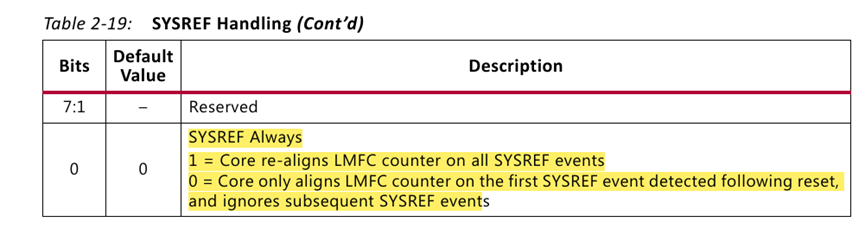

Bit0:

1 = 内核在所有 SYSREF 事件上重新对齐 LMFC 计数器

0 = 内核仅在复位后检测到的第一个 SYSREF 事件上对齐 LMFC 计数器,并忽略后续 SYSREF 事件

- Tx/Rx_Sync

- LINE相关描述

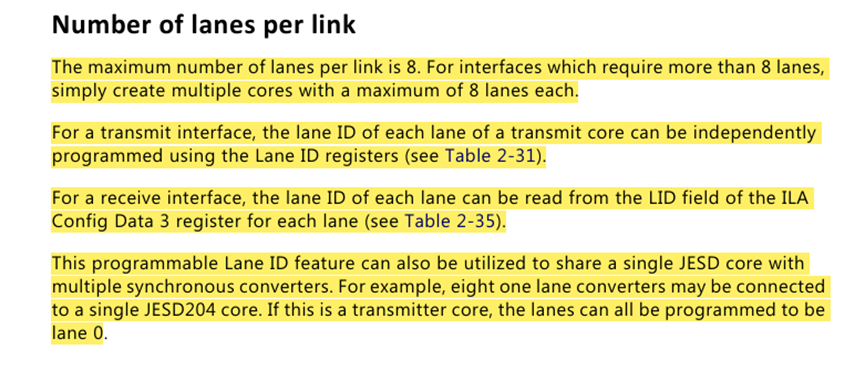

每个链路的最大通道数为 8。对于需要 8 个以上通道的接口,只需创建多个内核,每个内核最多 8 个通道即可。对于发送接口,发送内核每个通道的通道 ID 可以使用 Lane ID 寄存器独立编程(参见表 2-31)。对于接收接口,可以从每个通道的 ILA Config Data 3 寄存器的 LID 字段中读取每个通道的通道 ID(见表 2-35)。这种可编程 Lane ID 功能还可用于与多个同步转换器共享单个 JESD 内核。例如,八个单通道转换器可以连接到一个 JESD204 内核。如果这是 transmitter core,则所有通道都可以编程为通道 0

- JESD IP 的模式配置寄存器

通过axis_lite总线配置寄存器0x010,来配置JESD204的模式

- SYSref握手模式配置(0x010)

Bit16:

1 = 链路重新同步事件后需要 SYSREF 事件:TX 内核传输 K28.5,直到 SYSREF 重新对齐 LMFC;RX core 在 SYSREF 事件重新对齐 LMFC 之前不会置低 SYNC。

0 = 链路重新同步事件不需要 SYSREF 事件:TX 核心在下一个 LMFC 上传输 ILA 序列。RX 内核在下一个 LMFC 上置低 SYNC。

Bit[11:8]:

SYSREF 延迟:为 LMFC 计数器 1111 = 15 core_clk 周期延迟的 SYSREF 重新对齐添加额外的延迟。0000 = 0 core_clk 周期延迟

Bit0:

1 = 内核在所有 SYSREF 事件上重新对齐 LMFC 计数器

0 = 内核仅在复位后检测到的第一个 SYSREF 事件上对齐 LMFC 计数器,并忽略后续 SYSREF 事件

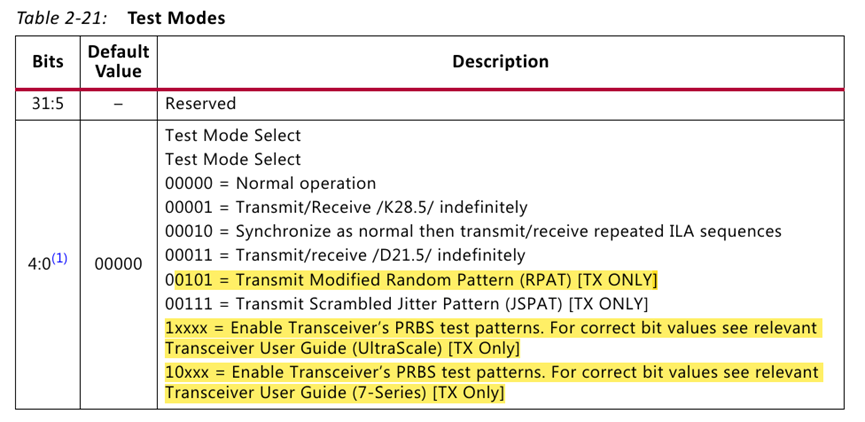

- 测试模式(0x018)

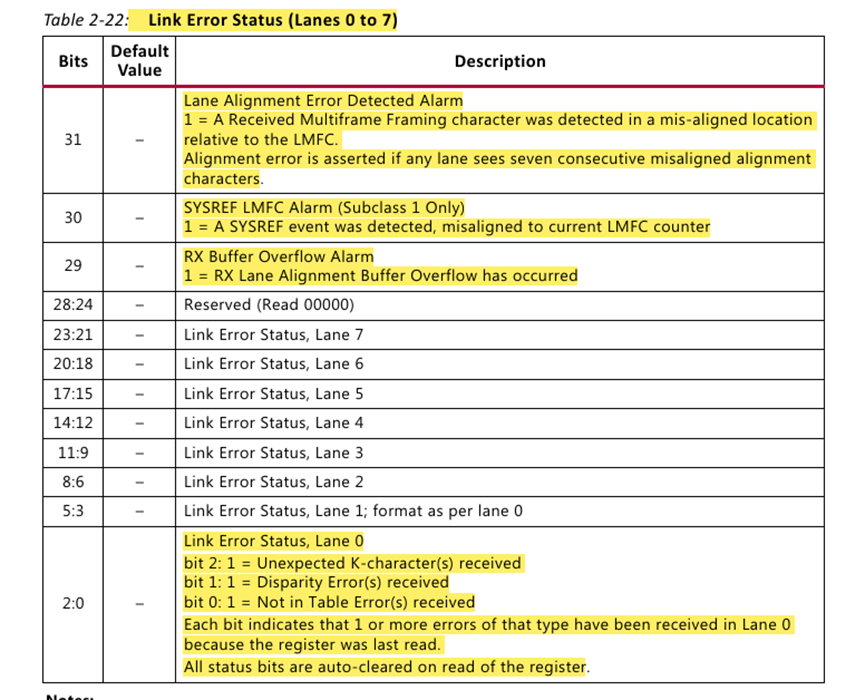

- 错误状态回读

Bit31 :

检测到通道对齐错误警报 1 = 在相对于 LMFC 的未对齐位置检测到接收到的多帧成帧字符。如果任何通道看到 7 个连续未对齐的对齐字符,则断言对齐错误

Bit30:

SYSREF LMFC 警报(仅限子类 1)1 = 检测到 SYSREF 事件,与当前 LMFC 计数不一致

Bit29:

RX 缓冲区溢出警报 1 = 发生 RX 通道对齐缓冲区溢出

Bit[2:0]:

链路错误状态,通道 0

Bit[2:1] = 收到意外的 K 字符

bit1: = 收到异位错误

bit0: = 未在表中收到错误

每个位表示由于上次读取寄存器,在通道 0 中收到了 1 个或多个该类型的错误。所有 status bits 在读取 register时自动清除。

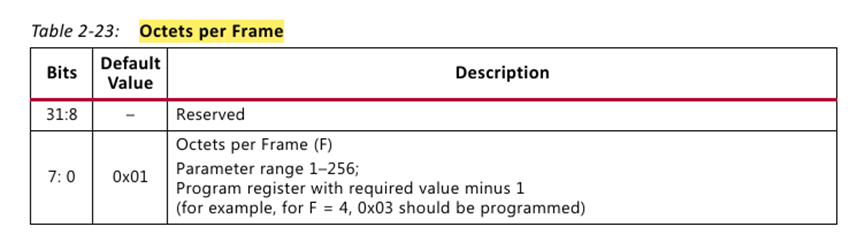

- 每个多帧的帧数/F码()

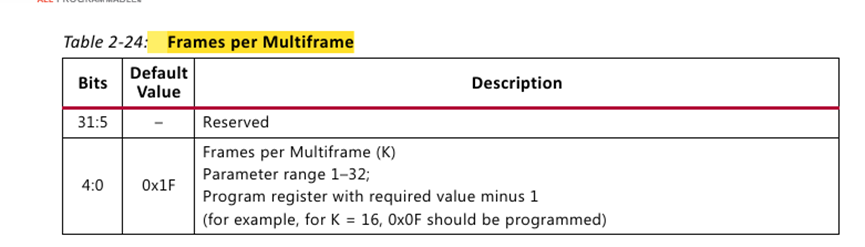

- 每个多帧的帧数/K码()

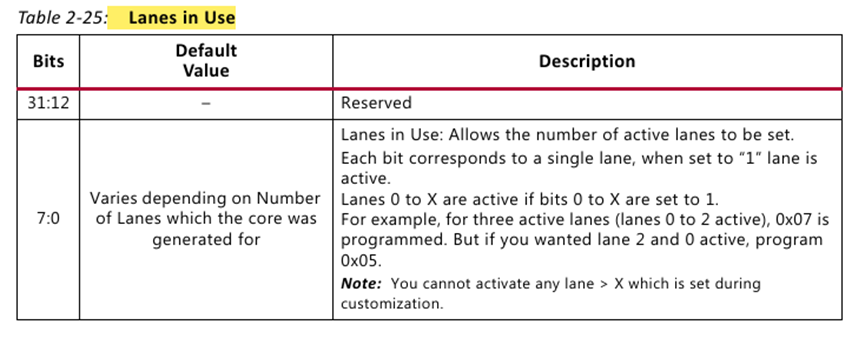

- LINE配置数

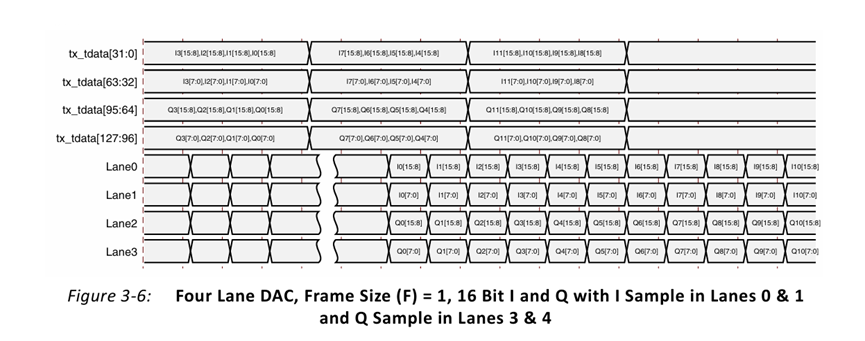

- TX_DATA

- 配置1 (250Msps-line4)

Line_rate = 250Msps * 16bit * 10b/8b / (4line / 2) = 2.5G

- 配置2(250Msps-line2)

- TX_Timing

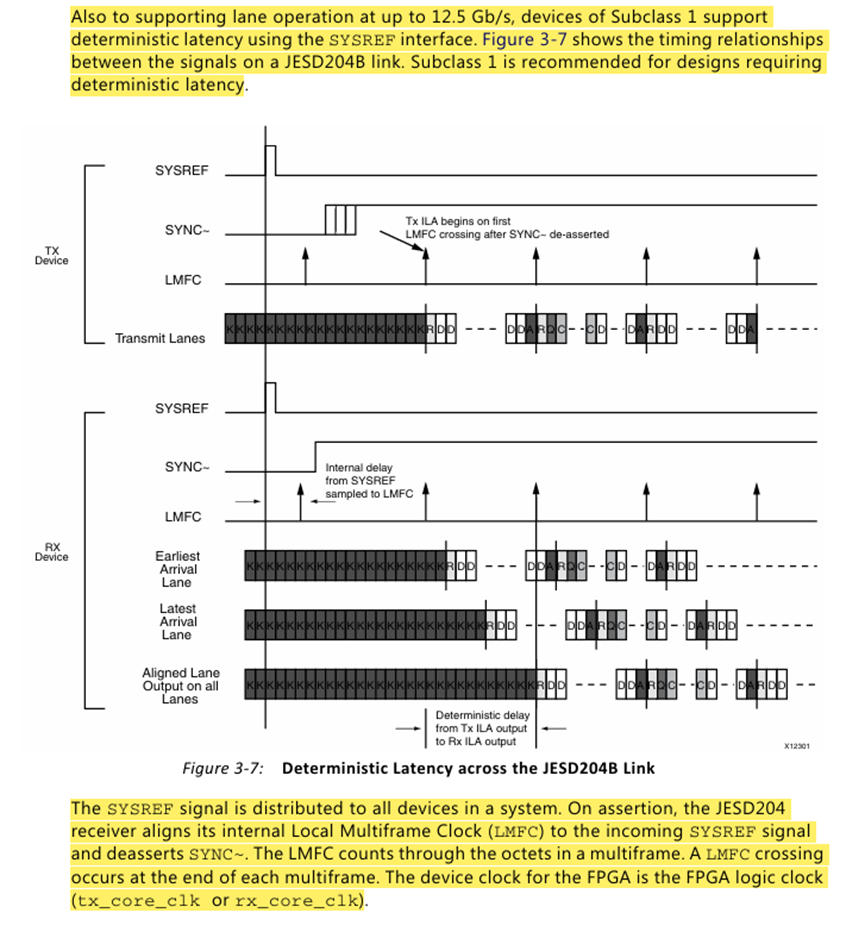

此外,为了支持高达 12.5Gb/s 的通道作,Subclass 1 的器件使用 SYSREF 接口支持确定性延迟。图 3-7 显示了 JESD204B 链路上信号之间的时序关系。对于需要确定性延迟的设计,建议使用子类 1

SYSREF 信号被分配到系统中的所有器件。置位时,JESD204接收器将其内部本地多帧时钟 (LMFC) 与输入的 SYSREF 信号对齐,并置低 SYNC~。LMFC 在多帧中通过八位字节进行计数。LMFC 交叉发生在每个多帧的末尾。FPGA 的器件 clock 是 FPGA logic clock (tx_core_clk 或 rx_core_clk)

- JESD_AXI_LITE读写驱动

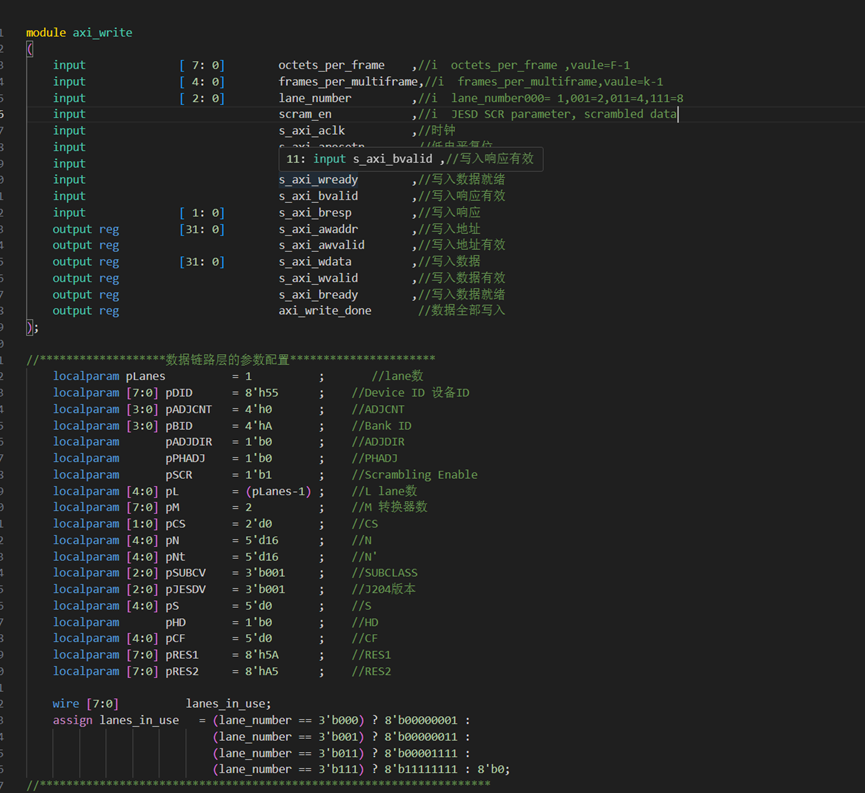

- 写驱动示例

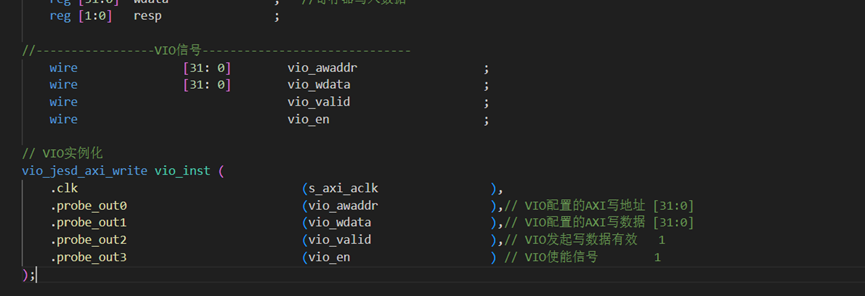

- 写驱动添加VIO,实时控制AXI_LITE

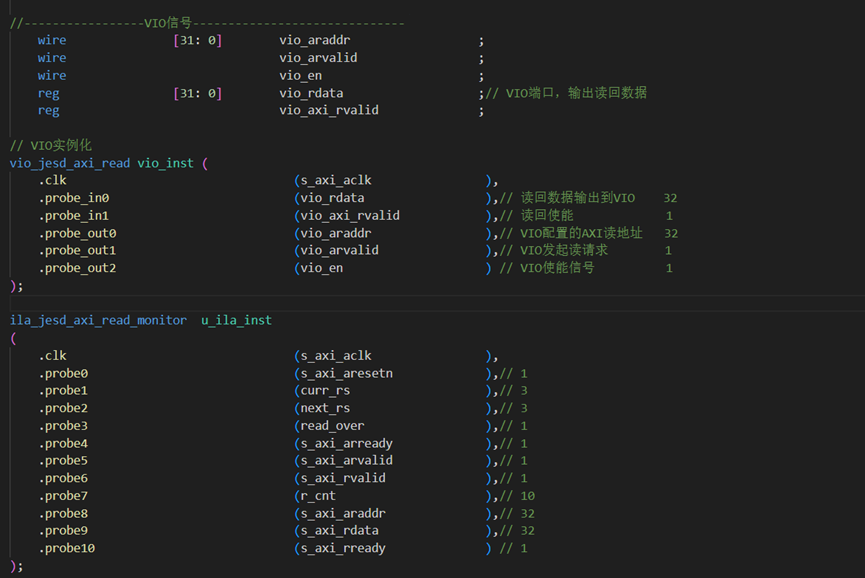

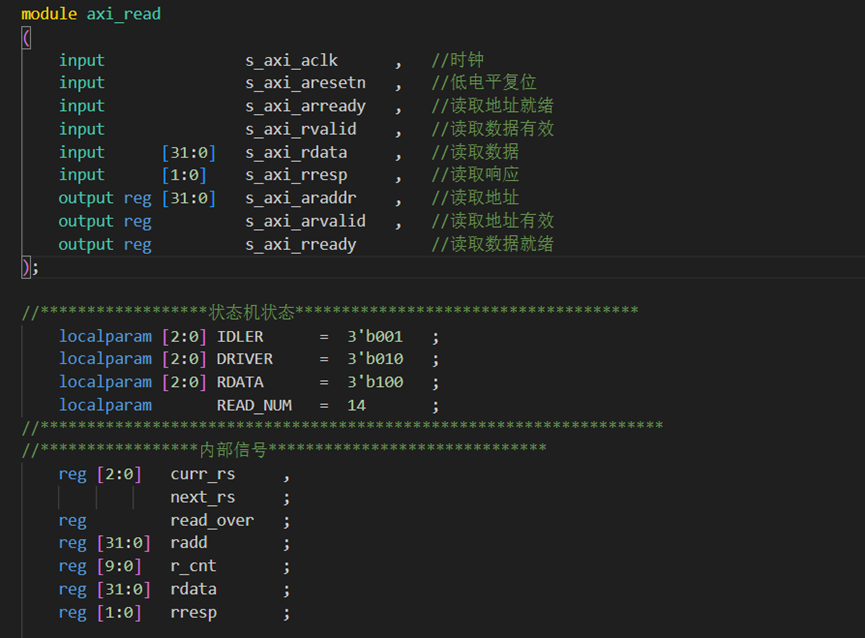

- 读驱动示例

- 读驱动添加VIO,实时获取AXI_LITE的回读数据