门级网标仿真的时钟异常检查

Note:ckg模块出来的给MIPI的500MHz的时钟周期为2ns,50%占空比。

经过chain buffer后,导致占空比严重变形。

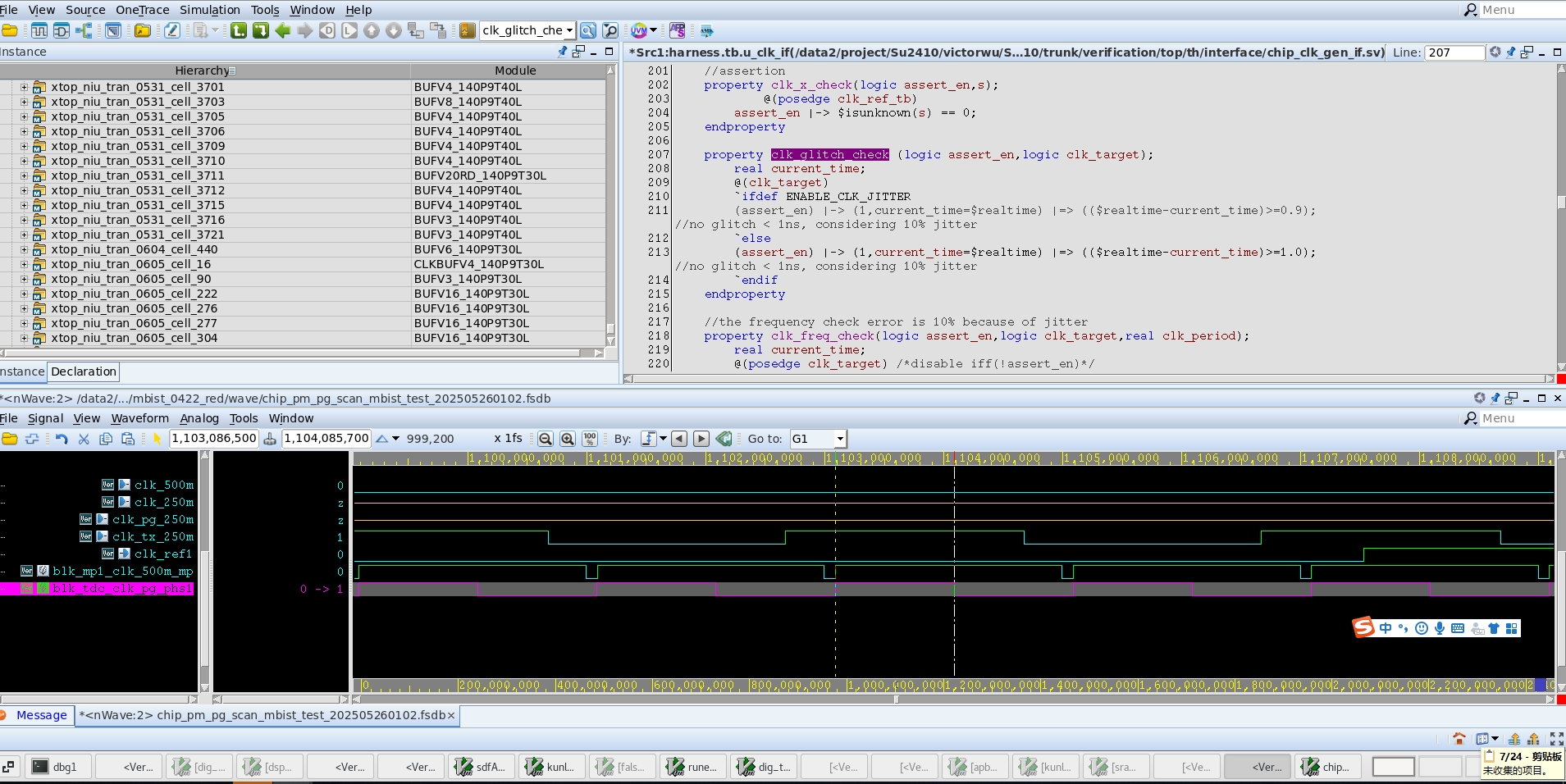

下面的断言进行时钟检查:

//assertion property clk_x_check(logic assert_en,s);@(posedge clk_ref_tb) assert_en |-> $isunknown(s) == 0;endpropertyproperty clk_glitch_check (logic assert_en,logic clk_target);real current_time;@(clk_target)`ifdef ENABLE_CLK_JITTER(assert_en) |-> (1,current_time=$realtime) |=> (($realtime-current_time)>=0.9); //no glitch < 1ns, considering 10% jitter `else(assert_en) |-> (1,current_time=$realtime) |=> (($realtime-current_time)>=1.0); //no glitch < 1ns, considering 10% jitter `endifendproperty//the frequency check error is 10% because of jitter property clk_freq_check(logic assert_en,logic clk_target,real clk_period);real current_time;@(posedge clk_target) /*disable iff(!assert_en)*/`ifdef ENABLE_CLK_JITTER(assert_en) |-> (1,current_time=$realtime) |=> ((($realtime-current_time)<=clk_period*1.10)&&(($realtime-current_time)>=clk_period*0.90)); `else(assert_en) |-> (1,current_time=$realtime) |=> ((($realtime-current_time)<=clk_period*1.05)&&(($realtime-current_time)>=clk_period*0.95)); `endifendpropertyproperty clk_toggle_check(logic assert_en,logic clk_target,real clk_period);@(posedge clk_ref_tb)(assert_en && (0 < clk_period) && (clk_period <= 1000)) |-> ##[0:2000] $rose(clk_target); //only check freq > clk_1mendproperty//not used, phase is checked in testproperty clk_phase_check(logic assert_en,logic clk_phs0,logic clk_phs1,real phs);real current_time;@(posedge clk_phs0)(assert_en) |-> (1,current_time=$realtime) |-> /*delay time*/ ((($realtime-current_time)<=phs*1.05)&&(($realtime-current_time)>=phs*0.95));endproperty