MIPI D-PHYv2.5笔记(5) -- 不同的PHY配置方式

声明:作者是做嵌入式软件开发的,并非专业的硬件设计人员,笔记内容根据自己的经验和对协议的理解输出,肯定存在有些理解和翻译不到位的地方,有疑问请参考原始规范看

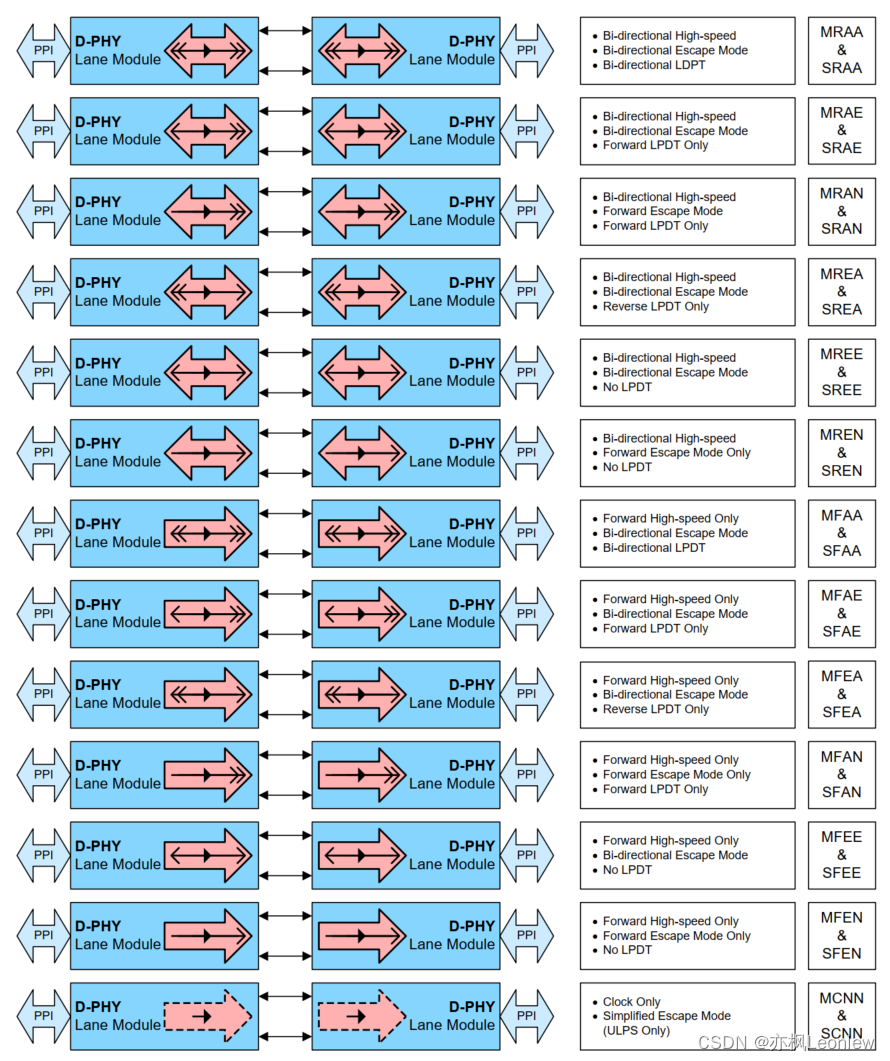

规范5.7章节列举了一些常见的PHY配置,但实际上只要不违反原则,可以扩展出其他很多种PHY配置。

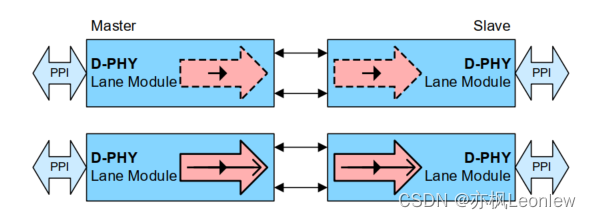

首先要搞明白示例PHY配置的图形所代表的意思,参见下图:

图1 Lane Symbol Macros and Symbols Legend

规范中下图展示了不同Lane类型的符号化表示。

图2 Possible Data Types and a Basic Unidirectional Clock Lane

单向配置(Unidirectional Configurations)

所有单向配置都要有一个Clock Lane以及1个或多个单向Data Lane。有两种基础的配置:单条Data Lane和多条Data Lane配置。如果要完整地来列举,还有一种Dual-Simplex(双单工)配置也被展示了出来。在PHY的层次来看,Dual-Simplex配置和两个独立的单向配置没有什么差异。

Singla Data Lane的PHY配置

这种配置方式,包含了从Master到Slave的一条Clock Lane和一条单向Data Lane,因此只存在Forward Direction通信。

图3 Unidirectional Single Data Lane Configuration

Multiple Data Lanes的PHY配置

这种配置包含了从Master到Slave的一条Clock Lane和多条单向Data lanes。相比于第一种配置,带宽有所增加,但仍然只存在Forward Direction通信。PHY的规范不要求所有Data Lane同时工作。事实上协议层(Protocol layer)独立控制所有Data Lane。如果有N条Data Lanes,那么配置需要2*(N+1)条互联的信号线。

图4 Unidirectional Multiple Data Lane Configuration without LPDT

Dual-Simplex(使用Unidirectional Lanes的双向配置方式)

这种情况和两个独立的(dual)、Unidirectional(simplex)链路的情况是一样的:每个方向上各存在一个完整的单向链路。每个方向上有自己的Clock Lane,可以包含1个或多个Data Lanes。由于两个方向上从概念上看是独立的,因此每个方向上的bit rate不必匹配。但在实际应用中,两条链路最好是能做到速率匹配,并且共享一些内部信号。

图5 Two Directions Using Two Independent Unidirectional PHYs without LPDT

双向半双工配置(Bi-Directional Half-Duplex Configurations)

双向配置包含了一个Clock Lane以及1个或多个双向Data Lane。半双工操作能够让双向数据在共享的互联信号线上进行传递。这种配置和Dual-Simplex配置相比,会节省信号线数量。但是链路上的时间是在正向、反向流量以及Link Truraround之间共享的。在Reverse Direction中,根据定义,其bit rate是Forward Direction的1/4。LPDT在Forward和Reverse Direciton中的速率是差不多的。这种配置对于有非对称数据流量的情况尤其有用。

Singla Data Lane的PHY配置

这种配置包含了一个Clock Lane以及一条任意类型的双向Data Lane。能够允许在Forward和Reverse方向上进行分时复用的数据传输。

图6 Bidirectional Single Data Lane Configuration

Multiple Data Lanes的PHY配置

这种配置包含了一个Clock Lane以及多条双向Data Lanes。每条单独的Lane都能够在Forward和Reverse方向上进行通信。对于每个方向,最大可用的带宽根据Lane的数量而定。PHY规范并不要求所有Data Lanes同时工作,甚至不要求在同一个方向上工作。实际上协议层单独控制着所有Data Lanes。如果有N条Data Lanes,这种配置需要2*(N+1)根互联信号线。

图7 Bi-directional Multiple Data Lane Configuration

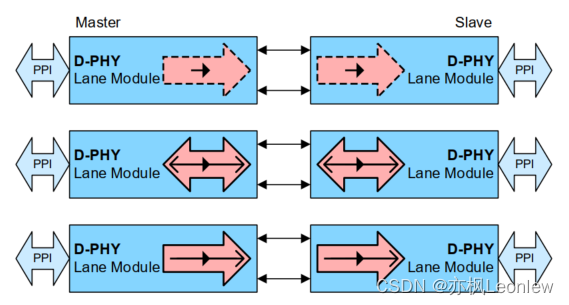

混合型Data Lane配置

PHY配置上也可以组合不同的单向和双向Data Lane到一起。下图展示了一个例子,这个例子中有一条双向Data Lane,一条单向Data Lane,没有LPDT。

图8 Mixed Type Multiple Data Lane Configuration