Aurora 8B/10B

目录

- 1. Overview

- 2. Feature List

- 2. Block Diagram

- 3. Ports Description

- 3.1. User Interface

- Framing Interface

- Streaming Interface

- User Flow Control(UFC)

- Native Flow Control(NFC)

- 3.2. Status and Control Ports

- 3.3. Transceiver Interface

- 3.4. Clock and Reset Ports

本篇blog将介绍由xilinx开发的Aurora 8B/10B链路层协议,并介绍aurora ip使用。

pg046 - Aurora 8B/10B v11.1 LogiCORE IP Product Guide

sp002 - Aurora 8B/10B protocol spec

Xilinx平台Aurora IP介绍(汇总篇)

Aurora 8B/10B IP核(一)——Aurora概述及数据接口

Xilinx FPGA平台GTX简易使用教程(汇总篇)

1. Overview

Aurora 8B/10B协议是一个用于在点对点串行链路间移动数据的可扩展轻量级链路层协议(由Xilinx开发提供)。

该协议能够方便对接GT等高速收发器,在AURORA的基础上可以运行诸如Ethernet和TCP/IP等常用逻辑层协议,或其他自定协议,可扩展性高。

Aurora 8B/10B常用于FPGA之间通信,可应用在多个GT收发器之间传输数据,最多可实现16个GT(包括GTX、GTP、GTH等)。可配置成单工or全双工模式。吞吐量可从480Mbit/s扩展到84.48Gbit/s,取决于GT的数量及线速率。

下图是典型的基于Aurora 8B/10B协议的全双工串行通信流程图。两个aurora channel cores通过多条lanes连接,实现相互通信。

Xilinx的Aurora 8B/10B IP核可以在连接到另一个aurora之后自动初始化链路,并将数据以frame或stream的形式收发。传输的用户数据(Protocol Data Units,PDU)可以是任意大小,aurora会对其进行打包,并通过8B/10B规则进行重编码,以检测错误。如果用户不传输数据,aurora也会发送IDLE数据以保持通信、防止电子干扰。同时可通过流量控制(Flow control)对数据传输速率进行控制。

8B/10B编码是将8bit数编码成10bit数进行传输,以尽量平衡0和1的个数以实现DC平衡,同理还有64B/66B编码。

如果aurora建链失败,或是数据检验错误,将会进行复位并重新建链

2. Feature List

● Aurora 8B/10B协议定义了以下内容:

物理层接口:电气特性、时钟编码、符号编码(symbol coding)

初始化与错误处理:定义了通讯双方通讯前的初始化操作,同样定义了通讯双方在出现错误时的操作(复位和重建链)

数据分段(data striping):定义了通讯数据如何映射到多个通道

链路层(link layer):链路层定义了用户数据的封装方式(帧头、帧尾、pad等)

流控(flow control):流控机制解决通信双方速率不一致所带来的缓存不足的问题

● Aurora 8B/10B协议未定义的内容:

错误指示和恢复:Aurora 8B/10B协议没有定义检测用户pdu错误的机制,也没有定义在8B/10B编码之外从错误中恢复的机制

数据交换:Aurora 8B/10B协议没有定义寻址方案,因此不能支持链路层复用或交换

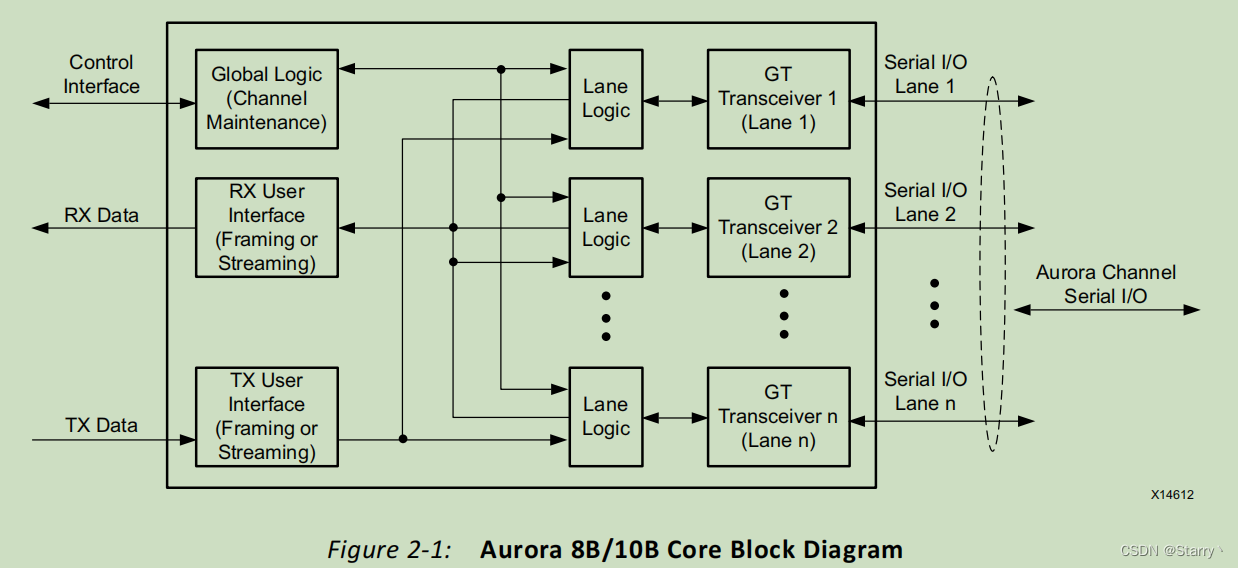

2. Block Diagram

Aurora 8B/10B IP核如下图所示

其中

Lane Logic: 每条Lane都包含一个GT,每个Lane驱动1个GT,可实现处理编解码及错误检测等。

Global Logic: 执行通道初始化的绑定和验证阶段。 可生成Aurora协议所需的随机空闲字符,并监控所有lane逻辑模块的错误。

RX User Interface: 接收端用户接口,使用AXI4-Stream格式将数据从channel传到用户端,并可进行接收流控。

TX User Interface: 发送端用户接口,使用AXI4-Stream格式将数据从用户端传到channel,并进行发送流控功能。核中具有标准时钟补偿(Clock Compensation)模块,可实现时钟补偿字符的周期性传输。

3. Ports Description

3.1. User Interface

用户层接口是基于AMBA AXI4-Stream格式进行交互的,也可添加流控功能。

启用以下接口需要在IP核中设置

高级可拓展接口 4.0 - 流传输(Advanced eXtensible Interface 4 - Stream, AXI4-Stream)

Framing Interface

| Group | Signal | Direction | Width(bits) | Clock Domain | Description |

|---|---|---|---|---|---|

| USER_DATA_S_AXI_TX | s_axi_tx_tdata | input | 8n | user_clk | 发送数据。此处n表示待发送数据的字节数,且n=Lane个数×Lane位宽 |

| s_axi_tx_tready | output | 1 | user_clk | ||

| s_axi_tx_tlast | input | 1 | user_clk | ||

| s_axi_tx_tkeep | input | n | user_clk | 指示数据中哪个字节是有效的,仅在last拉高时该数据有效 | |

| s_axi_tx_tvalid | input | 1 | user_clk | ||

| USER_DATA_M_AXI_RX | m_axi_rx_tdata | output | 8n | user_clk | |

| m_axi_rx_tlast | output | 1 | user_clk | ||

| m_axi_rx_tkeep | output | n | user_clk | 指示数据中哪个字节是有效的,仅在last拉高时该数据有效 | |

| m_axi_rx_tvalid | output | 1 | user_clk |