VHDL语言基础-组合逻辑电路-加法器

目录

加法器的设计:

半加器:

全加器:

加法器的模块化:

四位串行进位全加器的设计:

四位并行进位全加器:

串行进位与并行进位加法器性能比较:

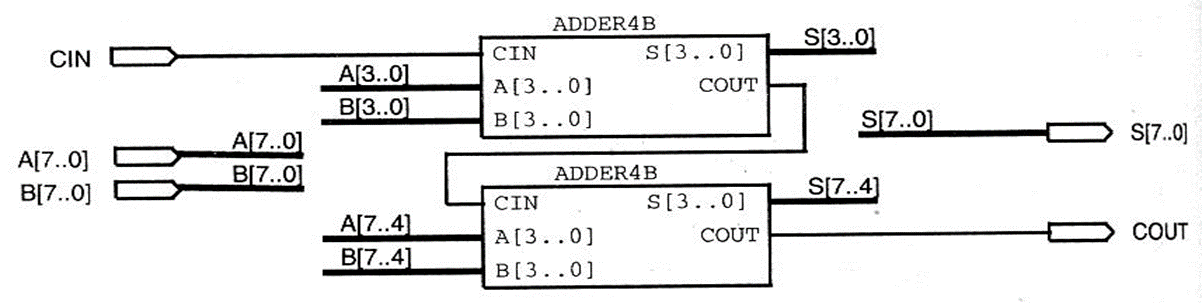

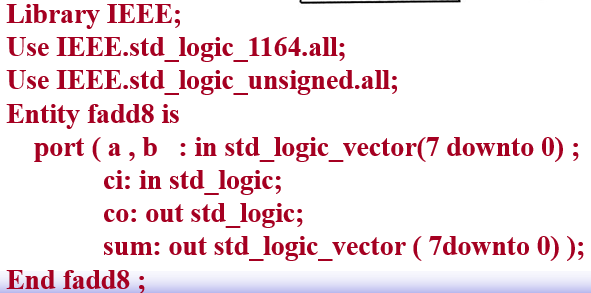

8位加法器的实现:

加法器的设计:

在数字系统中,常需要进行加、减、乘、除等运算,而乘、除和减法运算均可变换为加法运算,故加法运算电路应用十分广泛,另外,加法器还可用于码组变换,数值比较等,因此加法器是数字系统中最基本的运算单元。

加法在数字系统中分为全加和半加,所以加法器也分为全加器和半加器。

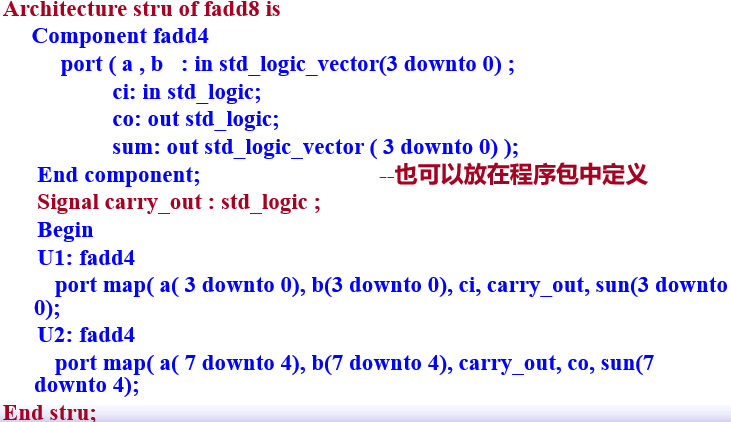

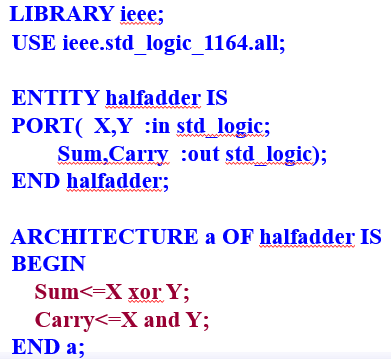

半加器:

不考虑由低位来的进位,只有本位两个数相加,称为半加器。

半加器不考虑低位向高位的进位,因此它只有两个输入端和两个输出端。

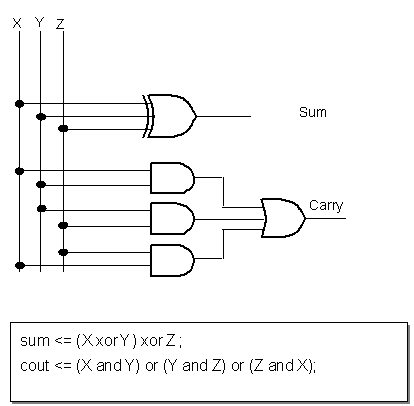

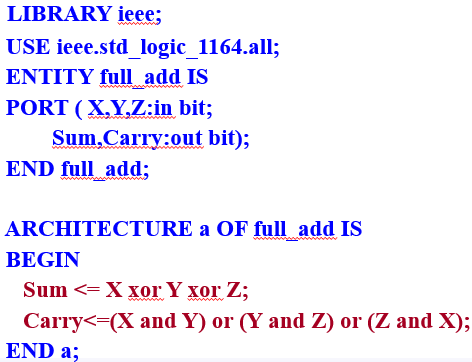

全加器:

除本位两个数相加外,还要加上从低位来的进位数,称为全加器

全加器考虑低位向高位的进位,所以它有三个输入端和两个输出端。

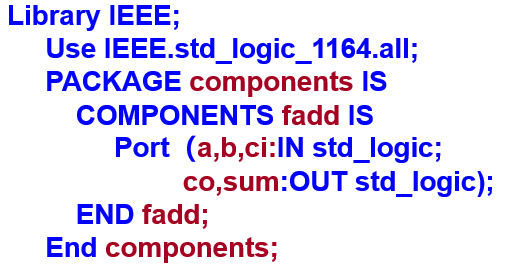

加法器的模块化:

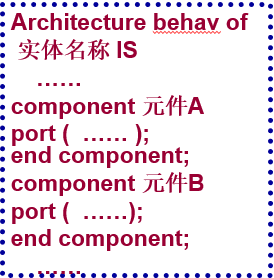

当全加器设计完成后,采用模块化设计方法,将全加器作为一个组件(component)定义,加入名为component的程序包中,以后可以统一将设计的组件放在这个程序包中。

四位串行进位全加器的设计:

l根据模块化设计思想,多位的加法器可将全加器作为一个基本组件多个级联,如图所示。

l在设计中,使用Component语句,与Port Map语句结合可以让我们像堆积木一般搭建出较为复杂的电路

四位串行进位全加器的实现:

四位并行进位全加器:

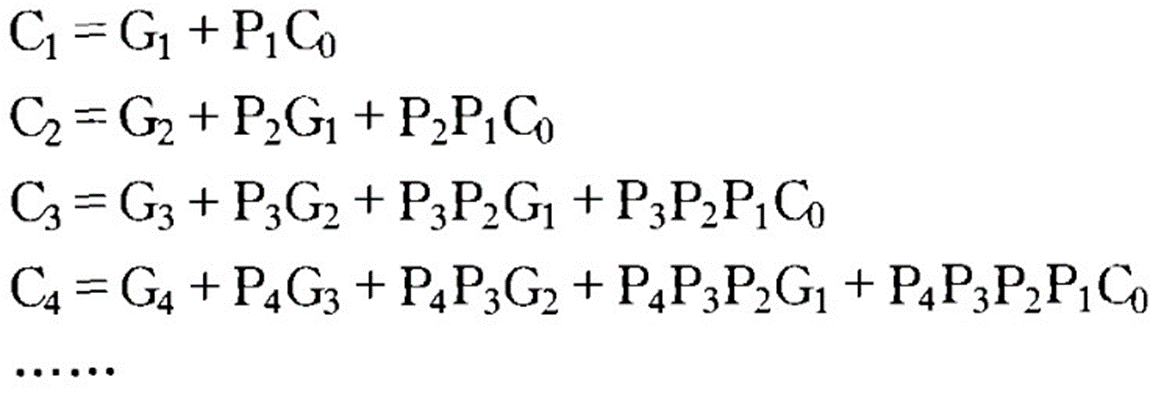

串行进位加法器,在每一位的计算时,都在等待前一位的进位,因此,位数越多,速度越慢。那是否能先考虑进位的输出?并行进位的思想在于各级进位信号同时产生,大大减少了进位产生的时间。其进位的逻辑表达式为:

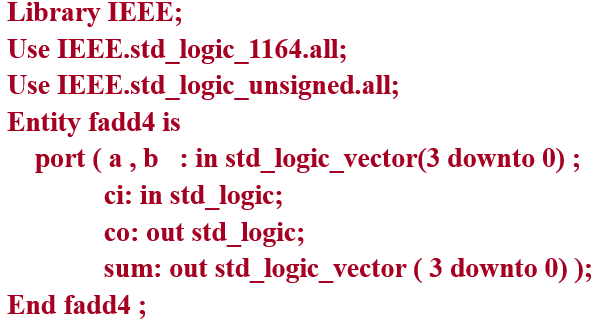

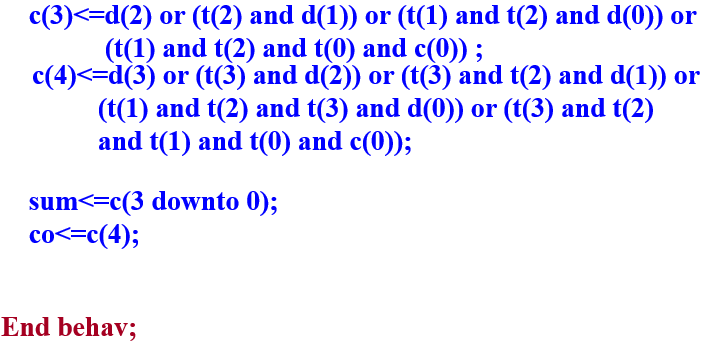

四位并行进位全加器的实现:

串行进位与并行进位加法器性能比较:

1.串行进位方式是将全加器级联构成多位加法器。

2.并行进位加法器设有并行进位产生逻辑,运算速度较快。

3.并行进位加法器通常比串行级联加法器占用更多的资源,随着位数的增加,相同位数的并行加法器与串行加法器的资源占用差距快速增大。因此,在工程中使用加法器时,要在速度和占用资源间寻找平衡。

4.实践表明,4位并行加法器和串行级联加法器占用几乎相同的资源,所以多位加法器(例如8位)可以由4位并行加法器级联构成。

8位加法器的实现: