晶片与电路板的桥梁-封装

俗话说得好:『婆媳之间的桥梁是老公,沟通得好,人生幸福美满。 』同样地,晶片与电路板(PCB)之间的桥梁,是封装(Package)。封装设计得好,老板荷包满满。老公表示:『😐』」

刚踏入半导体产业时,对「封装」这个词既熟悉又陌生。熟悉是因为常听到,尤其在股市新闻中看到「国内XX封装大厂营收创新高!」等利多消息;但对技术知识却是一片空白。听到什么QFP、QFN 只能一脸茫然,更别提BGA 或近期因台积电和辉达走红的「先进封装」了。不过有趣的是,随着股价狂飙,很多股市网红也摇身一变成了「先进封装专家」了😆。

股市网红介绍先进封装示意图

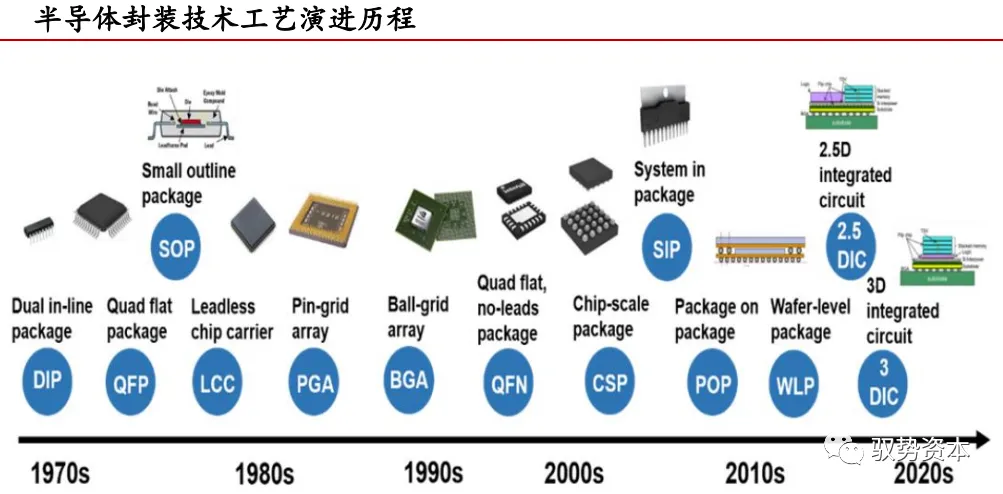

封装的发展从早期的DIP到现在的3D IC [1][2],封装的种类也算是百家争鸣,光QF系列就可以发展出一大串QFN(无脚)、QFP(有脚)...。光是在产品的应用种类上就有很多的选择[3],每种类型的封装都有其优缺点,与应用场景。

半导体封装发展历史[2]

当时看到这么多种类的封装型式,心凉了,摸了摸自己的头,好像有点晕,感觉自己不适合半导体产业。但实际接触后,发现其实封装再怎么变化,最后都是要连接到电路板(PCB)上的,常见的就只有两种封装Base,Leadframe与BGA (Ball Grid Array)。和晶片的IO pin怎么连接出来,常见的连接方式有bond wire和flip chip。 (我这里谈的是基本连接方式,当然有些人也会把Interposer、TSV、Substrate定义成连接方式也可以,毕竟封装每家公司都有不同的定义。)

晶片的连接技术

要了解封装,就要先从裸晶( Die)来说起。晶片的连接主要分成引线键合(Wire Bond)与倒装晶片(Flip Chip)连接技术为主。

引线键合(Wire Bond)

Wire Bond就是将裸晶上的bond pad与封装内的导线架(Lead frame)或基板(substrate)上的Finger Pad用细金属线连接起来的技术。目前键合的方式有热压、超音波和热压超音波键合(不要怀疑,就是前面两个技术相加XD)。

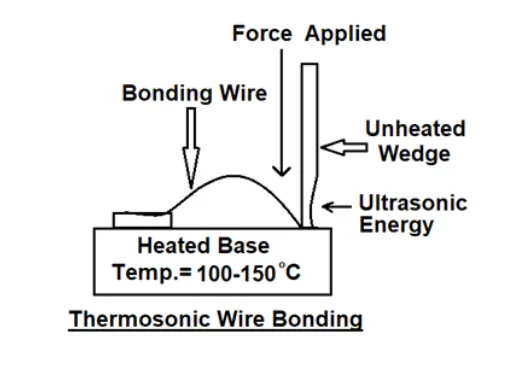

这里就稍微说明热压超音波键合技术,热压超音波键合是目前业界主流的键合技术。该技术结合了超音波振动与加热的双重机制,在超音波键合过程中,透过金属线与焊垫(Bond Pad)之间的弹性振动,破坏接触表面的氧化层,同时产生热量,使两者形成牢固的接合。

此外,加热板(Heated Base)与劈刀(Wedge)同步加热至约150°C,有助于金属间原子在接触界面的相互扩散,进一步增强分子间的作用力,从而提升键合点的强度与稳定性。这里仅做简单说明,有兴趣可以参考文献[4],示意图如下:

热压超音波键合技术[4]

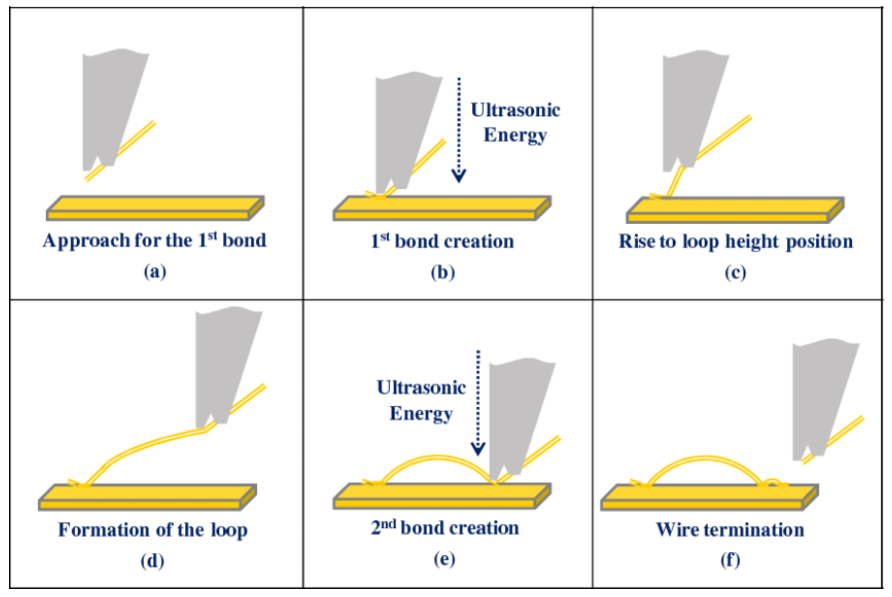

Bonding步骤[5]

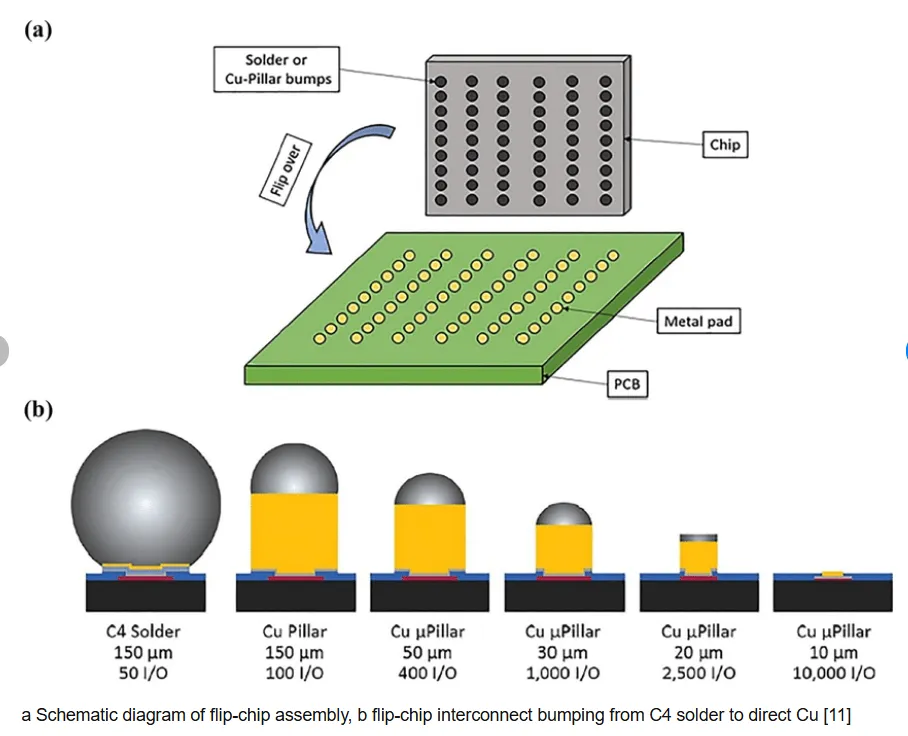

倒装晶片(Flip Chip)

Flip Chip顾名思义,就是将晶片上的凸点(Bump)倒装后,直接连接到基板(Substrate)或PCB板上。至于Bump的种类,这里不做详细讨论,目前业界常见的类型主要分为C4 Bump与Copper Pillar两种。简单来说,Copper Pillar外加了铜柱结构,可以增加高度,相较于C4 Bump具有更小的间距,因此能在相同尺寸的晶片(Die)上容纳更多的I/O Pad,进一步提升元件的连接密度与设计灵活性。

Schematic diagram of flip-chip assembly[6]

封装种类

谈完连接方式,接着再看封装种类就会清楚很多。大致可以分成三大类来说明,Lead frame封装、BGA封装、复杂结构封装。

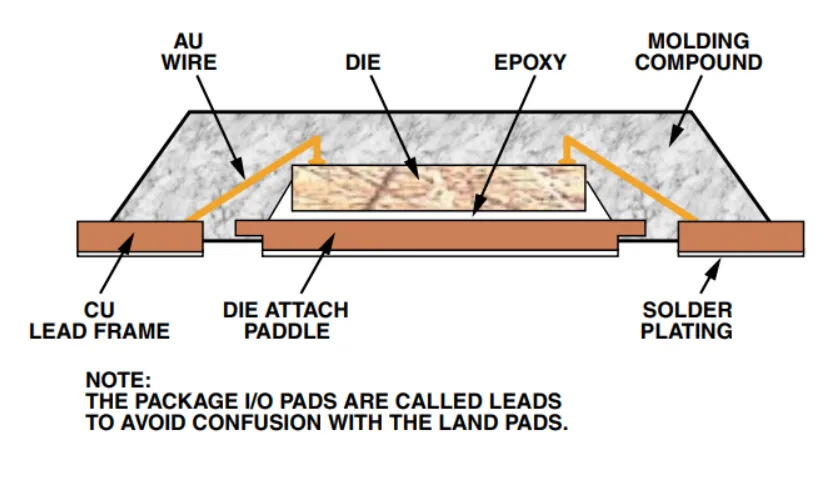

Lead frame封装

导线架封装可以说是封装的始祖,也是结构相对简单而且历久弥新,全靠便宜耐用撑起这个称号。从最阳春的TO封装发展到DIP、SO系列、QF系列,详细可以参考ASE的资料与文献[7][8]

Cross Section of the LFCSP [9]

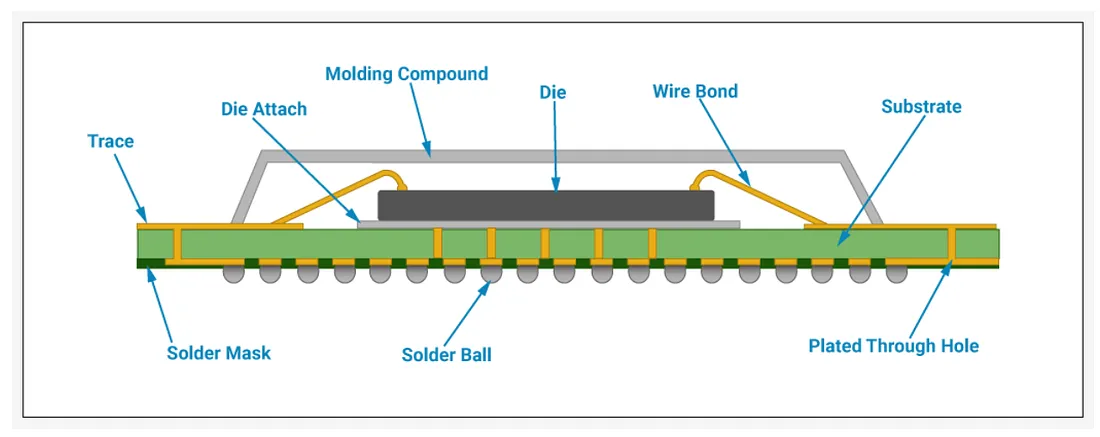

BGA封装(球栅阵列封装)

晶片封装会发展到BGA的型态,主要是现在晶片的IO数越来越多,所需要引出的引脚越来越多。加上传输的Data rate越来越高,要求封装的电感越来越小,若使用导线架会有很大的风险会Fail。 BGA的外观差异不大,但种类非常多,像是Die是Fan in还是Fan out,有没有用Substrate或是用PI tape的方式,还有面板级封装与晶圆级、传统封装制程,就可以分成很多名词种类。举个例子TFBGA(Thin and Fine Ball Grid Array),就是封装厚度很薄且BGA的Ball pitch是更精细。至于产品要用什么封装取决于Die的尺寸、IO数量与功能等。

这个时候或想说,这么多封装,怎么记得起来?其实可以将封装拆成三个部件来看,Die的连接方式、转介基板或Type(PS. 其实转介方式就两个方向,往Die发展就是RDL、interposer;往PCB发展就是基板发展FR4、BT、ABF...)、连接到电路板。用这个三个部件透过不同的组合在转换而已,最后再用Molding包起来。

封装逻辑

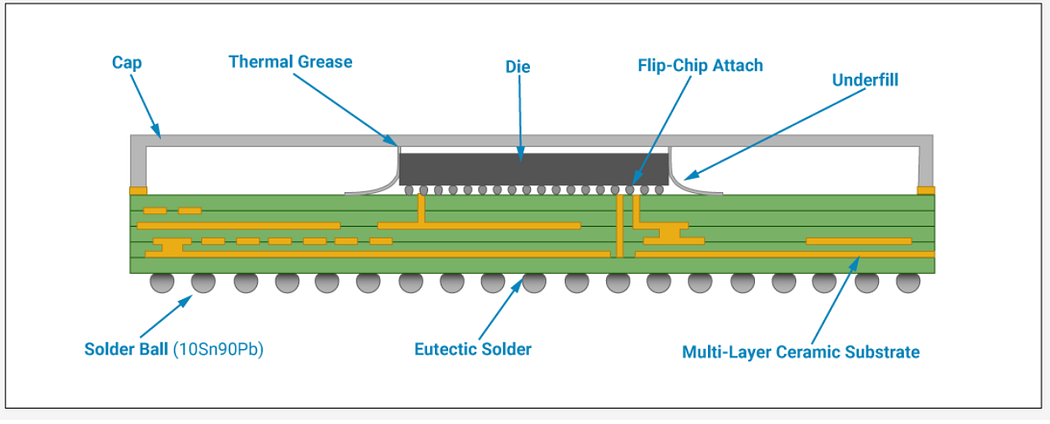

举个常见封装例子,使用连接方式有bond wire、Flip Chip有两种方式,Die到PCB有使用基板,连接到电路板是使用BGA base,就是常见的Wire bond BGA和Flip chip BGA这两种封装,如下图:

Die connected to BGA with bond wire [10]

Die connected to BGA using flip chip [10]

这时候会想原来这么简单啊,但怎么没看过Lead frame封装用Flip chip的方式连接。确实是没有。主要是这样做不合逻辑,先不谈Lead frame能不能Bumping上去(但好像是可以做的),光成本就不符合逻辑,有点杀鸡用牛刀的概念。这里只是简单的去分类封装技术,事实上封装是一个很专业的领域,尤其是在制程上,能想得出来跟做出来,是两个不同维度的事情。后续在看复杂结构会更有感觉,做封装跟做晶圆一样,不容易啊。

复杂结构封装

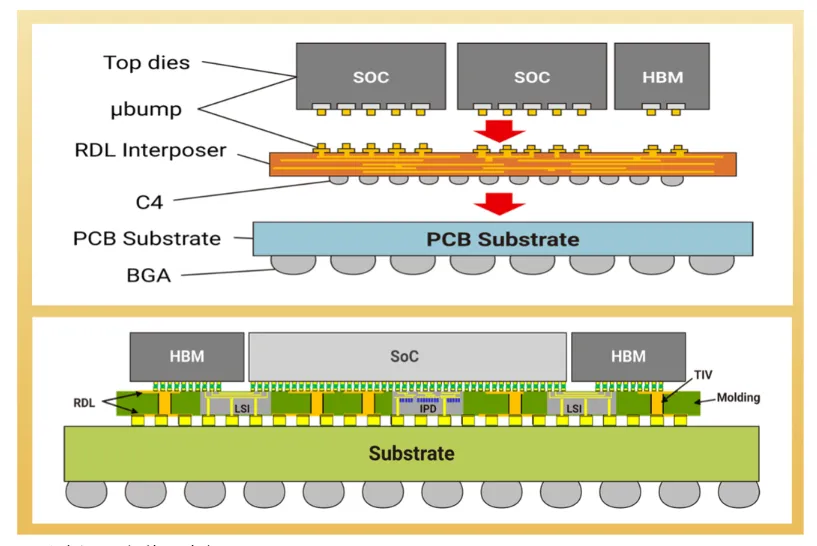

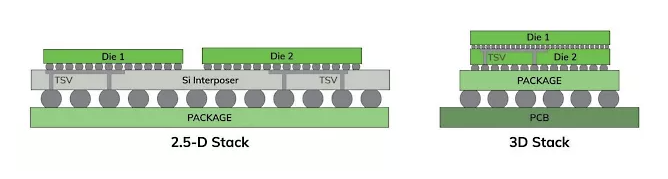

复杂结构封装种类也很繁多,说很复杂也不会,主要是看要了解多深(超废的一句话😆)。概念与前面说明的是差不多的,只是多了把Die跟Die之间的连结,包进来封装一起做。从发展历史来看,主要是由SOC(system on chip)的退而求其次的方式而发展出来,变成早些年也很有话题的SIP(system on package)。也就是要同质晶圆上做出一个系统很难(SOC),干脆降低难度。把系统(不同功能的Die)做在同一个封装里(SIP)。更早些年还有MCM(Multi-Chip Module)封装。然后的发展就是平面做到极限,就往2楼发展,加上使用中介层连接(俗称2.5D IC)。再更进阶就是直接Die叠Die,再往3楼以上发展(俗称3D IC),这些就是近几年很有话题的先进封装CosWoS(Chip-on-Wafer-on-Substrate)、SoIC封装技术如图[11][12]: (我个人认为这些就是SIP发展分支,最后都是做成一个pack 😆)

CosWoS(Chip-on-Wafer-on-Substrate)封装技术[11]

2.5-D 堆叠使用中介层搭配TSV 将多个晶片连接至封装,而3D 堆叠则使用TSV 作为垂直堆叠裸晶的设计。 [12]

事实上先进封装的种类不只CoWoS,还有技术更成熟的Info,没有使用中介层,使用RDL层去扩张Die的出bump面积,让更多的IO pad连接到基板。 [13]以上仅是先进封装技术的概念。因为光是interposer大致依材料内容就可以分成三种架构:Silicon interposer(目前比较成熟的制程)、RDL interposer、Silicon bridge(EMIB),加上Bump种类、TSV等,有兴趣可以参考[14]。

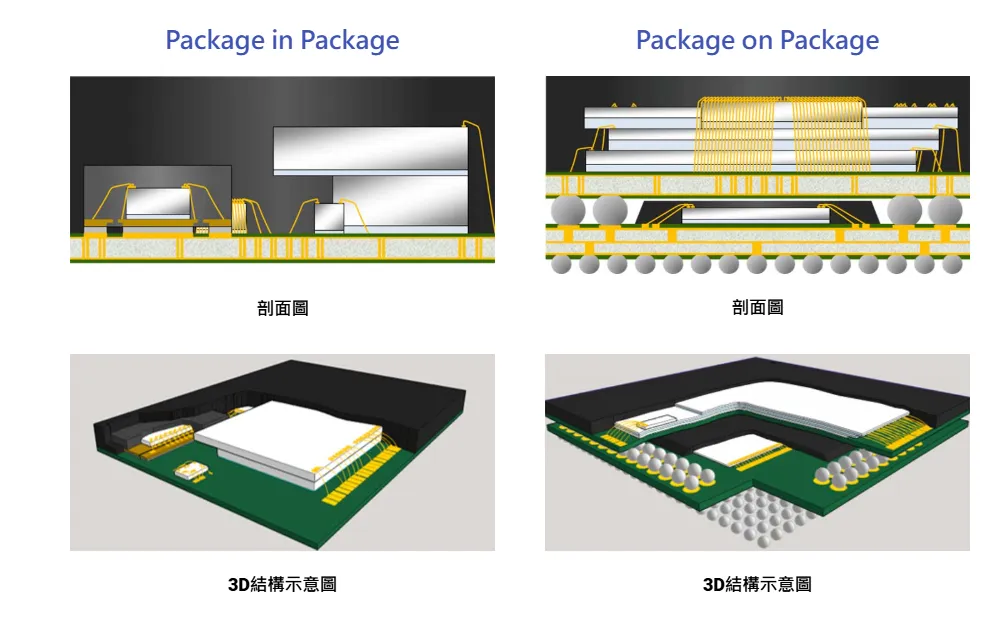

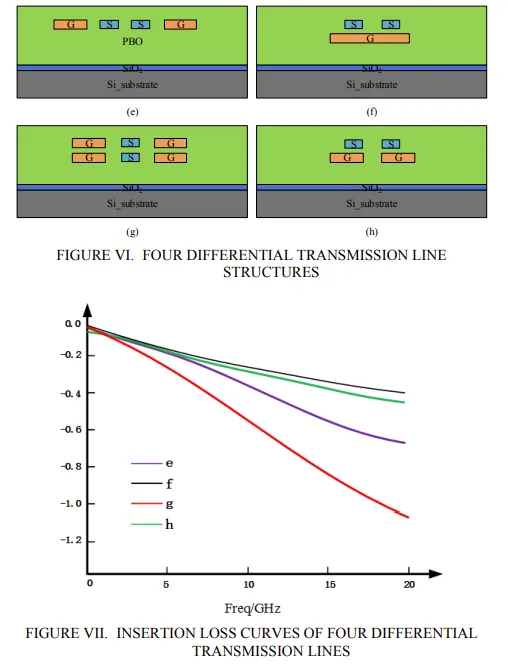

其实早些年也有类似技术像是PIP(Package in Package)、PoP (Package on Package),就是封装包封装与封装叠封装的概念,如下图[15]: (都是SIP)

PIP(Package in Package) and PoP (Package on Package) [15]

讯号完整性在封装的影响

最后谈谈SI的影响,封装要做好一个很重要的因素,就是要有良好的封装通道。封装从一开始的的DIP封装发展到近期的CoWos封装,对于传输高速讯号是友善的。路径缩得越来越短,对于入射与反射的loss都是有相当的帮助。但事实上SI工程师在小尺寸的封装更关注的是反射的loss。但在封装含有TSV、interposer,由高Dk值矽材组成的结构,高频损耗与一般的FR4还是有差的,必须额外考虑其他常见的SI问题(串扰和通道损失),像TSV这种Die to Die的传输,应用在Serdes电路上Skew也是需要考虑的。 (但与传输速率相比结构够短是可以忽略的)

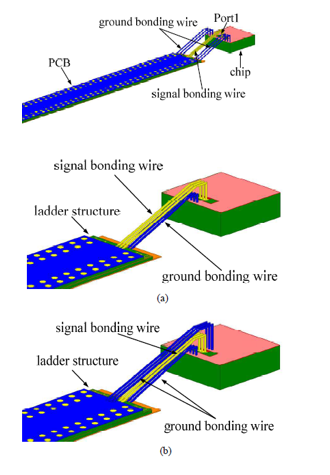

简单看个文献[16]例子,Wire bond连接封装,在高速讯号传输路径上,最害怕遇到磅线结构,对于高频来说,Wire就是一个高电感性元件,会造成高阻抗,影响整体传输频宽。可透过讯号磅线与GND磅线的间距、磅线的尺寸与整体结构,降低感性,来达到阻抗控制的需求。如下图[16] (这种结构封装厂是可以做到,但还要看bond pad在Die上的位置能不能这样出线😆)

Bondwire control by muti layer wire structure [13]

Result [16]

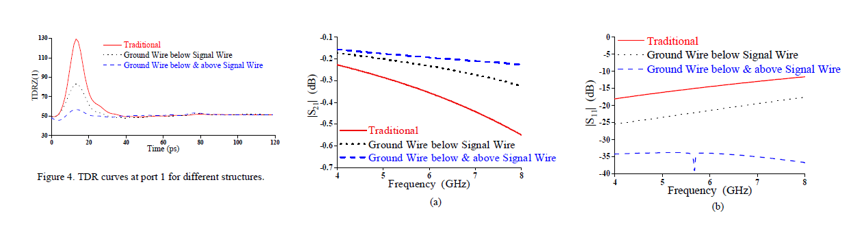

再以Wire bond BGA来说明[17],其实Wire bond BGA封装要做得好,反射就要小。反射点不外乎就是bondwire、Via、Solder Ball Pad。就像感情一样,主要都是肝、肾的问题,肝不好,气色就不会好。肾不好...😆

Three discontinuity regions in a wire-bonded plastic ball grid

array package [17]

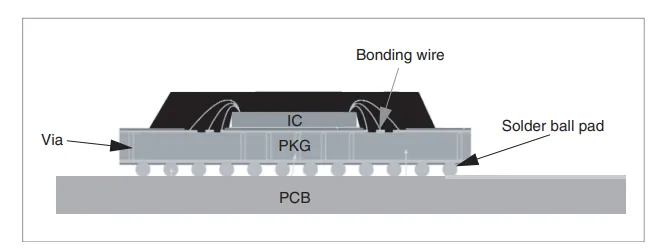

再来是先进封装,比较令人头疼的会是PI问题,尤其电流一大,最直观的IR drop问题就来了,这里先不细谈了。在SI设计上相对容易,主要需要考虑讯号与讯号之间的布线空间是否足够,足以最小化串扰问题。另外就是TSV via 尺寸很小,需考虑集肤效应造成插入损耗是否过大的问题。例外在RDL层,不太可能会有大面积的铺铜,做为参考面当回流路径。只有所谓的GND trace,下图简单的Study不同差分线布线方式对于差损的影响,如下图[18]:

不同差分线布线方式对于差损的影响[18]

写到这里,不禁有种自己在写一篇阳春版的封装技术Review 的感觉。对于SI/PI 工程师来说,封装设计的核心不在于追求最先进的封装制程,而是选择最适合产品需求的技术。说白了,其核心还是成本考量,这也是SI/PI 工程师的基本技能之一Trade-off! 😆

这让我联想到以前看《中华一番! 》时的一集:神前刀工对决,小当家与雷恩的最终对战。比赛的材料是鲷鱼,雷恩拿出了一把令人惊叹的猛刀— —北辰天狼刃(功能是切出的鱼肉特别保鲜😆)。而小当家则仅有一把由母亲传承下来的百穴菜刀。最后小当家赢了比赛。获胜的关键在于,他在百穴菜刀上巧妙地缠绕了细钢丝,让刀在切割鲷鱼时,达到与北辰天狼刃相同的保鲜效果。

老板表示🧓:「百穴菜刀?不觉得钢丝很像磅线吗?新产品用QFN 应该就能Work了吧!」

中华一番剧情

Double bonds with multi-wirebonds [20]

参考文献

[1] IC封装与测试,葱宝说说,半導體製程(三) | 封裝與測試 | 蔥寶說說裸晶們怎麼穿衣服

[2] 一文看懂封装基板,http://www.semiinsights.com/s/electronic_components/23/43704.shtml

[3] IC封装类型列表,https://zh.wikipedia.org/zh-tw/IC%E5%B0%81%E8%A3%85%E7%B1%BB%E5%9E%8B%E5%88%97%E8%A1%A8

[4] What is the Wire Bond Process? , What is the Wire Bond Process

[5] Gopal Bhatt , Optimization of Ultrasonic and Thermosonic Wire-Bonding Parameters on Au/Ni Plated PCB Substrate

[6] Jing Rou Lee , A review on numerical approach of reflow soldering process for copper pillar technology

[7] ASE Leadframe Packaging Offerings, 導線架封裝 | ASE

[8] https://www.iem.yzu.edu.tw/chinese/..%5CFiles%5CSpeech%5C20090512.pdf

[9] AN-772: A Design and Manufacturing Guide for the Lead Frame Chip Scale Package (LFCSP), AN-772: A Design and Manufacturing Guide for the Lead Frame Chip Scale Package (LFCSP) | Analog Devices

[10] BGA: Features, Soldering, and X-Ray Inspection | Sierra Circuits

[11] AIGC 带动CoWoS 先进封装需求https://wangofnextdoor.blogspot.com/2023/07/aigc-cowos.html

[12] 什么是先进半导体封装? , https://www.ansys.com/zh-tw/simulation-topics/what-is-advanced-semiconductor-packaging

[13] 如何区分Info与CoWoS封装? , https://www.eet-china.com/mp/a229437.html

[14] 一文读懂先进封装的四大要素? TSV、Bump、RDL、wafer,一文读懂先进封装的四大要素?TSV、Bump、RDL、wafer - 艾邦半导体网

[15] 首頁 - 華泰電子股份有限公司

[16] Jun-Jian Ju, Multi -Layered Wire Bonding Structure for

Impedance Matching

[17] Dong Gun Kam and Joungho Kim, Packaging a 40-Gbps Serial Link Using a Wire-Bonded Plastic Ball Grid Array

[18] Wenchao Tian and Zhanghan Zhao, Electrical Performance Simulation of 2.5D Package

[19] Arun Chandrasekhar, Characterisation, Modelling and Design of Bond-Wire Interconnects for Chip-Package Co-Design