systemverilog中clocking的用法

文章目录

- 1.clocking简介

- 2.clocking实例分析

- 3.重点分析

- (1)bus定义是不是随便取名的

- (2)输入输出的定义原则是什么

- (3)到底如何消除了竞争和冒险

- (4)没用到的信号如何处理

- (5)clocking和modport有什么关系

- (6)真实的clocking同步体会

1.clocking简介

概念:接口中声明clocking(时序块)和采样的时钟信号,用来做信号的同步和采样。clcoking块基于时钟周期对信号进行驱动或采样的方式,使得待测平台不再苦恼于如何准确及时地对信号驱动或采样,消除了信号的竞争问题。

作用:

- 事件的同步

- 输入的采样

- 输出的驱动

2.clocking实例分析

clocking bus @(posedge clock1);//定义了clocking为bus,由clock1的上升沿来驱动采样。default input 10ns output 2ns;//clocking所有信号默认为前10ns对其进行输入采样,在事件的后2ns对其进行输出驱动input data,reday,enable = top.mem1.enable//定义了输入信号output negedge ack;//定义了驱动信号,驱动信号的事件是时钟clock1的下降沿input #1step addr;//addr采用自身定义的采样时间,即clock1上升沿的1setp

endclocking

注意点:

- clocking块不但可以定义在interface中,也可以定义在module和program中

- clocking中列举的信号不是自己定义的,而是interface或其他声明clocking的模块定义的

- clocking在声明完名字之后,应该伴随定义默认时间。如果没定义,默认在clocking采样事件前的1setp对输入进行采样,在采样事件后的#0对输出进行驱动。

- 除了定义默认的采样和驱动事件,也可以在定义信号方向时,用新的采样事件对默认采样事件进行覆盖。

3.重点分析

(1)bus定义是不是随便取名的

bus不是随意进行的取名,而是对于driver和monitor中信号赋值的时候需要用上的,比如:

my_if vif;

my_transaction tr;

...vif.bus.ack<= tr.ack;

...

(2)输入输出的定义原则是什么

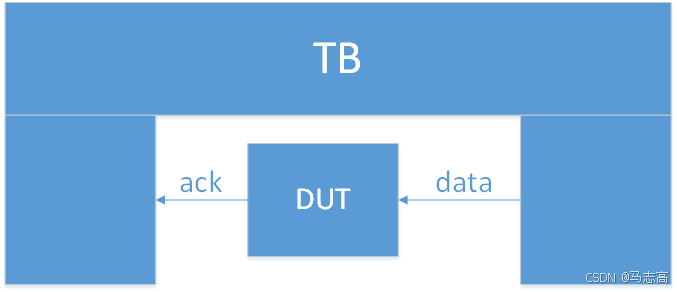

当信号从testbench到DUT是为输入,这里的data是输入

当信号从DUT到testbench是为输出,这里的ack为输出

(3)到底如何消除了竞争和冒险

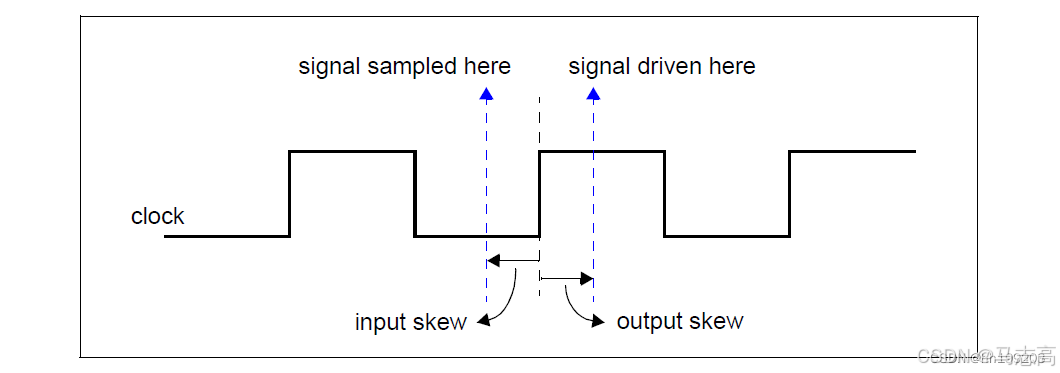

在RTL仿真时,由于无法确定具体电路的延迟时间,默认情况下时钟驱动电路时会添加一个无限最小的时间(delta cycle)的延迟,这个延迟要比最小时间单位精度还要小(可以理解成远小于1ps)。由于各种可能性,clk与被采样数据之间如果只存在若干个delta-cycle的延迟,那么采样就会出问题,在同样的时刻可能会得到不同的采样结果。

为了避免在RTL仿真中发生信号竞争的问题,使用时钟块来决定信号的驱动和采样的方式。

从这张图可以得知,input skew为 10step,输入信号的采样,会在时钟时间(clock1上升沿)前的10ns采样,output skew 为2,输出会在clocking事件后2ns时刻输出驱动。这样使得对clocking块中声明的信号进行采样和驱动时,不会造成竞争情况。

(4)没用到的信号如何处理

clocking是可以不使用全interface里面的信号的,如:

interface my_if(input clock1,input rst_n);logic [7:0]data;

logic ready;

logic enable;

logic addr;

logic ack;

logic psel;clocking bus @(posedge clock1);default input 10ns output 2ns;input data,reday,enable = top.mem1.enableoutput negedge ack;input #1step addr;

endclockingendinterface

很明显psel在clocking中未使用。

(5)clocking和modport有什么关系

interface A_Bus( input bit clk );wire req, gnt;wire [7:0] addr, data;clocking sb @(posedge clk);input gnt;output req, addr;inout data;endclockingmodport STB ( clocking sb ); // synchronous testbench modport

endinterface

modport介于interface和clocking之间,主要用于对信号进行分组,指定信号的输入输出方向,而clocking则是作用于信号的更底层,主要用于信号时序相关的控制,例如采样、同步等,当然clocking也可以指定信号的输入输出方向。(这么来看,modport好像没啥作用,modport能做的,clocking都能做。)

(6)真实的clocking同步体会

[DV]在长burst中漏采样的问题_什么叫漏采样-CSDN博客