Vivado时序报告六:Report Timing详解

目录

一、前言

二、配置选项概览图

三、配置选项详解

3.1 Targets

3.2 Options

3.1.1 Report

3.1.2 Path limits

3.1.3 Path display

3.2 Advanced

3.2.1 Report

3.2.2 File Output

3.2.3 miscellaneous

3.3 Timer Settings

3.4 共有部分

四、 设计示例

4.1 设计工程

4.2 Report Timing报告

4.2.1 General information

4.2.2 Settings

4.2.3 Timing checks

一、前言

时序分析中,Report_timing_summary默认是对所有路径进行分析,当工程设计较大时,时序路径较多,想要查找指定时序路径的时序情况就不方便,此时就可以使用“Report Timing"功能,但“ReportTiming”不会报告“Pulse Width” (脉冲宽度)。

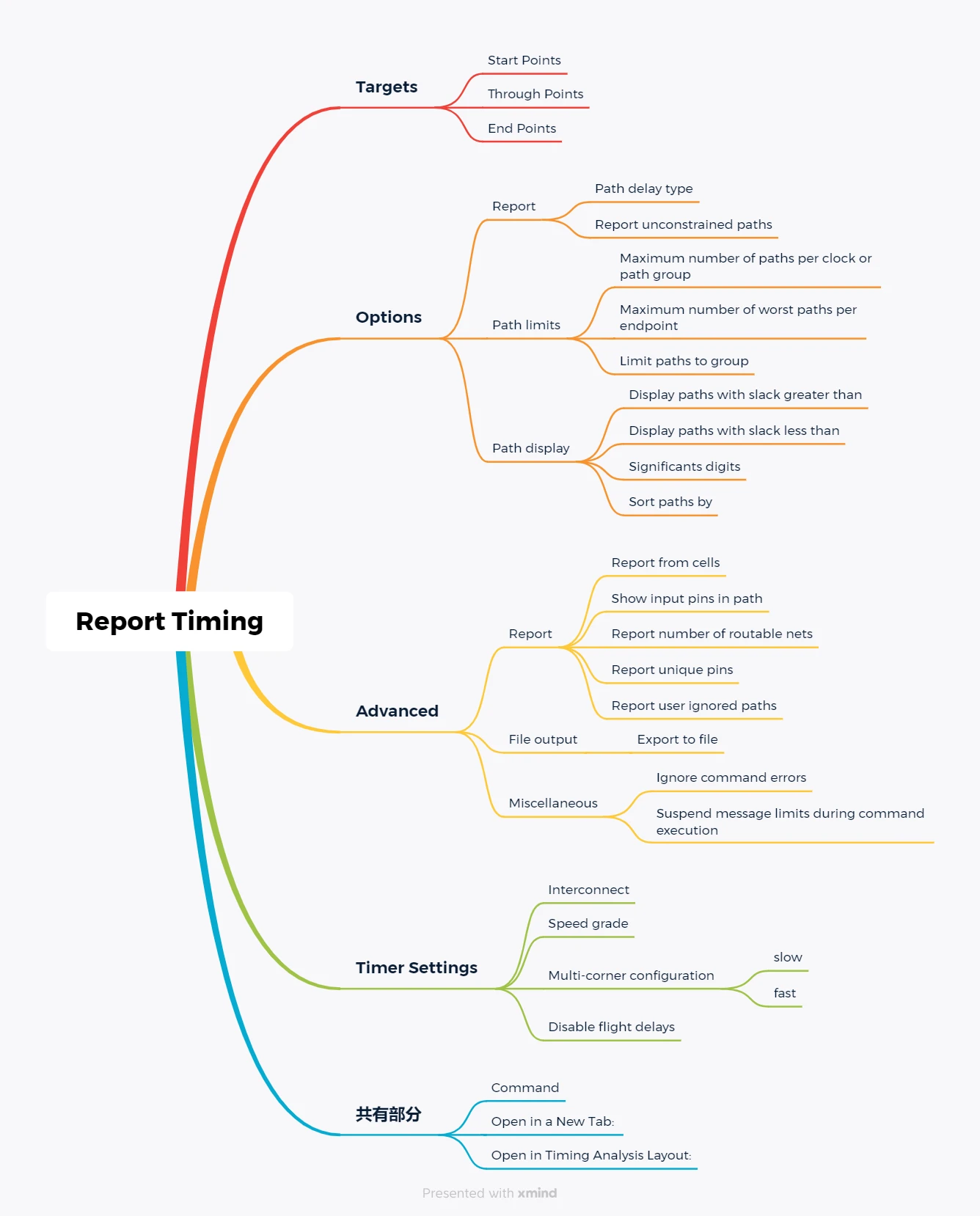

二、配置选项概览图

下图是Report Timing 中所有配置选项的结构图。

三、配置选项详解

下面,将对配置选项逐项进行解释。

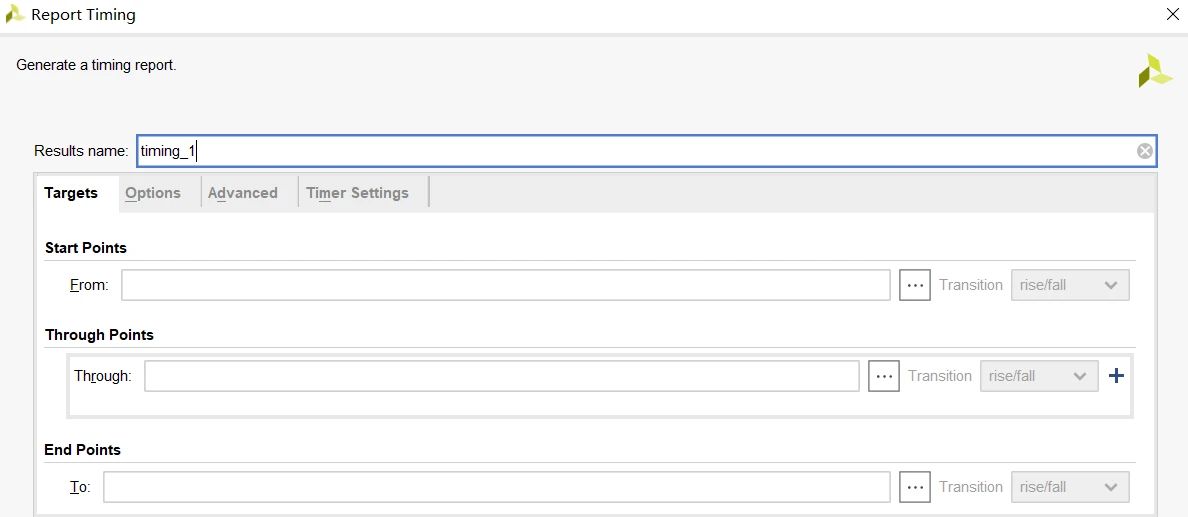

3.1 Targets

最上面的Result name是设置名称,默认是“timing_x”,如果会多次运行分析,x将从1开始计数的

Start points (From):设置时序路径的起点,可为网表Cells,时钟Clocks,引脚Cells pin和端口Ports,可同时设置多个,设置多个时符合其中任意一个都会进行分析,都符合则都进行分析

Transtion(Rise/Fall):用于设置源时钟边沿(上升沿/下降沿)。

Through Points (Through) : 设置路径的中间经过单元,可为网表Cells,线Nets,引脚Cells pin。可同时设置多个,设置多个时会对分析所有的对象。

Endpoints (To): 设置时序路径的终点,可为网表Cells,时钟Clocks,引脚Cells pin和端口Ports,可同时设置多个,设置多个时符合其中任意一个都会进行分析,都符合则都进行分析

时钟。

3.2 Options

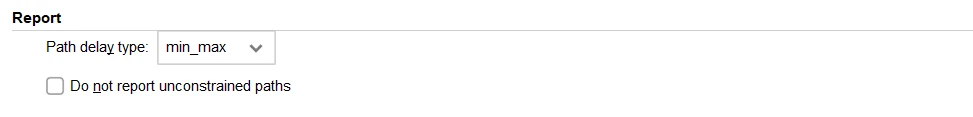

3.1.1 Report

Path delay type: 设置运行分析的类型,可设为min,max,min_max,综合阶段和实现阶段默认max和min都会分析,如果选择min,则只进行hold和removal分析

Report unconstrained paths:该选项默认勾选,对无约束的路径进行报告,当使用tcl命令report_timing_summary时是不会打开该配置

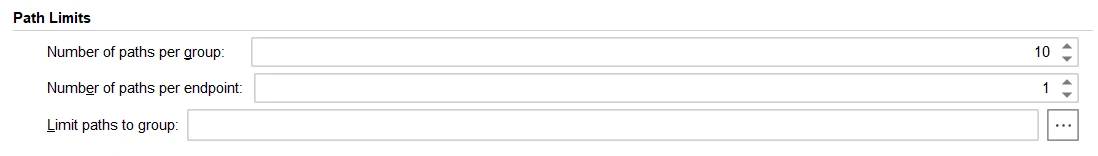

3.1.2 Path limits

Number of paths per clock:控制每个时钟组或路径组的最大数目,等效的tcl命令为-max_paths

Number of per endpoint:控制每个路径终点的最大路径数,该值一定是小于或等于maximum number of paths per clock or path group的值,等效的tcl命令为-nworst

Limits paths to group:设置每个时钟组的路径数,每个时钟属于一个时钟组

3.1.3 Path display

Display paths with slack greater than: 通过路径的slack值进行过滤,设置所能显示的slack值的最小值

Display paths with slack less than:通过路径的slack值进行过滤,设置所能显示的slack值的最大值

Significant digits:控制报告中数字显示的精度,默认是3位小数

Sort paths by:设置按组(默认) 还是按裕量slack来显示报告的路径。如果按组排序, 报告中会包含每个组和每种分析类型 (-delay_type min/max/min_max) 的 N 条(Number of per endpoint的设置值)最差的路径,最差的违例的组排在最前面。如果按裕量排序, 将按分析类型报告 N 条最差的路径(所有组已组合在一起), 并按裕量值升序排序。等效的 Tcl 选项为-sort_by。

3.2 Advanced

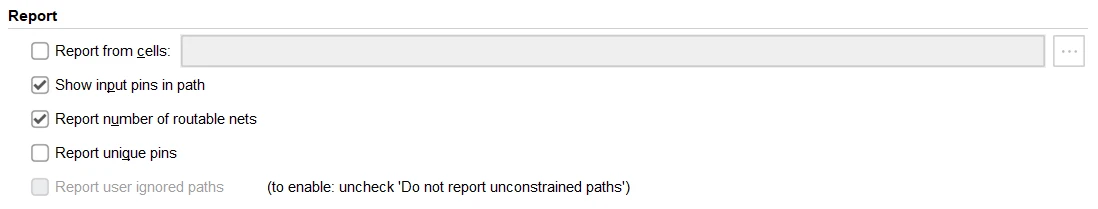

3.2.1 Report

Report from cells:指定报告的时序路径都经过设置的cells,该cells可以是起点,终点或中间部分

Show input pins in path:勾选后会显示时序路径上每个单元的输入引脚

Report number of routable nets:勾选后只报告布线成功net的

Report unique pins:勾选后,对于每一组引脚(起点和终点)仅展示一条时序路径

Report user ignored paths:勾选后将不会报告Unconstrained paths内容

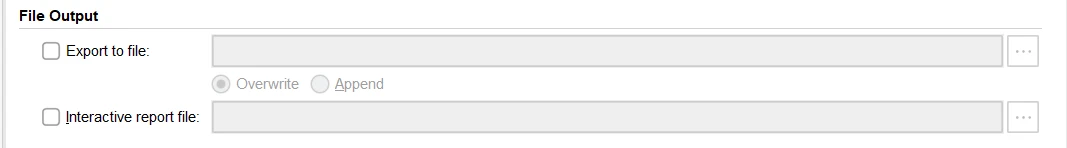

3.2.2 File Output

Export to file:默认的时序报告结果是写入时序窗口中,可以指定导出到指定的文件,写入时可以指定时覆盖overwrite或追加append写入

Interactive report file:以赛灵思RPX格式写入指定名称的文件中,RPX文件是一个包含所有报告信息的交互式报告,可以被重载入内存中

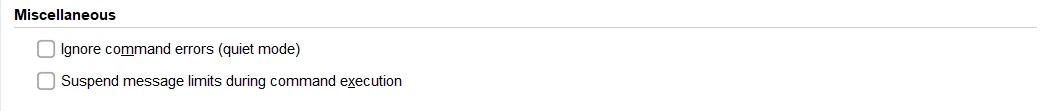

3.2.3 miscellaneous

Ignore command errors:直接执行命令,会忽略命令中的错误也不会返回错误信息,等效的tcl命令为-quiet

Suspend message limits during command execution:暂时性的忽略任何信息显示限制的设置,返回所有信息,等效的tcl命令为-verbose

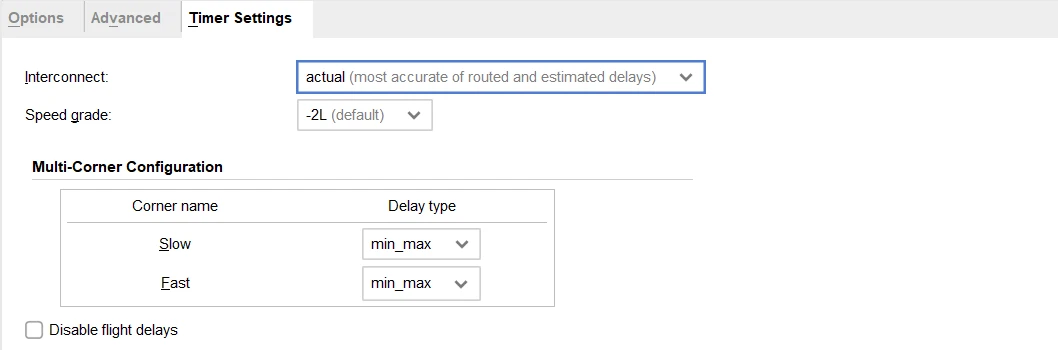

3.3 Timer Settings

Interconnect:用于控制net的时延值的计算方式,可以是评估的cell间的布线距离,实际的布线或者时序分析时移除net的时延。默认情况下,综合后阶段是用估算的net延时值,实现阶段后是用实际的net时延。可以设置值:actual,estimated,none

Estimated:对于未布局的单元cells,走线时延值是用最可能的布局情况下的值,会考虑driver和load以及扇出;对于已经布局的cells,走线时延是基于driver和load的距离以及扇出

actual:对于已经布线的net,走线时延是和实际硬件走线的时延一致

none:不考虑走线时延,等效走线时延值为0

Speed grade:设置器件的速度等级,通常情况下该值和工程创建时设置的速度一致,也可以不需要重新运行综合和实现,直接改变速度等级进行时序分析,等效的tcl命令为 set_speed_grade

Multi-corner configuration:指定fast/slow corner(可以理解为芯片运行的外部环境的好坏)下分析的路径时延类型,可以为none,min,max,min_max

Disable flight delays:勾选后时序分析不会考虑I/O端口的封装时延,

3.4 共有部分

Command:根据当前配置选项的情况自动生成对应的tcl命令

Open in a New Tab:勾选后在一个新的tab中显示结果,原先的tab标签结果保留,不勾选则会覆盖原有的结果

Open in Timing Analysis Layout:勾选后时序分析中以“Timing Analysis”的布局方式呈现结果

四、 设计示例

4.1 设计工程

module report_timing(d1,I1,I2,I3,clk1,clk2,clk3,ce,out1,out2);

input d1,I1,I2,I3,clk1,clk2,clk3,ce;

output out1,out2;

reg ff0,out1,out2;

wire result;

always@(posedge clk1,negedge ce)

begin

if(!ce)

ff0<=0;

else begin

ff0<=d1;end

end

assign result=ff0&ff0;LUT4 #(.INIT(16'h0810) // Specify LUT Contents) LUT4_inst (.O(o_lut), // LUT general output.I0(result), // LUT input.I1(I1), // LUT input.I2(I2), // LUT input.I3(I3) // LUT input);

always@(posedge clk2,negedge ce)

begin

if(!ce)

out1<=0;

else

out1<=o_lut;

endalways@(posedge clk3)

begin

if(!ce)

out2<=0;

else

out2<=o_lut;

end

endmodule时序约束

create_clock -period 10.000 -name clk1 -waveform {1.000 6.000} [get_ports clk1]

create_clock -period 8.000 -name clk2 -waveform {0.000 4.000} [get_ports clk2]

create_clock -period 8.000 -name clk3 -waveform {0.000 4.000} [get_ports clk3]4.2 Report Timing报告

Exception报告包含四个部分:General information,Settings,Timing Checks;

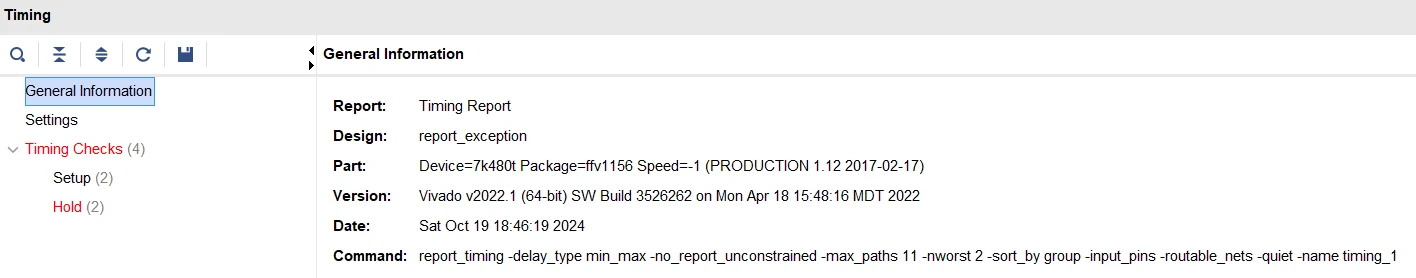

4.2.1 General information

与其他时序报告类似,General information主要包含一些基本信息,报告类型,设计模块名称,器件信息,Vivado版本,报告生成时间,报告生成对应的tcl命令

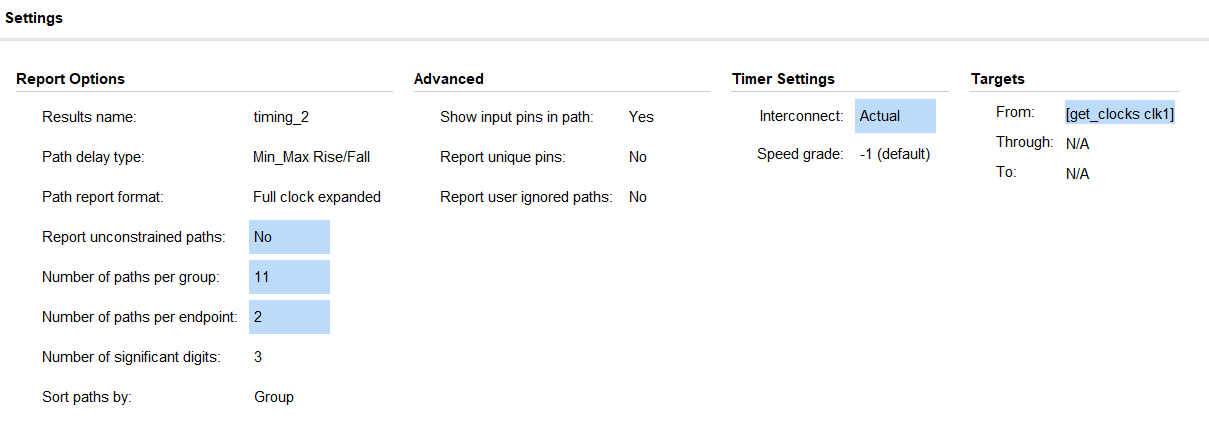

4.2.2 Settings

Settings中显示了生成报告前的配置选项界面的设置,也是分Targets,Report Options,Advanced,Timer Settings四类来展示

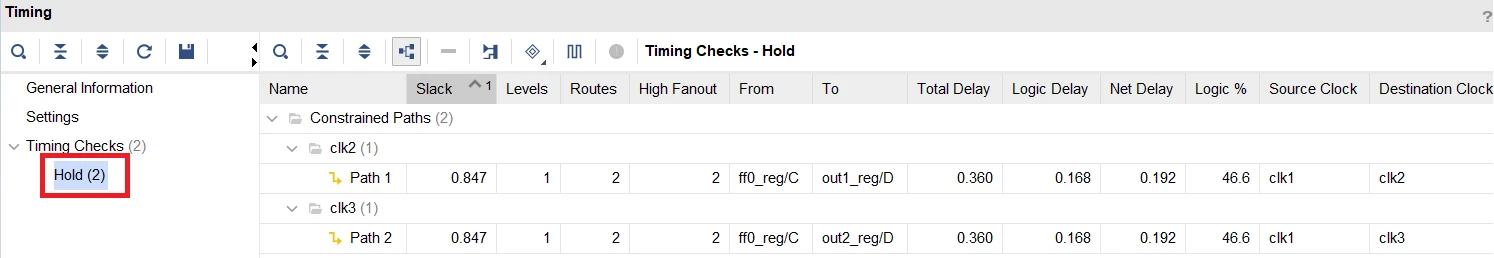

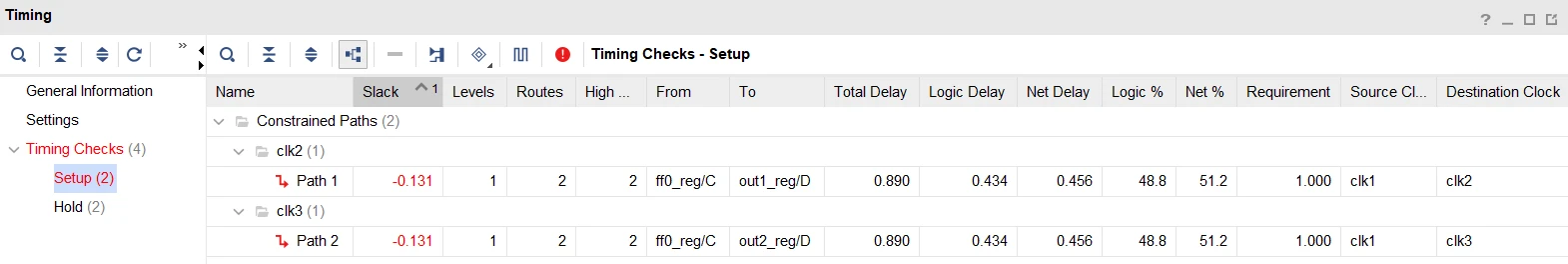

4.2.3 Timing checks

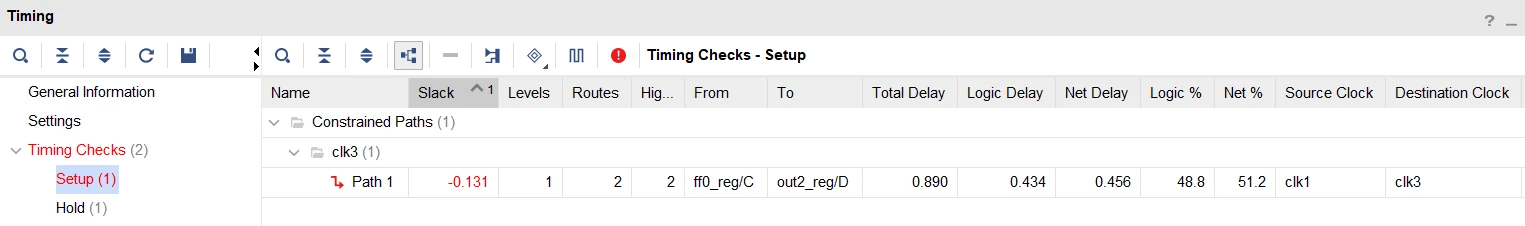

在使用默认配置时,结果和report_timing_summary的报告结果一致,除了无pulse_width的内容,下图是上述设计默认配置下的报告

将End points设为clk3,报告只有destination clock为clk3的路径

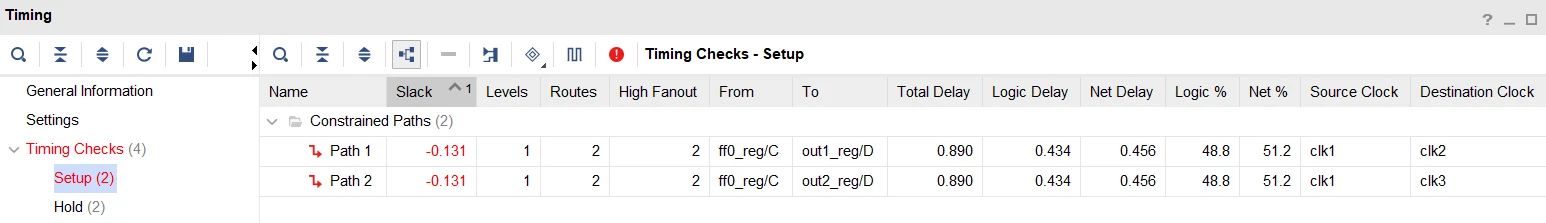

将sort paths by设为slack,则报告结果按slack来展示

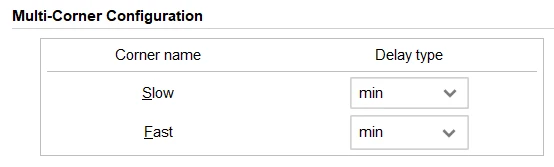

将slow/fast corner下的延时类型都设为min

则报告只有hold分析