VHDL-2008语言支持

介绍

AMD Vivado™合成支持VHDL-2008标准的可合成子集。这个以下部分介绍了支持的子集以及使用它的过程。将Vivado设置为使用VHDL-2008有几种方法可以使用Vivado运行VHDL-2008文件。您可以转到源文件属性窗口,并从可用文件类型的下拉列表中设置类型:VHDL 2008。这个Vivado工具将文件类型设置为VHDL-2008。也可以使用Tcl控制台中的set_property命令将文件设置为VHDL-2008。这个语法如下:

set_property FILE_TYPE {VHDL 2008} [get_files <file>.vhd]

最后,在非项目或Tcl流中,用于在VHDL中读取的命令的VHDL-2008为跟随:

read_vhdl -vhdl2008 <file>.vhd

如果要读入多个文件,可以使用多个read_vhdl命令或使用一个命令创建多个文件,如下所示:

read_vhdl -vhdl2008 {a.vhd b.vhd c.vhd}

支持的VHDL-2008功能

Vivado支持以下VHDL-2008功能。

操作员

匹配关系运算符

VHDL-2008现在提供了返回位或std_logic类型的关系运算符。在上一个VHDL标准,关系运算符(=,<,>=…)返回布尔类型。对于新的类型,需要写成的代码:

if x = y then

out1 <= '1';

else

out1 <= '0';

end if;

Can now be written as:

out1 <= x ?= y;

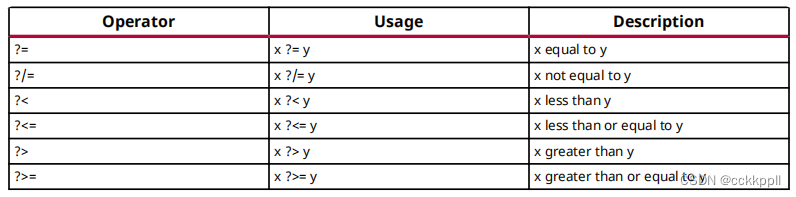

下表列出了Vivado中支持的关系运算符。

最大和最小运算符

VHDL-2008中新的最大和最小运算符采用两个不同的值和分别返回较大或较小的。例如

out1 <= maximum(const1, const2);

移位运算符(rol、ror、sll、srl、sla和sra)

sla和sra运算符以前只定义了位和布尔元素。现在VHDL-2008标准在有符号库和无符号库中定义了它们。

一元逻辑归约算子

在VHDL的早期版本中,和、nand或等运算符取两个不同的值和返回了一个位或布尔值。对于VHDL-2008,添加了对这些的一元支持操作员。它们返回输入的逻辑函数。例如,代码:

out1 <= and("0101");

将这4个比特加在一起并返回0。具有一元支持的逻辑函数是:and,nand、or、nor、xor和xnor。

混合数组和标量逻辑运算符

以前在VHDL中,逻辑运算符的两个操作数需要具有相同的大小。

VHDL-2008支持在其中一个操作数是数组而另一个是时使用逻辑运算符标量。例如,要将一个比特与向量的所有比特进行“与”运算,需要以下代码:

out1(3) <= in1(3) and in2;

out1(2) <= in1(2) and in2;

out1(1) <= in1(1) and in2;

out1(0) <= in1(0) and in2;

This can now be replaced with the following:

out1<= in1 and in2;

声明

如果其他-如果和案例生成

以前在VHDL中,if generate语句采用以下形式:

if condition generate

--- statements

end generate;

An issue appears if you want to have different conditions; you would need to write multiple

generates and be very careful with the ordering of the generates. VHDL-2008 supports if

else-if generate statements.

if condition generate

---statements

elsif condition2 generate

---statements

else generate

---statements

end generate;

In addition, VHDL-2008 also offers case-generate statements:

case expressions generate

when condition =>

statements

when condition2 =>

statements

end generate;

Sequential Assignments

VHDL-2008 allows sequential signal and variable assignment with conditional signals. For

example, a register with an enable would be written as the following:

process(clk) begin

if clk'event and clk='1' then

if enable then

my_reg <= my_input;

end if;

end if;

end process;

With VHDL-2008, this can now be written as the following:

process(clk) begin

if clk'event and clk='1' then

my_reg <= my_input when enable else my_reg;

end if;

end process;

Using case? Statements

With VHDL-2008, the case statement has a way to deal with explicit don’t care assignments.

When using case? , the tool now evaluates explicit don’t care terms, as in the following

example:

process(clk) begin

if clk'event and clk='1' then

case? my_reg is

when "01--" => out1 <= in1;

when "000-" => out1 <= in2;

when "1111" => out1 <= in3;

when others => out1 <= in4;

end case?;

end if;

end process;

Using select? Statements

Like the case, the select statement now has a way to deal with explicit don’t care

assignments. When using the select? statement, the tool now evaluates explicit don’t care

terms, for example:

process(clk) begin

if clk'event and clk='1' then

with my_reg select?

out1 <= in1 when "11--",

in2 when "000-",

in3 when "1111",

in4 when others;

end if;

end process;