【Verilog】——Verilog简介

目录

1.简介

2.什么是HDL以及HDL的功能

3.Verilog和C语言的比较

4.Verilog的用途

5.数字系统的抽象层次

1.系统级

2.算法级

3.RTL级(寄存器变换级)

6.数字系统抽象层级

7.自顶向下的结构化设计方法

8.Verilog建模

9.Verilog概述

10.Verilog模块的基本概念

11.Verilog模块总结

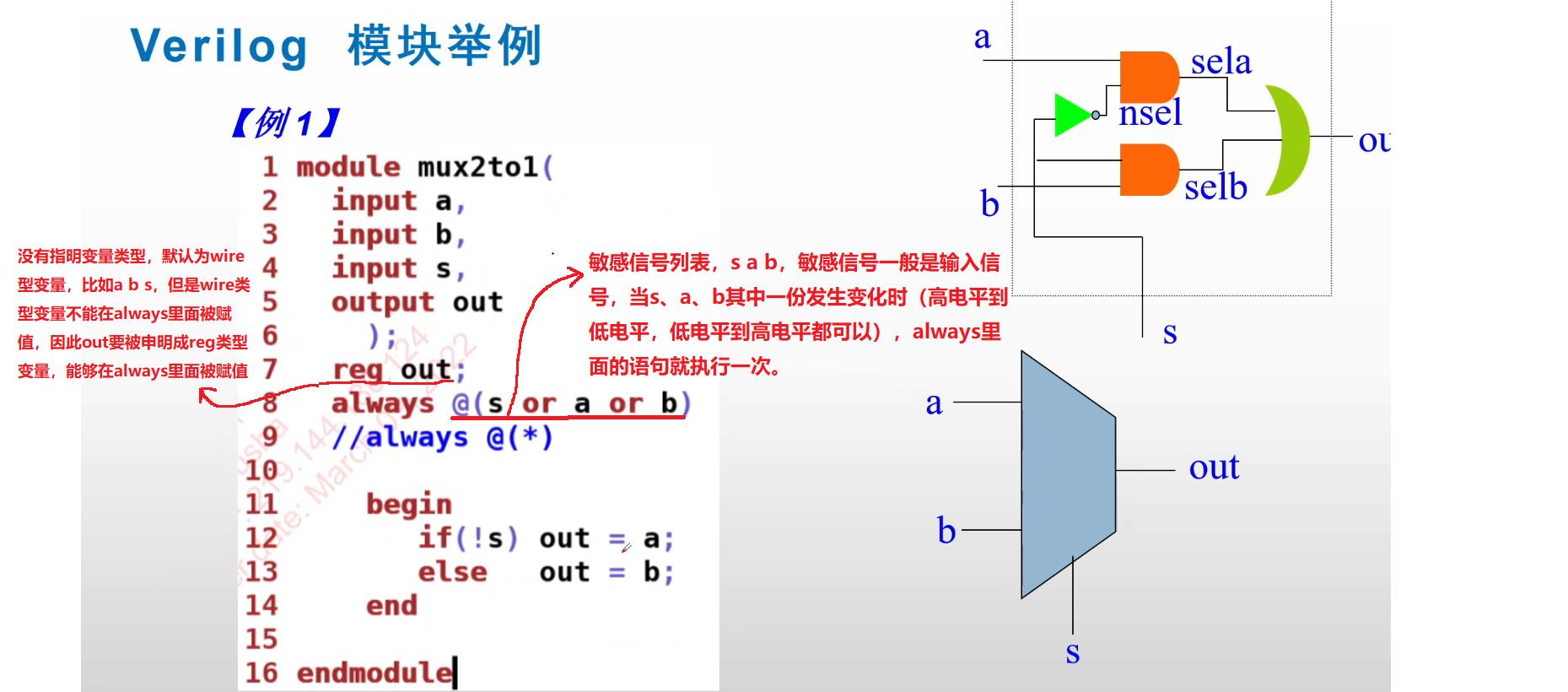

12.二选一数据选择器

13.测试模块

1.简介

本课程是一门关于现代数字系统设计基础的课程,讲述硬件描述语言Verilog HDL的要素、语法、语句,仿真测试程序及可综合的设计方法。

通过本课程的学习,掌握利用Verilog设计现代数字系统的基本方法和手段(基本语法,简单的可综合verilog模块(与逻辑电路的对应),简单的verilog测试模块)。

rtl——可综合的模块,对应逻辑电路

tb——测试代码,用来测试电路的

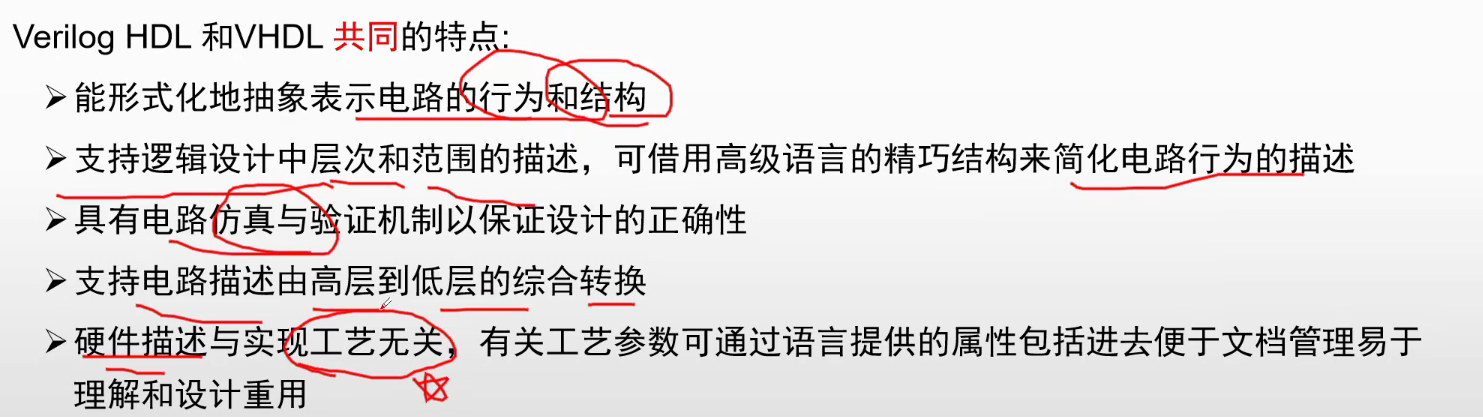

2.什么是HDL以及HDL的功能

3.Verilog和C语言的比较

4.Verilog的用途

5.数字系统的抽象层次

1.系统级

2.算法级

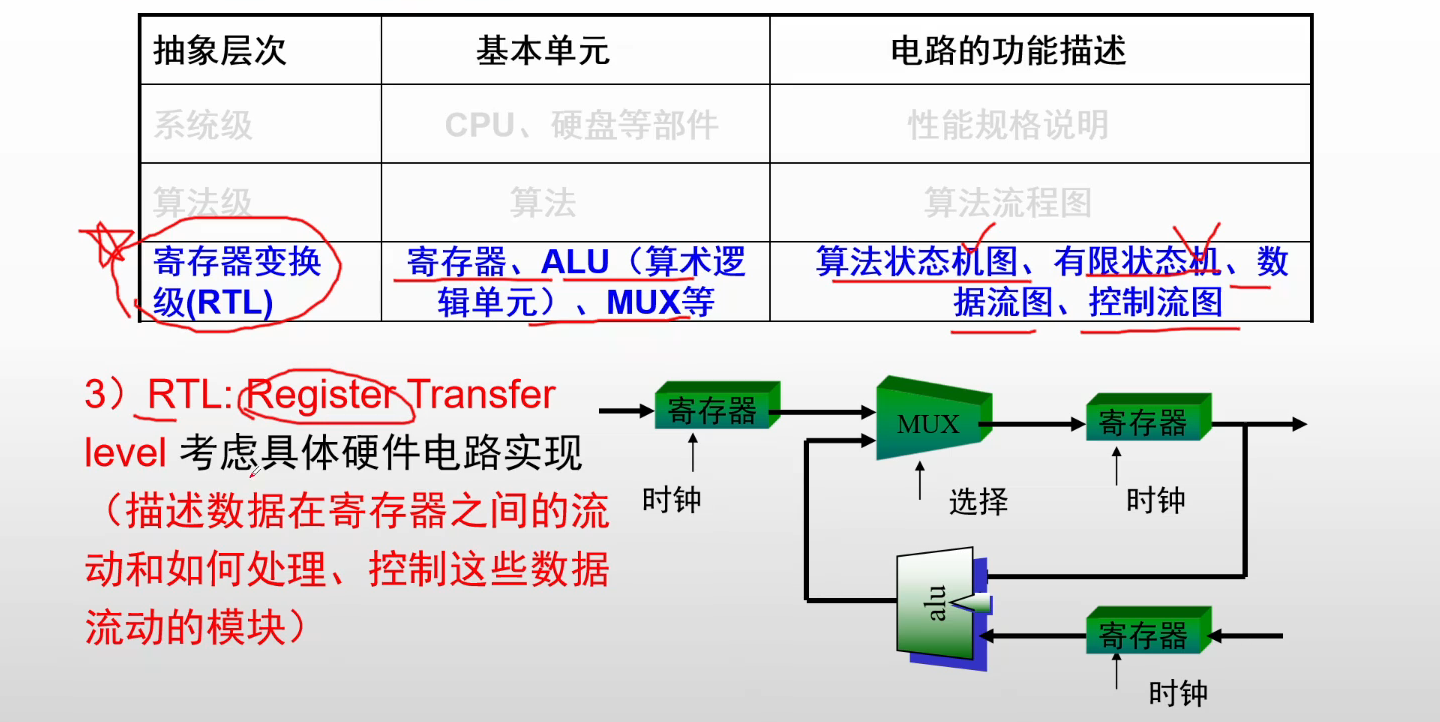

3.RTL级(寄存器变换级)

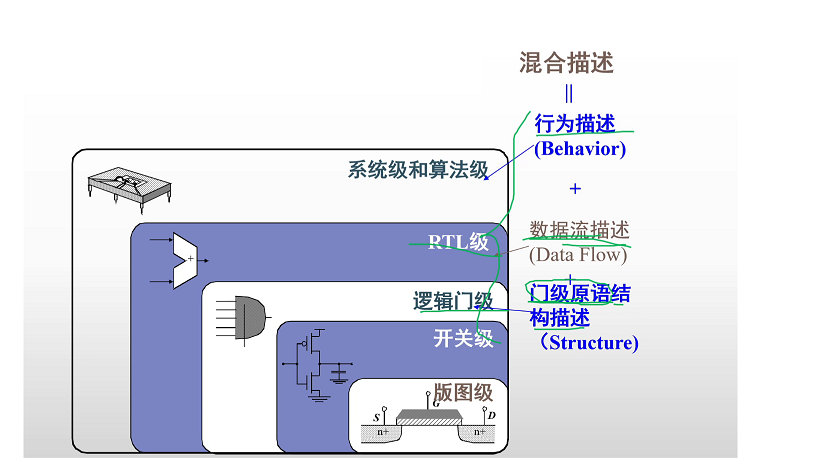

6.数字系统抽象层级

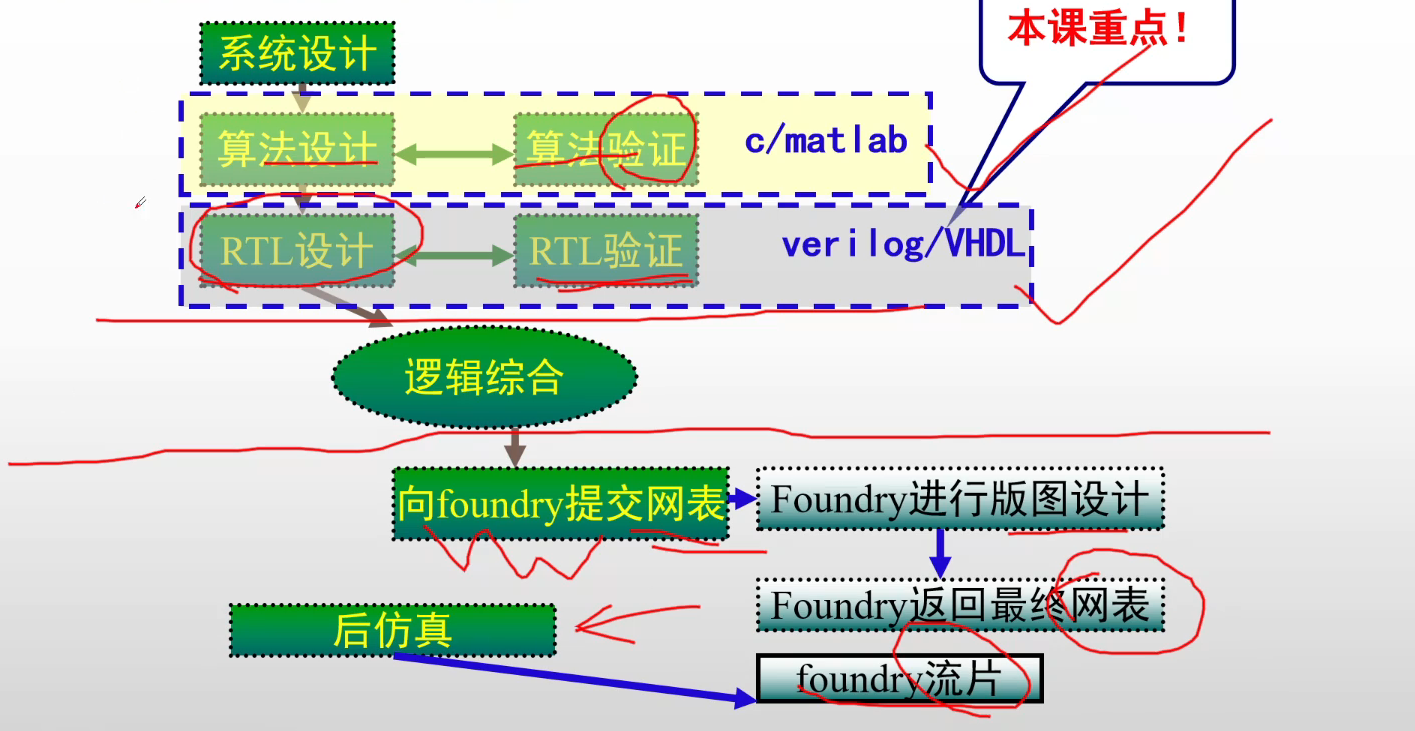

7.自顶向下的结构化设计方法

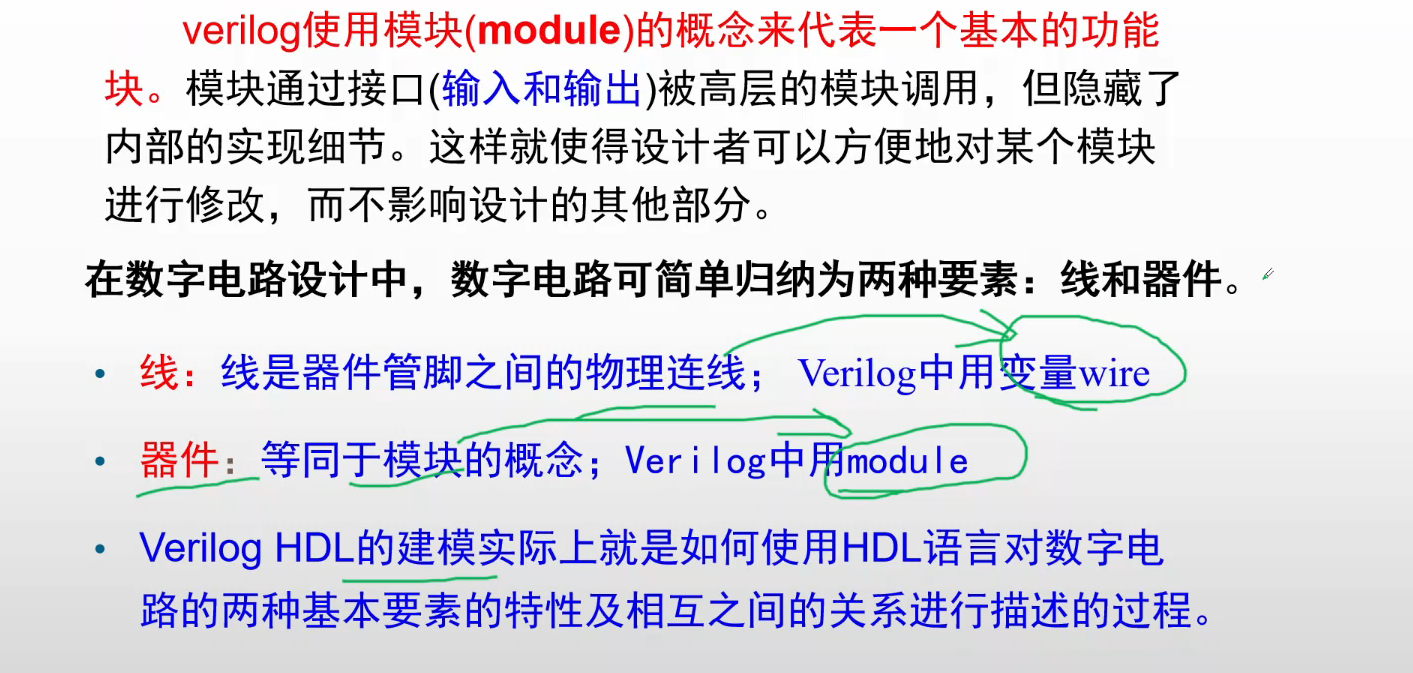

8.Verilog建模

9.Verilog概述

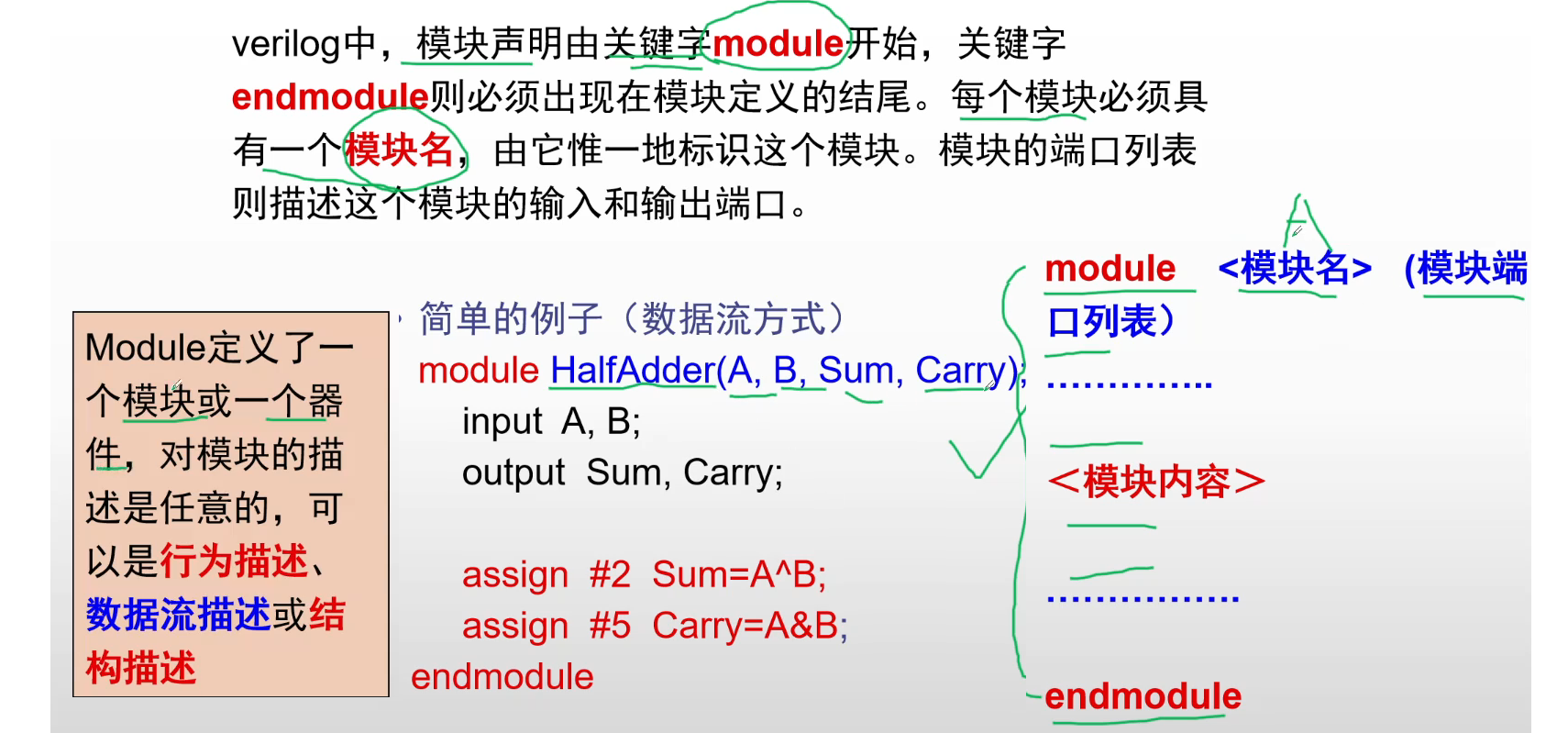

10.Verilog模块的基本概念

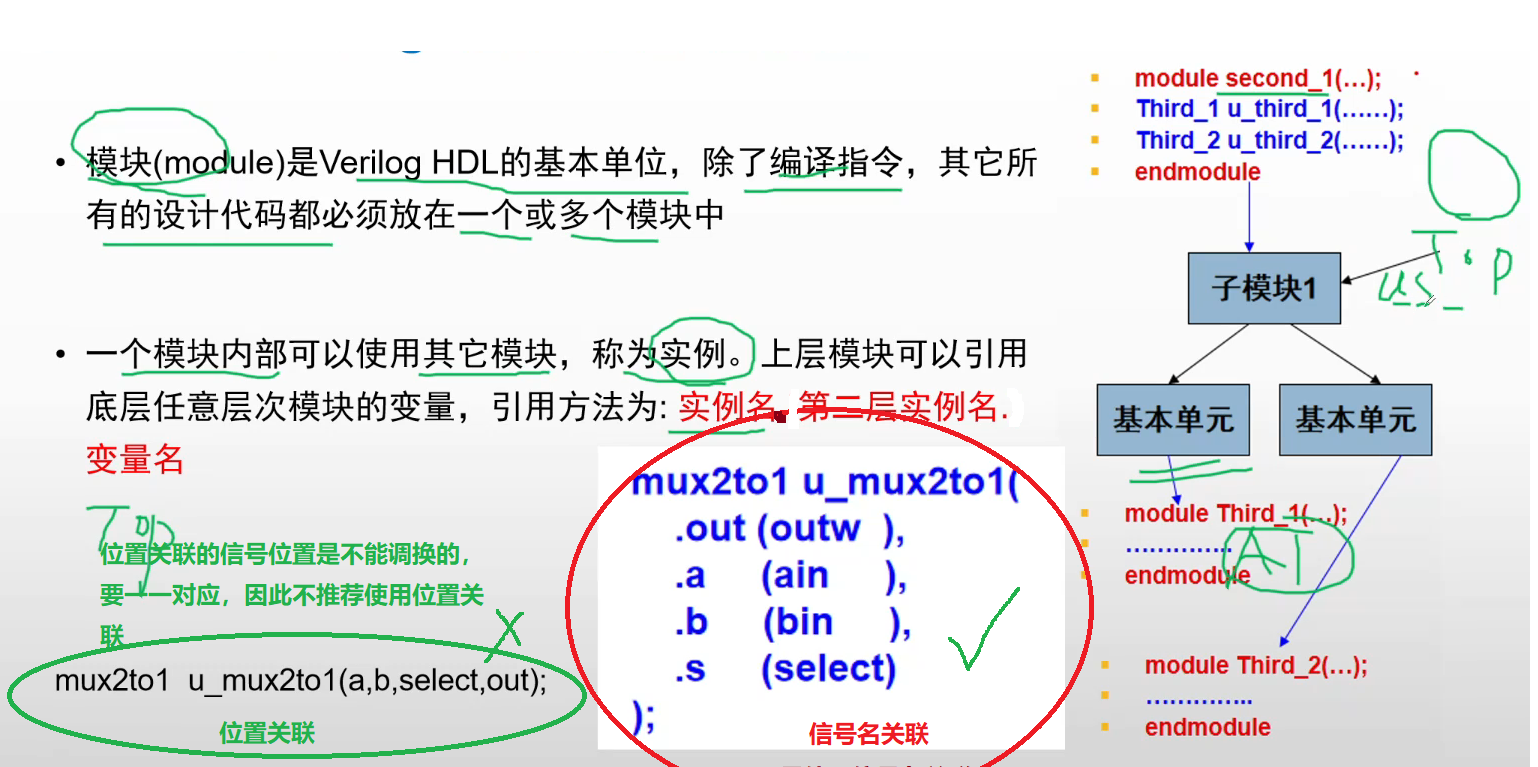

11.Verilog模块总结

12.二选一数据选择器

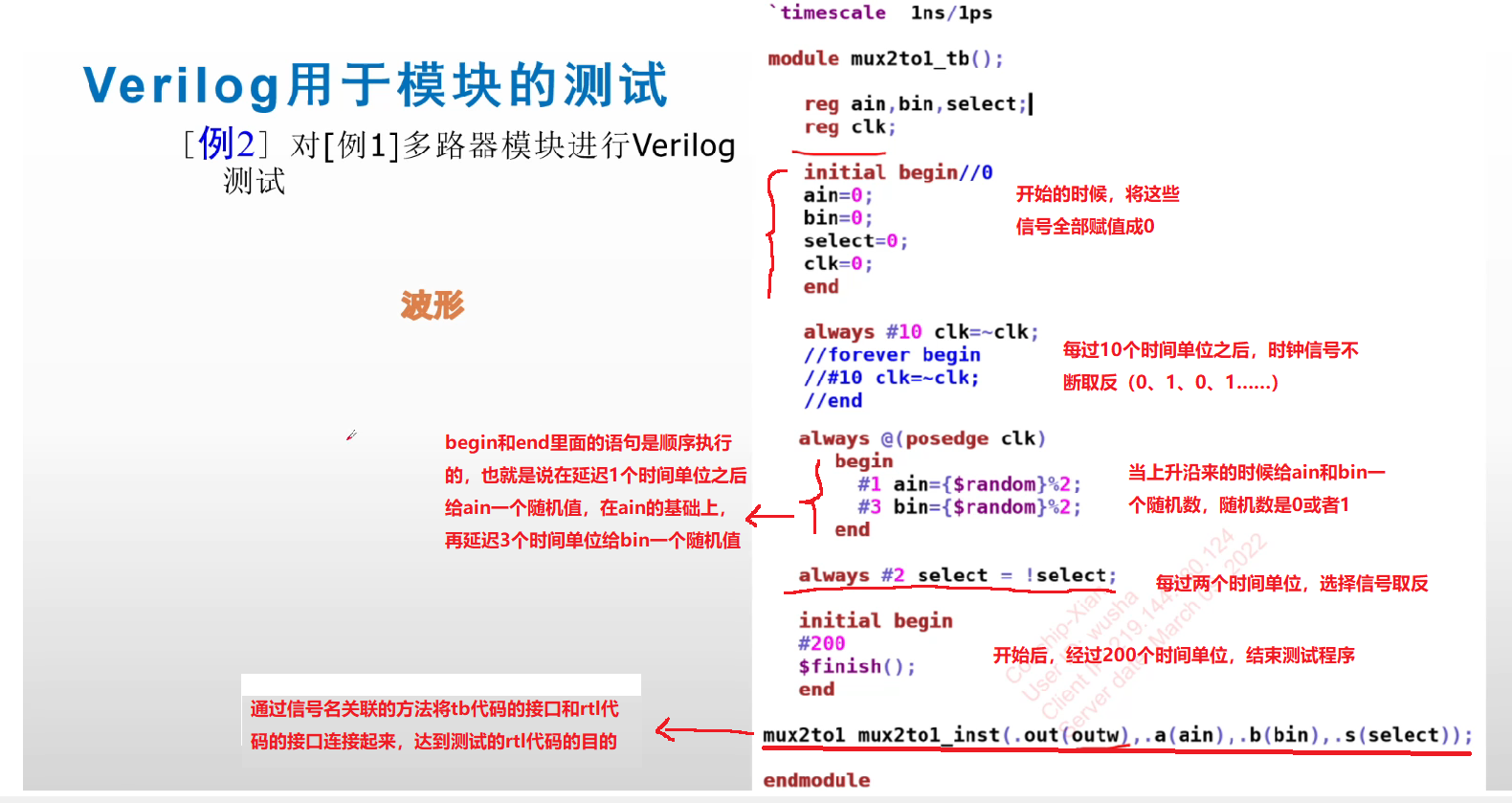

13.测试模块

13.测试模块