[FPGA开发工具使用总结]VIVADO在线调试(1)-信号抓取工具的使用

目录

- 1简介

- 2 添加观测信号的几种方法

- 2.1 通过定制IP核添加

- 2.2 通过约束文件添加

- 2.3 通过GUI生成DEBUG约束文件

- 2.4 两种方法的优点与缺点

- 3在线调试方法

- 3.1 器件扫描设置

- 3.2 触发条件设置

- 3.3 触发窗口设置

- 3.4 采样过程控制

- 4常见问题

- 4.1 时钟域的选择

- 4.2 缺少LTX文件

- 4.3 ILA无时钟

- 参考文档

1简介

在FPGA开发过程中,实时抓取信号进行观测是一种必不可少的问题分析手段。通常厂家会提供一种通过JTAG互联,逻辑资源定制的实时记录信号的调试手段。

通过阅读本文您可以了解到针对VIVADO开发工具的在线分析工具的使用方法。例如,如何添加被测信号,如何准确的观测到被测信号的典型现象,以及通常会遇到的问题等。

2 添加观测信号的几种方法

2.1 通过定制IP核添加

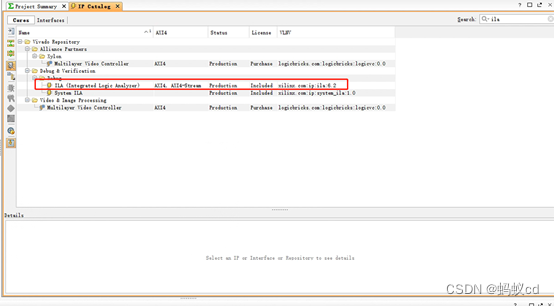

VIVADO提供了一个用于实时抓取信号的IP核,名为ILA(内部逻辑分析仪),用户使用时可在IP Catalog中直接搜索ila进行定制。

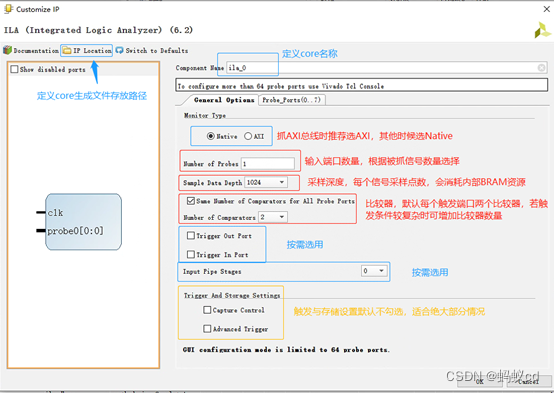

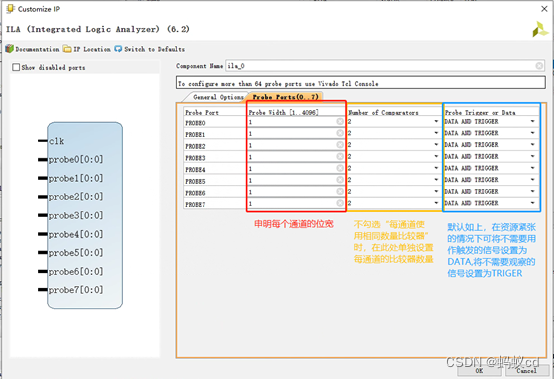

ILA core的定制非常简单,通常仅需如下配置即可满足需求。

在使用ILA Core时需要注意,输入被测信号的位宽可以小于等于ILA Core端口的位宽,但是不能使ILA Core端口为空,否则布局布线会失败。

在遇到难以解决的问题时,一个工程中会添加很多的ILA core,此时如果单独定制每一个Core会增加许多繁冗的工作,可先定制一个输入端口与位宽足够的Core,然后按需例化。

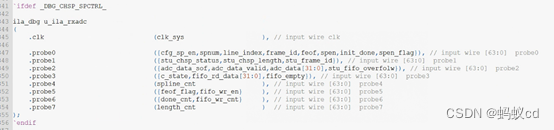

如下图是在某个工程中被调用的ILA Core,在调试时打开宏将ILA例化到工程中进行调试,完成调试后通过关闭宏屏蔽掉ILA,该方法可以避免在完成调试后删除ILA过程中的修改引入不必要的BUG。

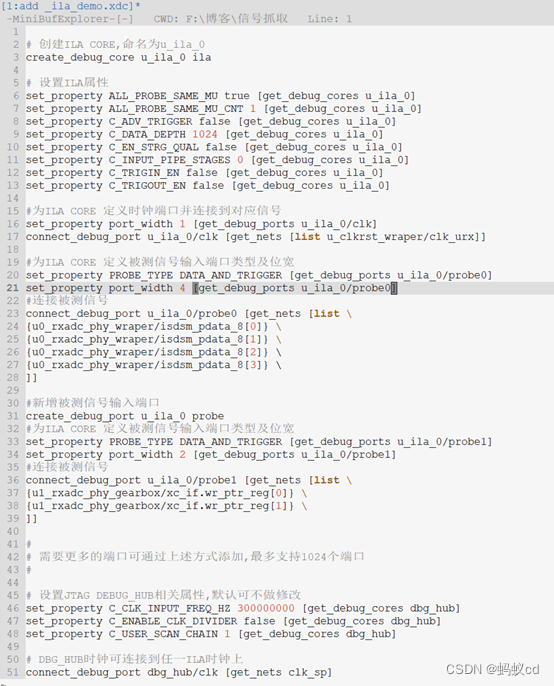

2.2 通过约束文件添加

通过编写XDC约束文件,亦可实现ILA添加,添加ILA Core的XDC示例文件如下所示。

使用此种方式需要对约束脚本非常熟悉。若不熟悉约束脚本的编写也可通过GUI界面生成约束文件;2.3节将介绍如何生成DEBUG的约束文件。

2.3 通过GUI生成DEBUG约束文件

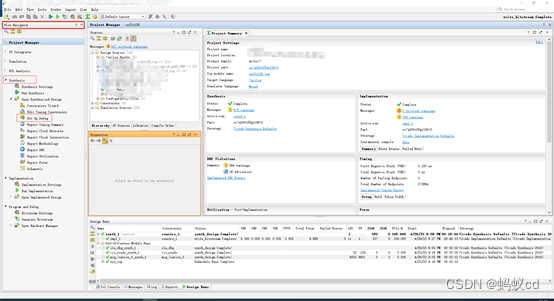

使用GUI生成约束文件需要先完成工程综合,然后在FlowNavigator窗口中打开Synthesized –>Open Synthesized Design –> Set Up Debug,等待加载设计。

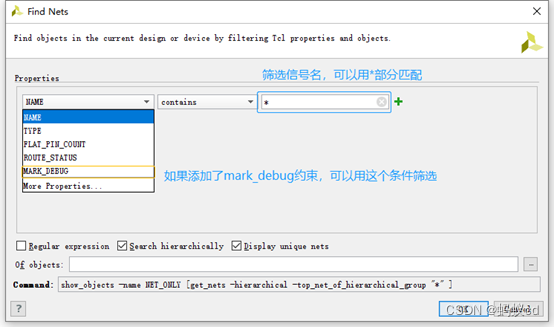

被测信号筛选及添加,综合后原来的信号名基本都会发生变化,可以在信号名的后面带上*以便准确的匹配到。

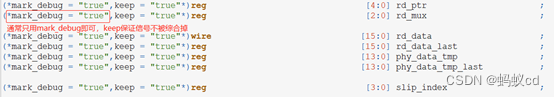

若想被测信号名称在综合时不被优化掉,可以在综合之前在代码中设置约束。添加mark_debug约束后,被测信号可以很方便的被筛选出来。

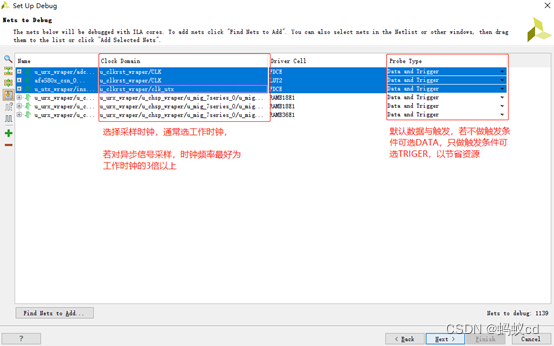

添加完信号后设置采样深度等。

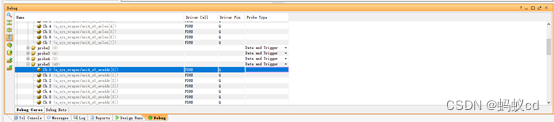

完成后可以在底部的Debug窗口看到添加的被观测信号,到这一步还没结束,还需要保存刚才生成的约束才可以重新编译。

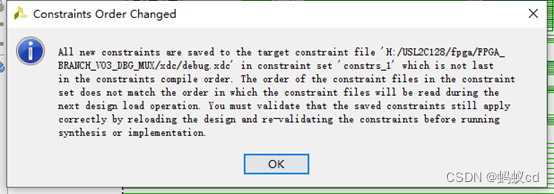

直接在Synthesized Design界面中按ctrl+s即可保存刚才生成的约束,弹出下图界面及保存成功。系统会默认保存到target的xdc文件中。推荐用一个专门的XDC文件来保存DEBUG相关约束。

2.4 两种方法的优点与缺点

VIVADO提供了通过IP Core核约束的两种方式添加在线分析逻辑的方法,两种方法优缺点如下所示。

| 优点 | 缺点 | |

|---|---|---|

| 通过IP Core添加 | IP Core自带网表,节省编译时间;在代码中直接例化,能够快速搭建测试平台。 | 对跨模块的信号不太友好,代码改动较大。 |

| 通过约束添加 | 方便跨模块信号观测;不在功能代码中做修改,方便完成调试后的代码整理。 | 编译较慢。 |

3在线调试方法

3.1 器件扫描设置

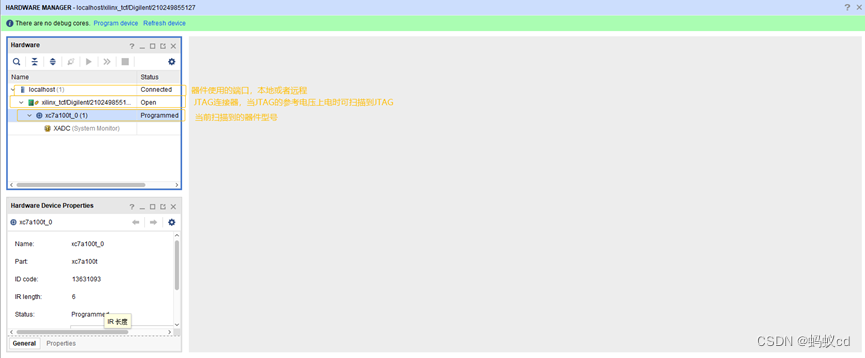

VIVADO器件扫描在Flow Navigator 窗口中Open Hardware Manager -> Open Target –>Auto Connect打开。

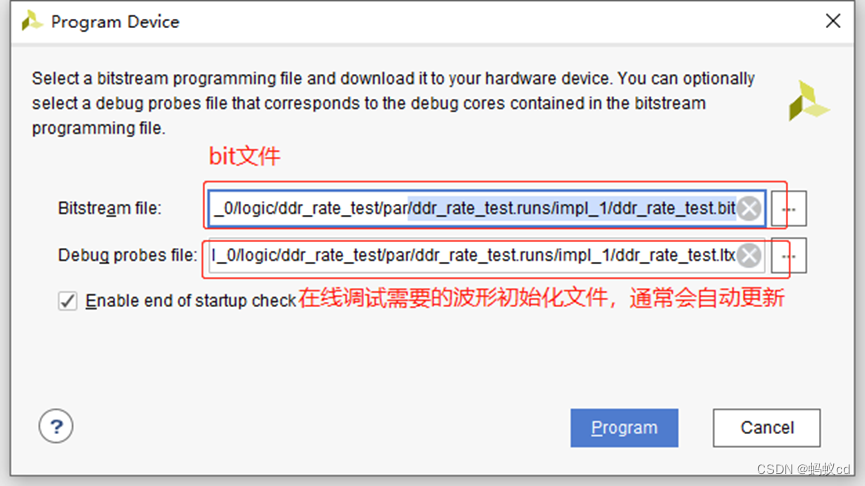

鼠标右键单击器件信号选择Program Device下载程序(bit文件)。VIVADO也支持将程序(mcs文件)烧写到FLASH启动然后添加LTX文件启动在线调试。

LTX文件在工程路径下/.runs/impl_1/debug_nets.ltx或者.ltx(*为工程名),这两个文件是一样的。烧写完成后会自动刷新出在线DEBUG的窗口,如果没有刷新,可以鼠标右键单击器件信号选择Refresh Device进行手动刷新。

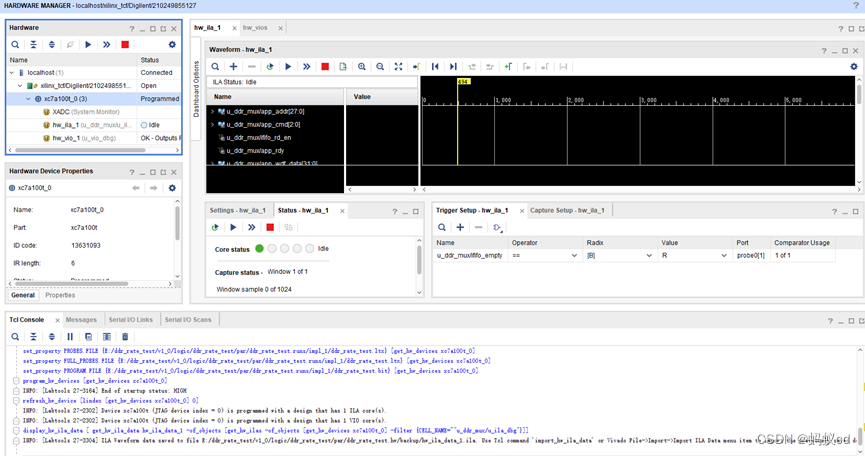

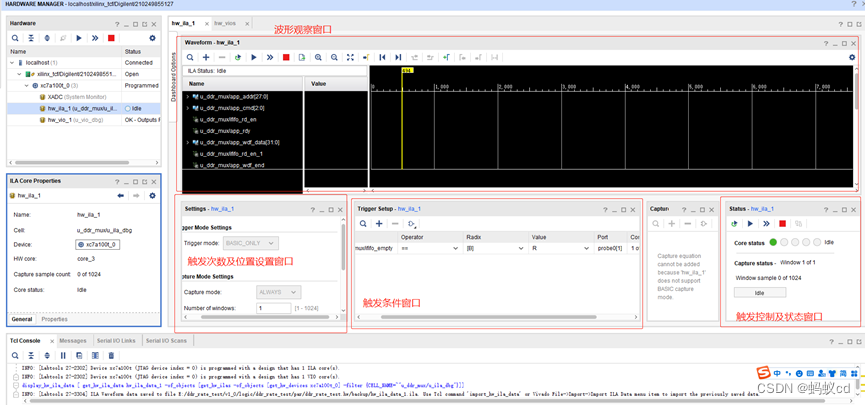

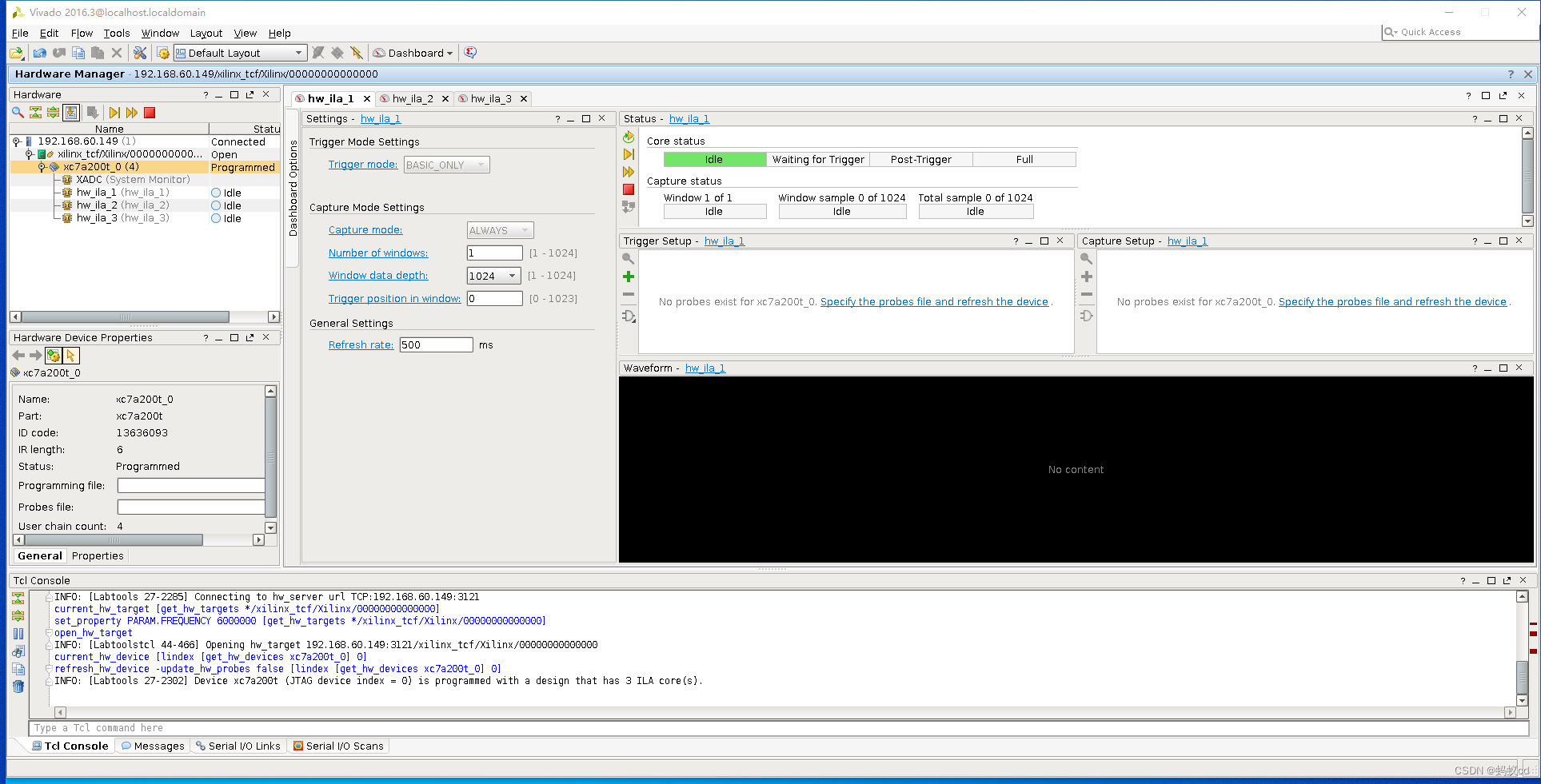

在线调试的界面如下,在大部分的调试过程中,需要用到的窗口有Waveform、Settings、Trigger Setup、Status等几个窗口。

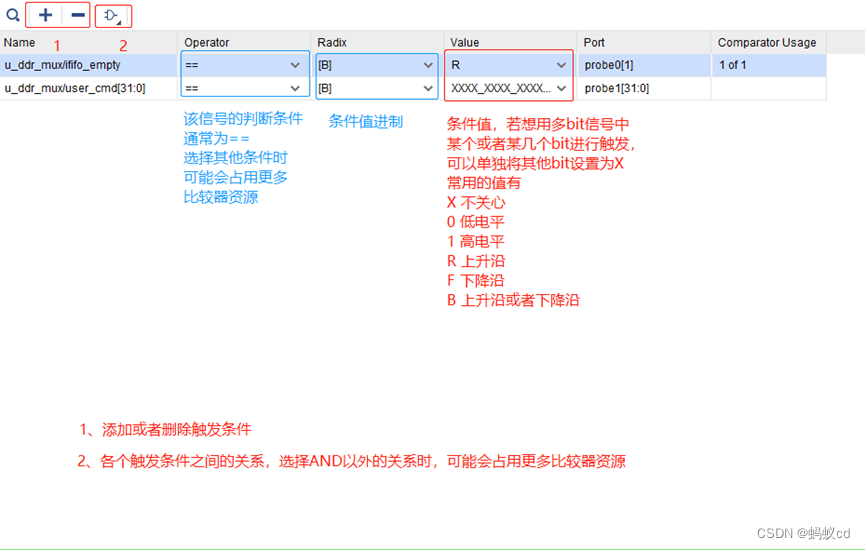

3.2 触发条件设置

触发条件设置如下。

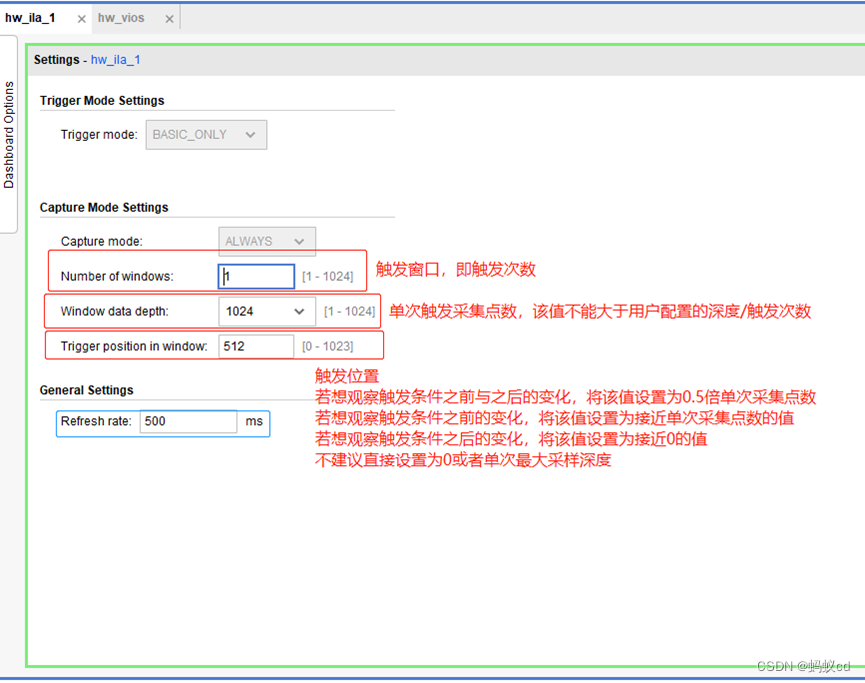

3.3 触发窗口设置

想要准确的观察到信号的变化情况,选择合适的触发窗口非常重要。通常可按如下推荐设置。

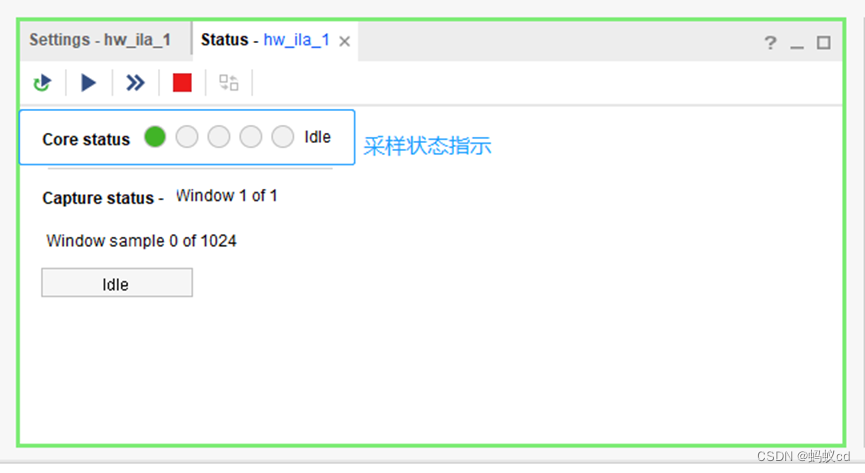

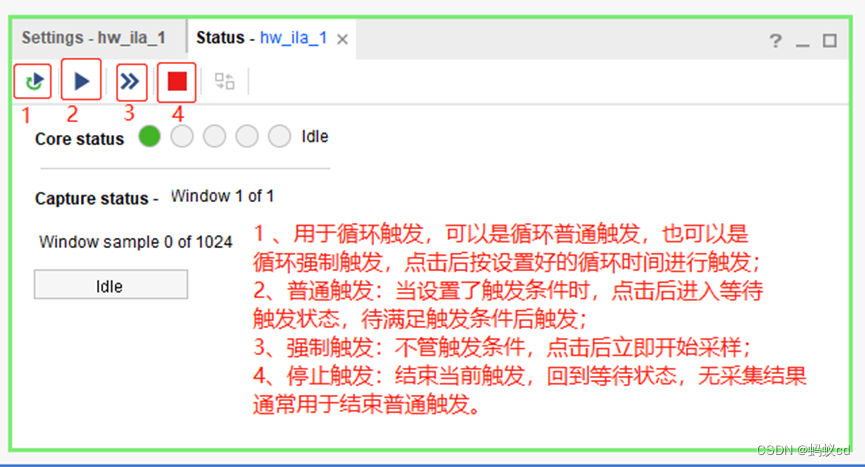

3.4 采样过程控制

用户可以通过Status窗口控制采样过程,每次采样需要经过空闲->预触发->等待触发->后触发->满(完成)等几个状态才能观察信号。整个过程会在status窗口中显示出来。

用户可以通过如下所示的按钮控制采样。

此处仅介绍了普通模式的触发方式,更详细的使用方式请参考Xilinx官方的文档UG936

4常见问题

4.1 时钟域的选择

Xilinx的FPGA器件内部有区域时钟、全局时钟、本地时钟等各种类型的时钟信号,在选择采样时钟时应充分考虑布局布线是否能够通过。通常推荐使用全局时钟作为采样时钟,此外若被测信号比较多时也推荐使用全局时钟。当必须使用区域时钟时,布局布线的通过率就必须考虑到。

在通过约束添加DEBUG信号时,需要注意的是,不同时钟采样的被测信号会被放置到不同的观测窗口中,不太容易做到同一时刻采样。也不能进行对比观察。

4.2 缺少LTX文件

如果烧写BIT文件后弹出出现如下界面,则是由于找不到LTX文件导致的。只需根据提示手动添加LTX文件即可。如果是通过FLASH启动,也会弹出如下界面。

4.3 ILA无时钟

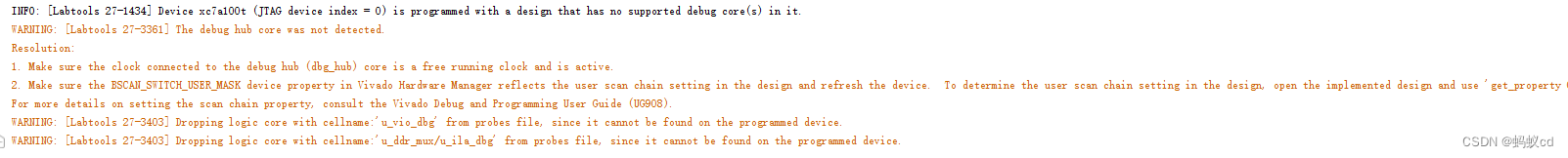

如果烧写BIT文件后不能正常弹出DEBUG窗口,手动刷新也没有时,观察Tcl Console窗口是有如下错误,则有很大可能性是没有采样时钟导致(不排除其他因素)。

参考文档

- ug936-vivado-tutorial-programming-debugging

- pg172-ila