电子技术——CMOS反相器

电子技术——CMOS反相器

在本节,我们深入学习CMOS反相器。

电路原理

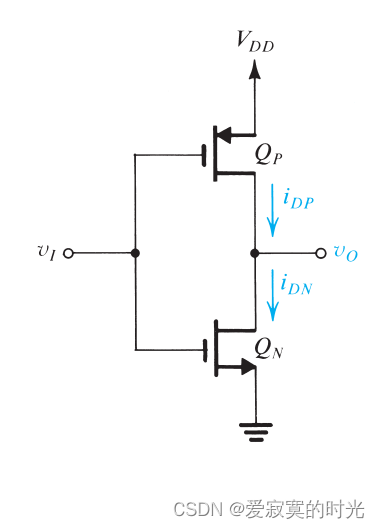

下图是我们要研究的CMOS反相器的原理图:

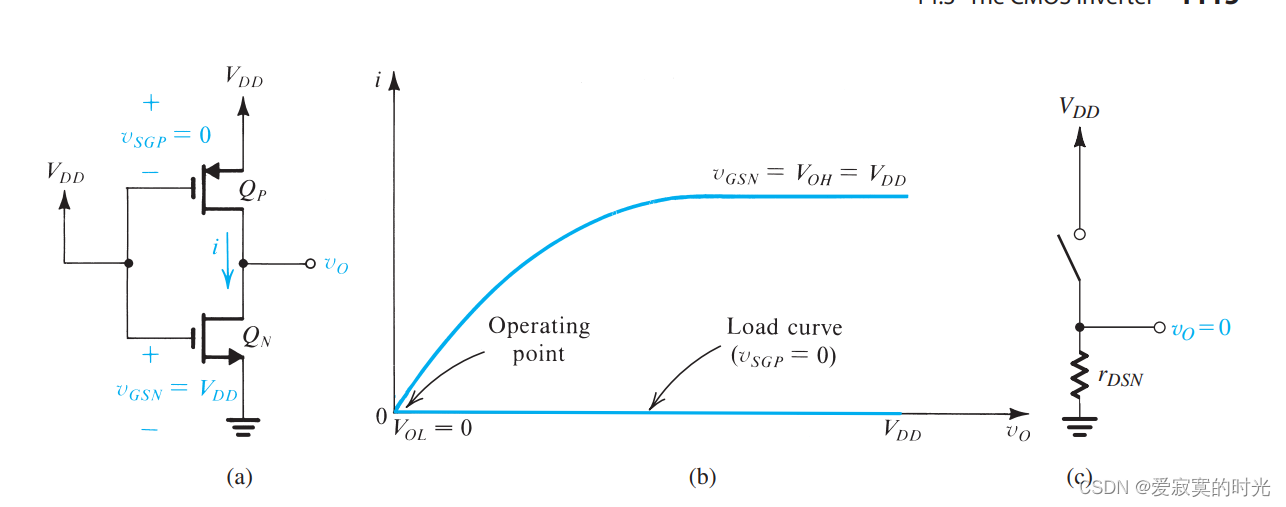

下图展示了当输入 vI=VDDv_I = V_{DD}vI=VDD 时的 iD−vDSi_D-v_{DS}iD−vDS 曲线:

我们把 QNQ_NQN 当做是驱动源,而 QPQ_PQP 作为负载,我们在图像上叠加关于 QPQ_PQP 在 vSGP=0v_{SGP} = 0vSGP=0 的负载曲线。因为 vSGP<∣Vt∣v_{SGP} < |V_t|vSGP<∣Vt∣ 因此负载曲线是一条零电流的水平直线。两个曲线的交点就是我们的工作点,我们发现此时电流为零,输出电压为零。同样意味着此时耗散功率为零。然而,工作点处在曲线 iD−vDSi_D-v_{DS}iD−vDS 的上升处,具有有限的斜率,因此 QNQ_NQN 对外表现出有限的阻抗,如图©:

rDSN=1/[kn′(WL)n(VDD−Vtn)]r_{DSN} = 1 / [k_n'(\frac{W}{L})_n (V_{DD} - V_{tn})] rDSN=1/[kn′(LW)n(VDD−Vtn)]

另外一种情况,当输入 vI=0v_I = 0vI=0 的时候,如图:

因为 vGSN=0v_{GSN} = 0vGSN=0 此时驱动曲线是一条零电流的直线,此时负载曲线是 vSGP=VDDv_{SGP} = V_{DD}vSGP=VDD 的曲线。我们发现,此时交点在零电流,输出电压为 vO=VDDv_O = V_{DD}vO=VDD 。耗散功率为零。同样的,QPQ_PQP 表现出有限的阻抗:

rDSP=1/[kp′(WL)p(VDD−∣Vtp∣)]r_{DSP} = 1 / [k_p' (\frac{W}{L})_p (V_{DD} - |V_{tp}|)] rDSP=1/[kp′(LW)p(VDD−∣Vtp∣)]

虽然,静态电流为零,这种CMOS反相器可以提供较大的负载能力。例如,负载是容性负载的时候,当 QNQ_NQN 导通的时候,由于其较小的开关阻抗,可以提供一个较短的对地回路,可以使得容性负载迅速泄放电荷,拉低电位,因此 QNQ_NQN 称为下拉元件。同样的,当 QPQ_PQP 导通的时候,由于其较小的开关阻抗,可以提供一个较短的对电压通路,可以使得容性负载迅速充满电荷,拉高电位,因此 QPQ_PQP 称为上拉元件。

根据上面的讨论CMOS反相器作为理想的反相器:

- 输出电压的范围在 0−VDD0-V_{DD}0−VDD 电压压摆达到最大。同时,两个MOS可以进行匹配使得提供一个对称的电压传导特性,具有较宽的噪声容限。

- 静态功率为零,这是因为电压源和地直接没有直接的DC回路。

- 对地和电压都是低阻抗路径,较低的输出阻抗使得反相器具有较高的驱动能力,以及实现电气功能与元件参数无关,提高噪声和其他干扰的容忍性。

- 上拉的下拉元件使得电路的翻转速度更快,对于容性负载具有较高的驱动能力。

- 输入阻抗为无穷大。所以CMOS反相器可以驱动大量同样的CMOS反相器而不造成电压水平损失。当然,增加被驱动元件的数量就意味着增加了容性负载,这会降低电平的翻转速度。

电压传导特性

通过联立两个曲线,我们可以绘制出CMOS反相器的电压传导特性曲线,这里给出驱动和负载方程:

iDN=kn′(WL)n[(vI−Vtn)vO−12vO2],vO≤vI−Vtni_{DN} = k_n'(\frac{W}{L})_n [(v_I - V_{tn})v_O - \frac{1}{2}v_O^2], v_O \le v_I - V_{tn} iDN=kn′(LW)n[(vI−Vtn)vO−21vO2],vO≤vI−Vtn

iDN=12kn′(WL)n(vI−Vtn)2,vO≥vI−Vtni_{DN} = \frac{1}{2}k_n' (\frac{W}{L})_n (v_I - V_{tn})^2, v_O \ge v_I - V_{tn} iDN=21kn′(LW)n(vI−Vtn)2,vO≥vI−Vtn

iDP=kp′(WL)p[(VDD−vI−∣Vtp∣)(VDD−vO)−12(VDD−vO)2],vO≥vI+∣Vtp∣i_{DP} = k_p' (\frac{W}{L})_p [(V_{DD} - v_I - |V_{tp}|)(V_{DD} - v_O) - \frac{1}{2}(V_{DD} - v_O)^2], v_O \ge v_I + |V_{tp}| iDP=kp′(LW)p[(VDD−vI−∣Vtp∣)(VDD−vO)−21(VDD−vO)2],vO≥vI+∣Vtp∣

iDP=12kp′(WL)p(VDD−vI−∣Vtp∣)2,vO≤vI+∣Vtp∣i_{DP} = \frac{1}{2} k_p' (\frac{W}{L})_p(V_{DD} - v_I - |V_{tp}|)^2, v_O \le v_I + |V_{tp}| iDP=21kp′(LW)p(VDD−vI−∣Vtp∣)2,vO≤vI+∣Vtp∣

通常电路设计者通常将阈值电压设计为 Vtn=∣Vtp∣=VtV_{tn} = |V_{tp}| = V_tVtn=∣Vtp∣=Vt 。同样,尽管并不总是这样,我们也假设两个MOS完全匹配,即 kn′(W/L)n=kp′(W/L)pk_n'(W/L)_n = k_p'(W/L)_pkn′(W/L)n=kp′(W/L)p 。因为存在电子速率差异,当两个MOS具有相同的长度的时候,其宽度满足:

WpWn=μnμp\frac{W_p}{W_n} = \frac{\mu_n}{\mu_p} WnWp=μpμn

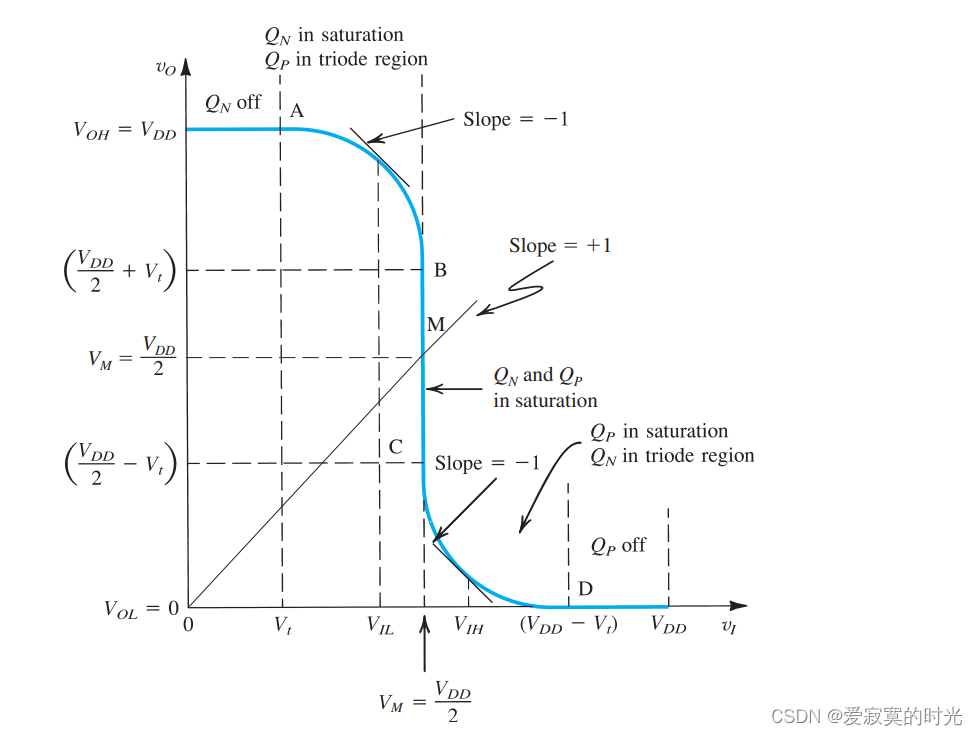

此时电路具有对称的传递特性,以及相同的负载驱动能力。电压传导特性如图:

其中BC段为MOS的放大器区,因为我们忽略了沟道宽度调制效应,因此在BC端具有无限大的增益。由于电路的对称性,传导中点发生在 VM=VDD/2V_M = V_{DD} / 2VM=VDD/2 的地方,上下边界点为 vO(B)=VDD/2+Vtv_O(B) = V_{DD} / 2 + V_tvO(B)=VDD/2+Vt (QPQ_PQP 进入三极管区) 以及 vO(C)=VDD/2−Vtv_O(C) = V_{DD} / 2 -V_tvO(C)=VDD/2−Vt(QNQ_NQN 进入三极管区)。

为了决定点 VIHV_{IH}VIH 的位置,我们注意到此时 QNQ_NQN 进入三极管区,通过电流相等我们联立方程:

(vI−Vt)vO−12vO2=12(VDD−vI−Vt)2(v_I - V_t)v_O - \frac{1}{2} v_O^2 = \frac{1}{2} (V_{DD} - v_I - V_t)^2 (vI−Vt)vO−21vO2=21(VDD−vI−Vt)2

对 vOv_OvO 求导可得:

(vI−Vt)dvOdvI+vO−vOdvOdvI=−(VDD−vI−Vt)(v_I - V_t) \frac{dv_O}{dv_I} + v_O - v_O \frac{dv_O}{dv_I} = -(V_{DD} - v_I - V_t) (vI−Vt)dvIdvO+vO−vOdvIdvO=−(VDD−vI−Vt)

带入 vI=VIHv_I = V_{IH}vI=VIH 以及 dvOdvI=−1\frac{dv_O}{dv_I} = -1dvIdvO=−1 我们得到:

vO=VIH−VDD2v_O = V_{IH} - \frac{V_{DD}}{2} vO=VIH−2VDD

带入 vI=VIHv_I = V_{IH}vI=VIH 得到 vOv_OvO 带回上式得到:

VIH=18(5VDD−2Vt)V_{IH} = \frac{1}{8} (5V_{DD} - 2V_t) VIH=81(5VDD−2Vt)

同样的做法我们得到:

VIL=18(3VDD+2Vt)V_{IL} = \frac{1}{8} (3V_{DD} + 2V_t) VIL=81(3VDD+2Vt)

可以计算出噪声容限:

NMH=VOH−VIH=18(3VDD+2Vt)NM_H = V_{OH} - V_{IH} = \frac{1}{8}(3V_{DD} + 2V_t) NMH=VOH−VIH=81(3VDD+2Vt)

NML=VIL−VOL=18(3VDD+2Vt)NM_L = V_{IL} - V_{OL} = \frac{1}{8}(3V_{DD} + 2V_t) NML=VIL−VOL=81(3VDD+2Vt)

正如期望的那样,若两个MOS完全一样,则此时传导特性完全对称。

MOS不完全匹配的情况

若我们想使得MOS完全匹配,那么PMOS器件的尺寸就要是NMOS尺寸的3到4倍。这会导致更大的硅区域。一方面浪费了一些硅区域,为器件小型化造成了不利条件,另一方面增加了器件的容性阻抗,增加了CMOS反相器的时间延迟。因此,通常情况下MOS是不完全匹配。

首先我们推导不完全匹配下的M点,因为两个MOS都工作在饱和区,因此带入 vI=vO=VMv_I = v_O = V_MvI=vO=VM 我们得到:

VM=r(VDD−∣Vtp∣)+Vtnr+1V_M = \frac{r(V_{DD} - |V_{tp}|) + V_{tn}}{r + 1} VM=r+1r(VDD−∣Vtp∣)+Vtn

这里:

r=kpkn=μpWpμnWnr = \sqrt{\frac{k_p}{k_n}} = \sqrt{\frac{\mu_p W_p}{\mu_n W_n}} r=knkp=μnWnμpWp

这里我们让 LLL 的长度相同,通常是在指定工艺下的最小精度值,注意到当MOS完全匹配的时候,此时 r=1r = 1r=1 。对于 ∣Vtp∣=Vtn|V_{tp}| = V_{tn}∣Vtp∣=Vtn 并且 r=1r = 1r=1 产生 VM=VDD/2V_M = V_{DD} / 2VM=VDD/2 。对于给定 VDDV_{DD}VDD 和 VtnV_{tn}Vtn 以及 VtpV_{tp}Vtp 则 VMV_MVM 是一个和工艺参数 rrr 相关的函数。例如,在0.18um工艺下:

我们可以总结关键两点:

- VMV_MVM 随着 rrr 的增大而增大。因此,让 kp>knk_p > k_nkp>kn 则 VMV_MVM 向 VDDV_{DD}VDD 偏移,让 kp<knk_p < k_nkp<kn 则 VMV_MVM 向 000 偏移。

- VMV_MVM 并不是与 rrr 强相关,例如让 rrr 降低两倍,则 VMV_MVM 降低0.13V。

第2条告诉我们,若我们能够接受极小的 NMLNM_LNML 减小和 VMV_MVM 点偏移,我们可以不让MOS完全匹配,从而提高器件性能等等。