【FPGA】Verilog:BCD 加法器的实现

0x00 XOR 运算在 2 的补码加减法中的应用

2 的补码加减法的特点是,当从某个数中减去负数时,将其转换为正数的加法来计算,并将减去正数的情况转换为负数的加法来计算,从而将所有减法运算转换为加法运算。在这种情况下,两个数的加法运算中产生进位的情况是在加法位的所有位都为 1 时。

换句话说,可以使用 AND 门来检测产生进位的情况。在两个数的加法运算中,进位传播的情况是在加法位的两个位中只有一个被设置为 1 时。这是因为从较低位传递上来的进位位会再次传递到下一个位,因此可以使用 XOR 门来检测进位传播的情况。

- carry-generate funciton:

- carry-propagate function:

0x01 BCD 运算

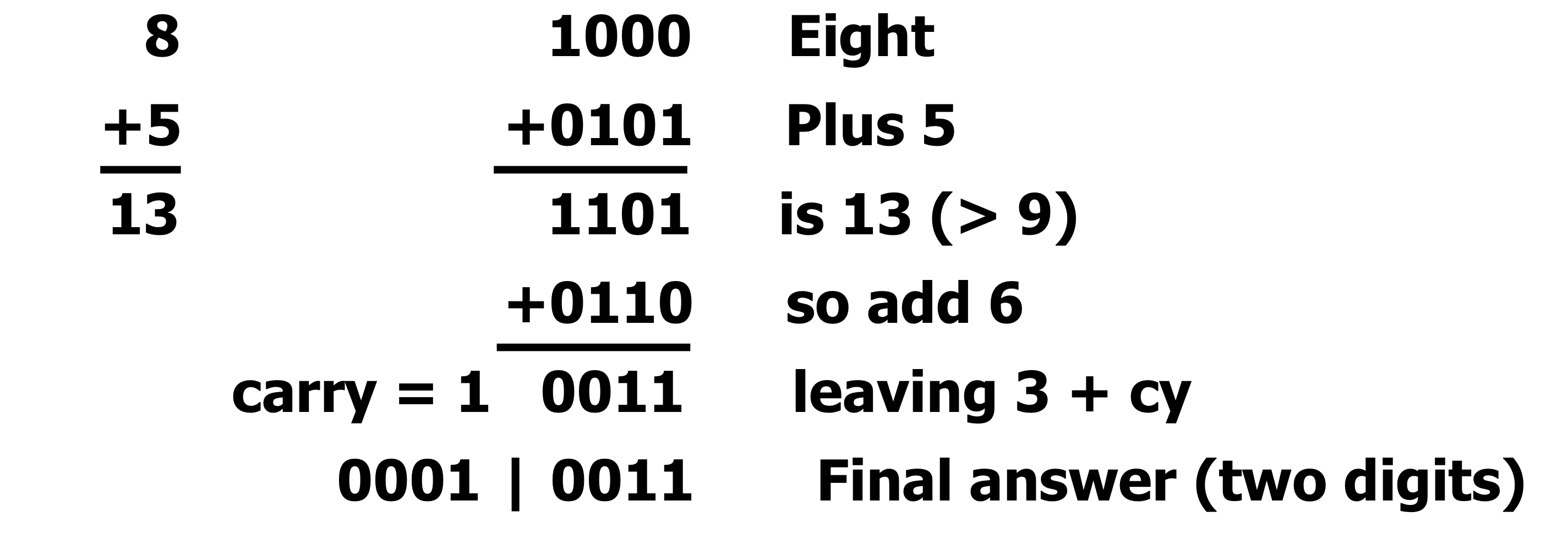

在 BCD 中,使用4位值作为操作数,但由于只表示 0 到 9 的数字,因此只使用 0000 到 1001 的二进制数,而不使用 1010 到 1111 的二进制数(don't care)。

因此,不能使用常规的 2'complement 运算来计算,需要额外的处理:如果 4 位二进制数的运算结果在 1010 到 1111 的范围内,需要将 6 (即 0110),添加到运算结果中。

| BCD 运算例子 |

|

|

0x02 BCD 加法器的实现

关于 BCD 加法器的结果和模拟过程进行说明(Verilog源代码,输出示例,详细描述过程)。

💬 Design source:

module BCD2(input Cin,input a1,input a2,input a3,input a4,input b1,input b2,input b3,input b4,output sum1,output sum2,output sum3,output sum4,output cout);

wire s1,s2,s3,s4;

wire c1,c2,c3,c4;

wire C1,C2,C3,C4;assign s1 = (a1^b1)^Cin;

assign c1 = (Cin && (a1^b1)) || (a1 && b1);assign s2 = (a2^b2)^c1;

assign c2 = (c1 && (a2^b2)) || (a2 && b2);assign s3 = (a3^b3)^c2;

assign c3 = (c2 && (a3^b3)) || (a3 && b3);assign s4 = (a4^b4)^c3;

assign c4 = (c3 && (a4^b4)) || (a4 && b4);///

assign cout = (c4 || (s3 && s4) || (s2 && s4));assign sum1 = s1;

assign C1 = (0 && (s1^0)) || (s1 && 0);assign sum2 = (s2^cout)^C1;

assign C2 = (C1 && (s2^cout)) || (s2 && cout);assign sum3 = (s3^cout)^C2;

assign C3 = (C2 && (s3^cout)) || (s3 && cout);assign sum4 = (s4^0)^C3;

assign C4 = (C3 && (s4^0)) || (s4 && 0);endmodule💬 Testbench:

`timescale 1ns / 1psmodule BCD2_tb;

reg Cin,a1,a2,a3,a4,b1,b2,b3,b4;

wire sum1,sum2,sum3,sum4,cout;BCD2 u_BCD2 (.Cin(Cin ),.a1(a1 ),.a2(a2 ),.a3(a3 ),.a4(a4 ),.b1(b1 ),.b2(b2 ),.b3(b3 ),.b4(b4 ),.sum1(sum1 ),.sum2(sum2 ),.sum3(sum3 ),.sum4(sum4 ),.cout(cout )

);initial beginCin = 1'b0;a1 = 1'b0;a2 = 1'b0;a3 = 1'b0;a4 = 1'b0;b1 = 1'b0;b2 = 1'b0;b3 = 1'b0;b4 = 1'b0;

endalways@(Cin or a1 or a2 or a3 or a4 or b1 or b2 or b3 or b4) beginCin <=#10 ~Cin;a1 <= #20 ~a1;a2 <= #40 ~a2;a3 <= #80 ~a3;a4 <= #160 ~a4;b1 <= #320 ~b1;b2 <= #640 ~b2;b3 <= #1280 ~b3;b4 <= #2560 ~b4;

endinitial begin#5120$finish;

endendmodule🚩 运行结果如下:

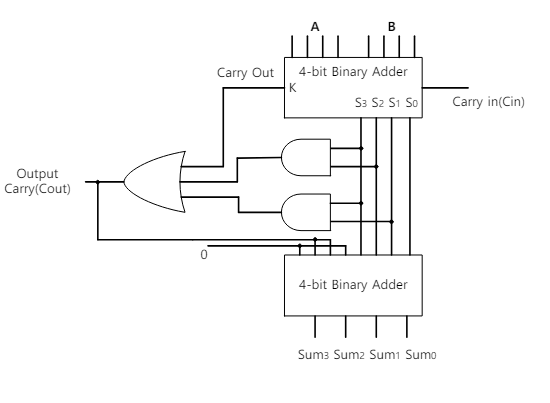

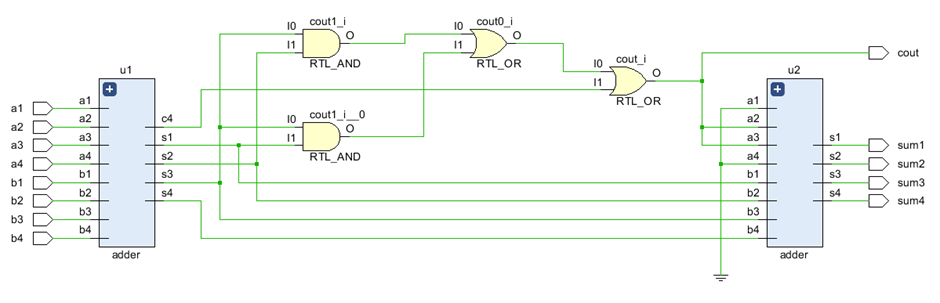

📜 Schematic:

实现的 BCD 加法器是一种将 4 位加法器运算结果转换为 BCD 表示的设备。如果运算结果是一个大于 9 的数字,我们只需加上 6 (0110)。为了实现这一点,该装置由两个加法器电路组成:一个用于执行 4 位加法器运算,另一个电路用于在第一个运算结果大于 9 时加上 0110(补偿电路)。

实现的 BCD 加法器是一种将 4 位加法器运算结果转换为 BCD 表示的设备。如果运算结果是一个大于 9 的数字,我们只需加上 6 (0110)。为了实现这一点,该装置由两个加法器电路组成:一个用于执行 4 位加法器运算,另一个电路用于在第一个运算结果大于 9 时加上 0110(补偿电路)。

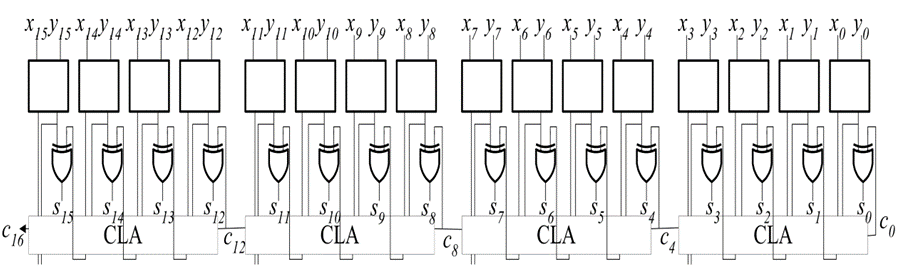

0x03 补充:Single-level 16 bit 超前进位加法器

四个 4 位超前进位加法器可以合并成一个 16 位超前进位加法器。它是四个并行结构的串行连接,是并行和串行结构的混合体。

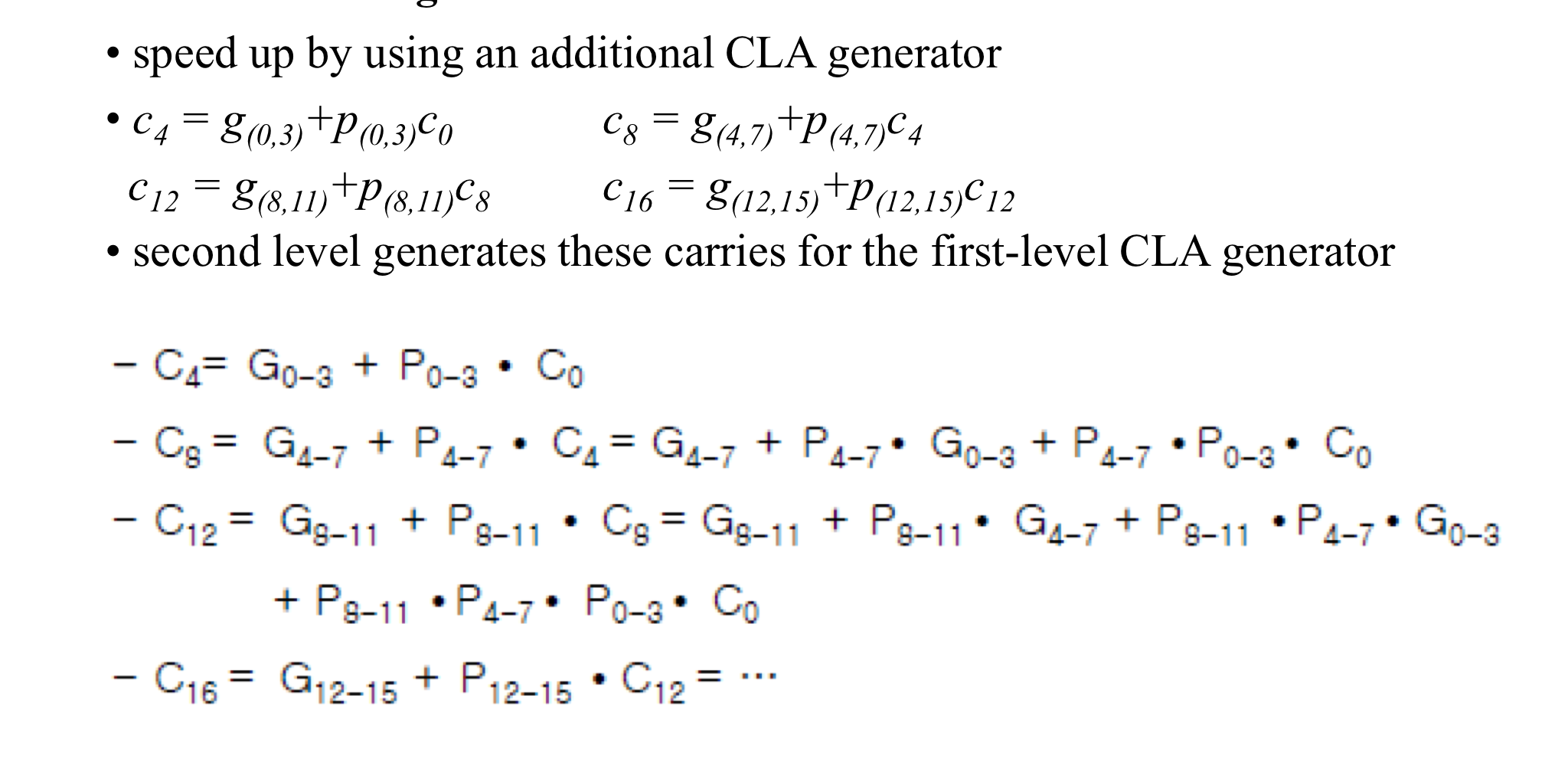

0x04 补充:2-level 16-bit 超前进位加法器

2 级 16 位超前进位加法器是一种通过使用双 CLA 发生器,比单级 16 位超前进位加法器更能减少通过栅极所需的延迟的结构。

| 2-level 16-bit Carry Look-ahead Adder |

|

|

📌 [ 笔者 ] 최역우(韩)

📃 [ 更新 ] 2022.9.20

❌ [ 勘误 ] /* 暂无 */

📜 [ 声明 ] 由于作者水平有限,本文有错误和不准确之处在所难免,本人也很想知道这些错误,恳望读者批评指正!| 📜 参考资料 Introduction to Logic and Computer Design, Alan Marcovitz, McGrawHill, 2008 Microsoft. MSDN(Microsoft Developer Network)[EB/OL]. []. . 百度百科[EB/OL]. []. https://baike.baidu.com/. |