数字IC前端学习笔记:时钟切换电路

相关阅读

数字IC前端![]() https://blog.csdn.net/weixin_45791458/category_12173698.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12173698.html?spm=1001.2014.3001.5482

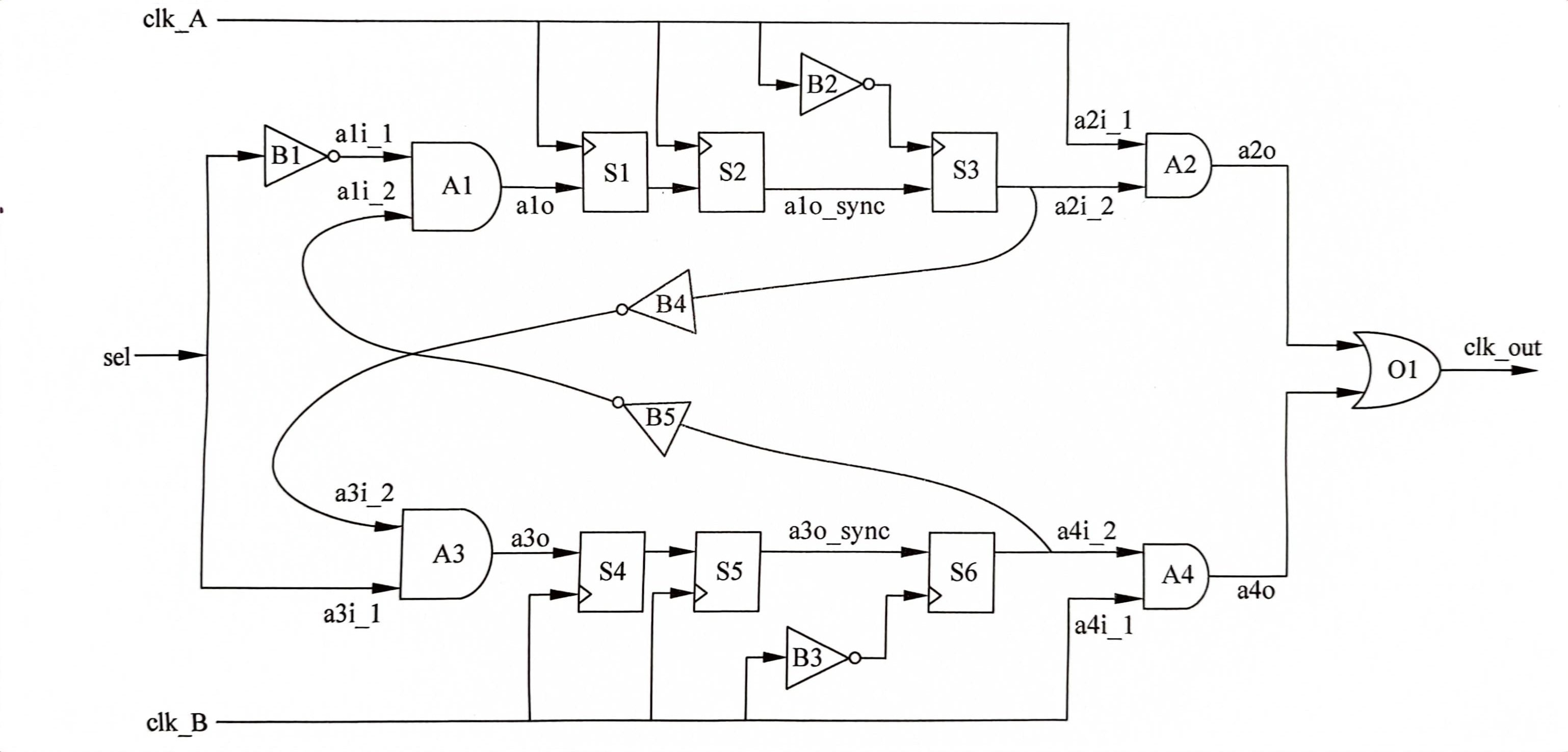

有些时候我们需要在系统运行时切换系统时钟,最简单的方法就是使用一个MUX(数据选择器)选择输出的时钟,如下代码片所示。但这样做会导致毛刺的产生,这可能会导致寄存器的输出产生亚稳态。由于时钟在一个系统内是如此的重要,这种亚稳态可能会使整个系统宕机。一个简单的使用数据选择器的时钟切换电路如下图1所示,时钟切换时的毛刺如图2所示。

module clock_switch(input clk_1, clk_2, select, output reg clk_out);always@(*) beginif(select == 1'b1)clk_out = clk_1;elseclk_out = clk_2;end

endmodule

图1 简单的数据选择器

图2 有毛刺的波形

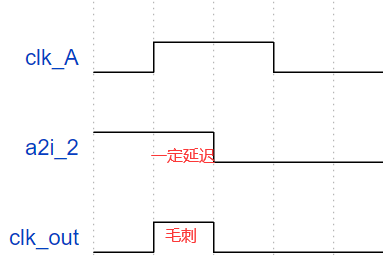

一种不会产生毛刺的时钟切换电路如下图3所示。该电路的输出为两个时钟门控输出的与,上半部分电路控制时钟clk_A,当门控信号a2i_2为1时门控关闭时钟clk_A,当门控信号a2i_2为0时门控打开时钟clk_A。下半部分电路控制时钟clk_B,当门控信号a4i_2为1时门控关闭时钟clk_B,当门控信号a4i_2为0时门控打开时钟clk_B。控制信号sel用于选择clk_A还是clk_B,当sel为0时a3o输出0,由于sel和a3i_2信号都不是clk_B时钟域的信号,因此这个输出需要经过clk_B时钟域的两级同步器得到a3o_sync信号,最后a3o_sync信号通过clk_B的下降沿采样得到a4i_2和!a4i_2,a4i_2用于关闭clk_B,而!a4i_2用于拉高a1o,从而最后将a2i_2拉高,即打开时钟clk_A(注意到对于a1o,即使sel为0,a1i_1为1,也不会立刻拉高,因为!a4i_2仍然为0),对sel为1的分析与上面类似,在此不详述。可以看到这种结构在时钟切换的过程中,首先关闭正在运行的时钟(此时没有时钟输出,输出恒为0),然后再开启另一个时钟,且这个关闭和开启的动作都是由本时钟所同步的行为,即clk_A负责关闭和开启clk_A,clk_B负责关闭和开启clk_B,这样就在一定程度上避免了毛刺的产生。S3和S6这两个触发器需要下降沿触发,这是为了在关闭和打开时钟时不产生毛刺,因为寄存器S3和S6的输出有一定延迟。如果使用上升沿触发,此时时钟信号为高电平,但门控信号a2i_2和a4i_2需要延迟一段时间才会拉高或拉低,此时会在a20和a4o产生毛刺,下降沿触发则不会有这个问题,因为时钟信号为低,这保证了a20和a4o一定为低,如图4和图5所示。但值得注意的是,这在无形中对时钟的占空比提出了要求,即占空比不能太高,最好为50%左右,否则还是会导致输出出现毛刺(在S3,S6延迟较大时)。图中的B2、B3、B4、B5实际综合后可能不存在,因为有专门的下降沿触发的寄存器,同时寄存器也有取反输出端。

图3 无毛刺的时钟切换电路

图4 使用上升沿触发出现毛刺

图4 使用下升沿触发不出现毛刺

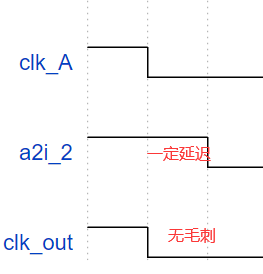

图5是没有毛刺的切换电路的波形图,可以看到切换有一定延迟但不会出现毛刺。

图5 没有毛刺的波形

下面是以上电路的Verilog描述,在这里面要注意S3和S6的时钟触发沿。

module clock_switch(input clk_1, clk_2, select, rst_n1, rst_n2, output clk_out);

//上半部分时钟控制的逻辑 wire a1i_1, a1o, a2o;reg a1o_r, a1o_syn, a2i_2, a4i_2;assign a1i_1 = !select;assign a1o = a1i_1 & !a4i_2;always@(posedge clk_1 or negedge rst_n1)begin //打两拍同步if(!rst_n1)begina1o_r <= 0;a1o_syn <= 0;endelse begina1o_r <= a1o;a1o_syn <= a1o_r;endendalways@(negedge clk_1 or negedge rst_n1)begin //注意这里用下降沿触发if(!rst_n1)a2i_2 <= 0;elsea2i_2 <= a1o_syn;endassign a2o = a2i_2 & clk_1;//下半部分时钟控制的逻辑 wire a3o, a4o;reg a3o_r, a3o_syn;assign a3o = select & !a2i_2;always@(posedge clk_2, negedge rst_n2)begin //打两拍同步if(!rst_n2)begina3o_r <= 0;a3o_syn <= 0;endelse begina3o_r <= a3o;a3o_syn <= a3o_r;endendalways@(negedge clk_2 or negedge rst_n2)begin //注意这里用下降沿触发if(!rst_n2)a4i_2 <= 0;elsea4i_2 <= a3o_syn;endassign a4o = a4i_2 & clk_2;//输出的与门逻辑assign clk_out = a2o | a4o;

endmodule

文中图3来源于《数字IC设计入门》