北邮22级信通院数电:Verilog-FPGA(9)第九周实验(1)实现带同步复位功能、采用上升沿触发的D触发器

北邮22信通一枚~

跟随课程进度更新北邮信通院数字系统设计的笔记、代码和文章

持续关注作者 迎接数电实验学习~

获取更多文章,请访问专栏:

北邮22级信通院数电实验_青山如墨雨如画的博客-CSDN博客

目录

一.顶层模块的书写

二.两种验证方法

2.1使用FPGA开发板验证

2.1.1管脚分配

2.1.2实验效果

2.2使用仿真验证

2.2.1仿真代码的书写

2.2.2仿真结果

一.顶层模块的书写

D_trigger.v

module D_trigger

(input clk,input rst,input d,output reg q

);always @ ( posedge clk or negedge rst)begin if(!rst)q<=1'b0;else q<=d;end

endmodule二.两种验证方法

2.1使用FPGA开发板验证

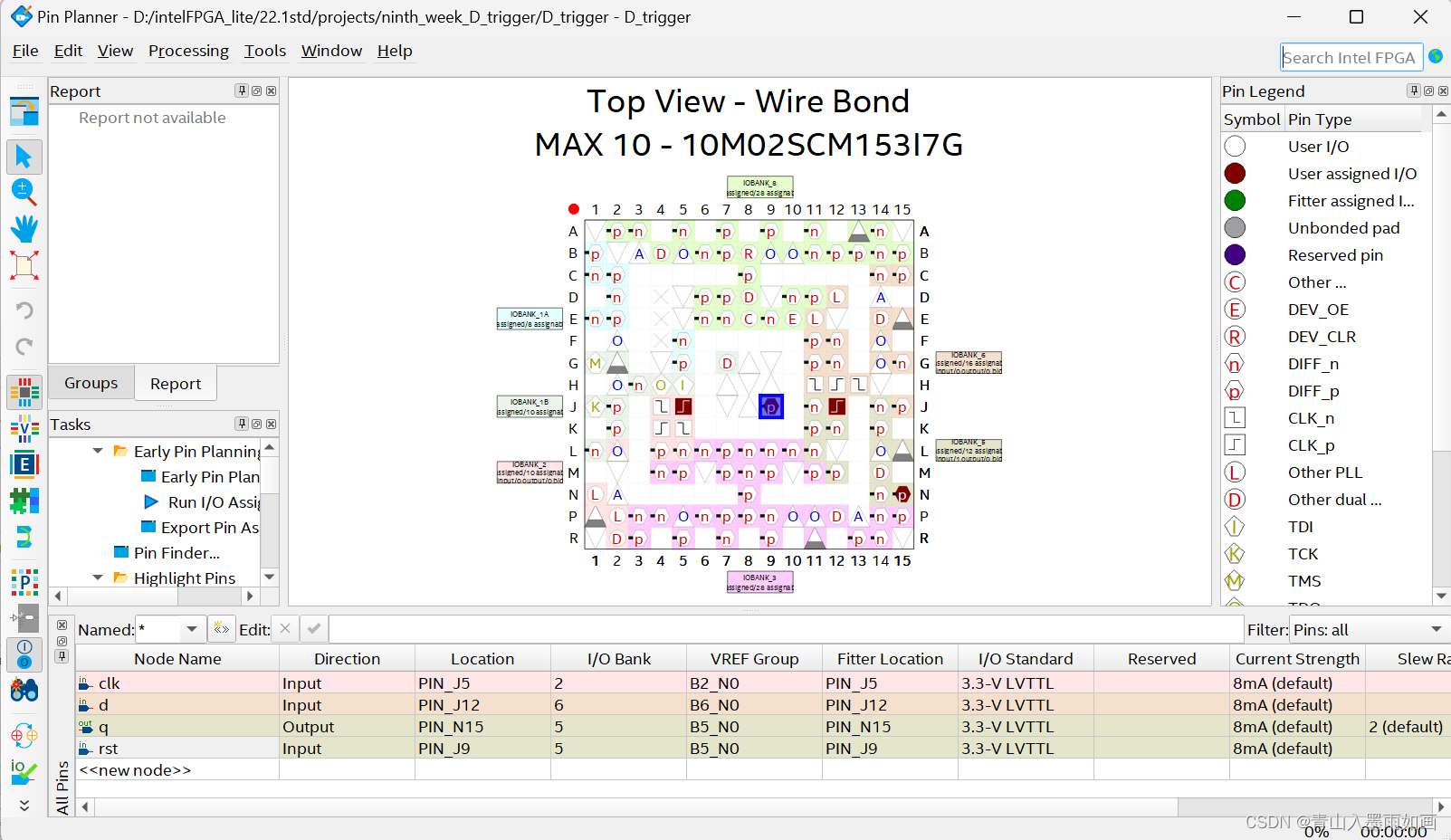

2.1.1管脚分配

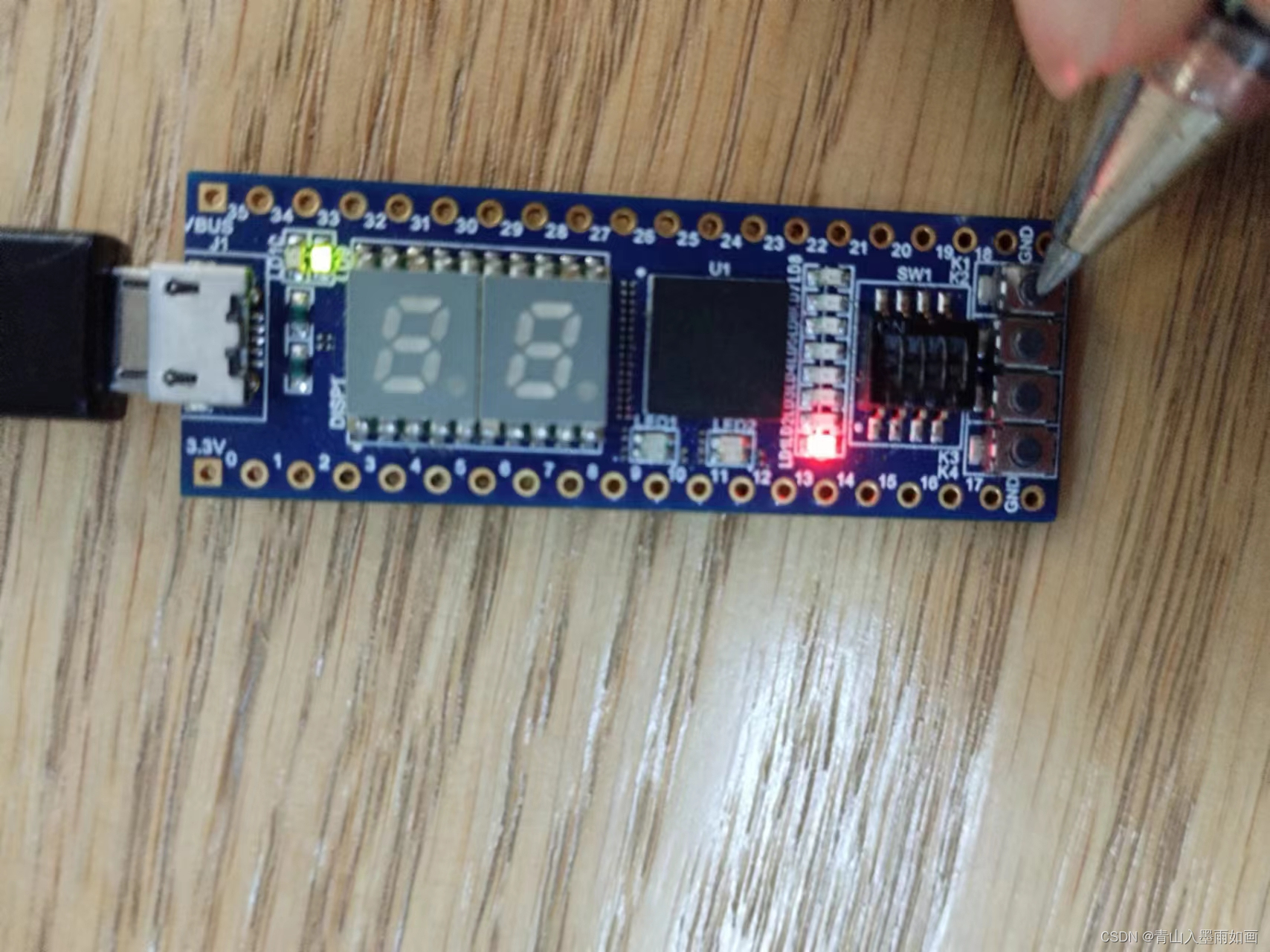

2.1.2实验效果

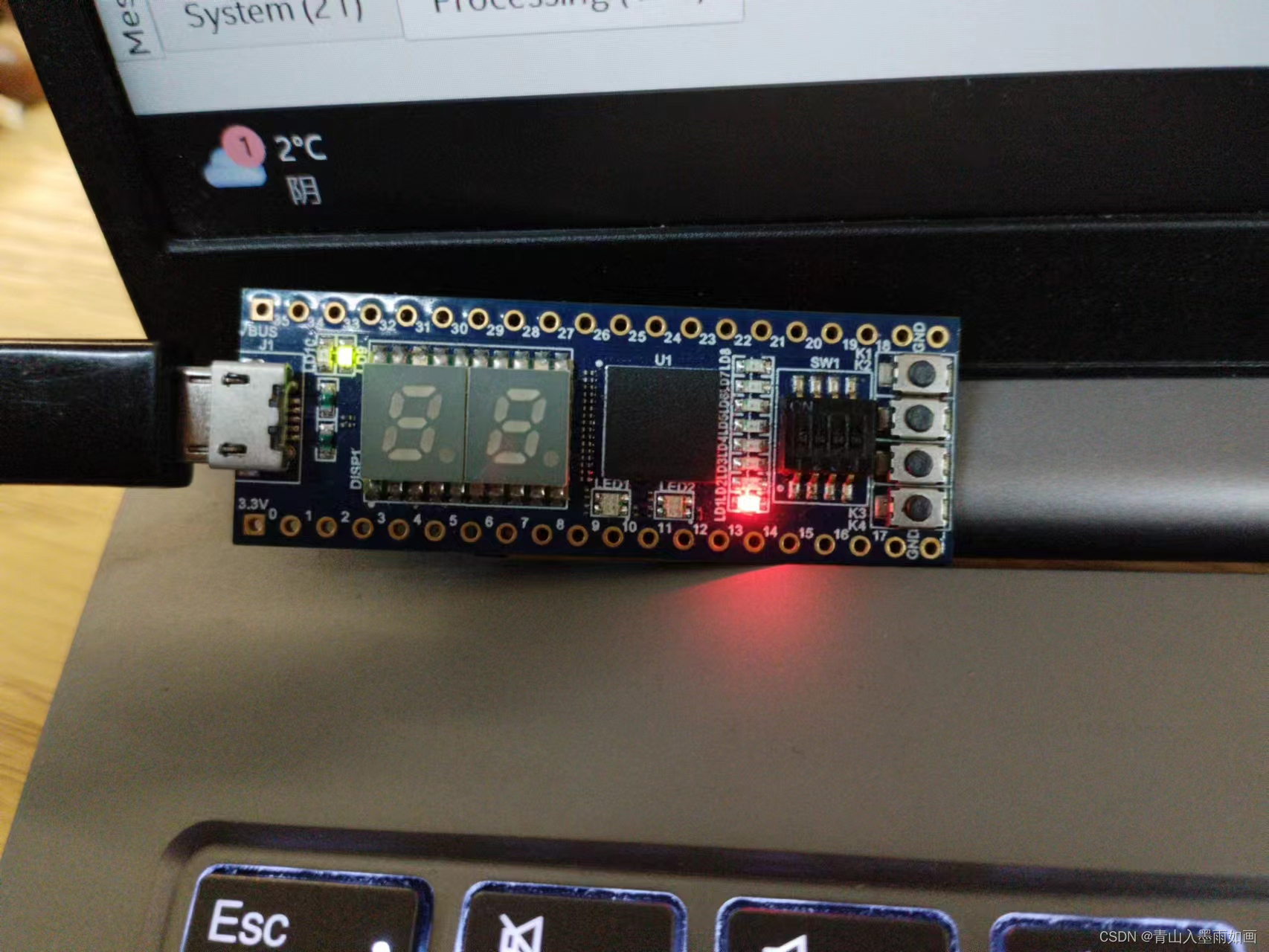

烧录过后,第一个且仅第一个LED灯亮。

将第一个拨码开关调至ON,LED熄灭;

按K1,灯亮。

注意,K1,在开发板上有标注!!!和大脚丫一样的

2.2使用仿真验证

2.2.1仿真代码的书写

D_trigger_tb.v

`timescale 1ns/1ps

`define clk_period 10

module D_trigger_tb;reg clk;reg rst;reg d;wire q;D_trigger trigger_1

(.clk(clk),.rst(rst),.d(d),.q(q)

);initial clk=1;always@(`clk_period/2)begin clk=~clk;end

initial begin rst = 0;#100;rst = 1;#1000;rst = 0;#100;$stop;endinitialbegind=0;#120;d=1;#100;d=0;#105;d=1;#100;end

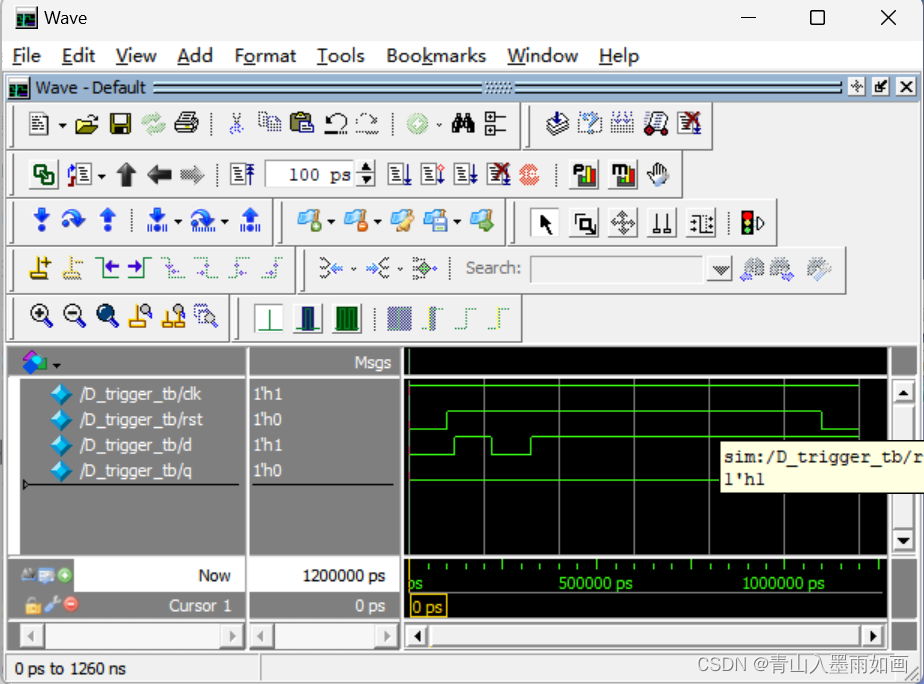

endmodule2.2.2仿真结果