DDR SDRAM 学习笔记

一、基本知识

1.SDRAM

SDRAM : 即同步动态随机存储器(Synchronous Dynamic Random Access Memory), 同步是指其时钟频率与对应控制器(CPU/FPGA)的系统时钟频率相同,并且内部命令 的发送与数据传输都是以该时钟为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机指数据的读取和写入可以随机指定地址,而不是必须按照严格的线性次序变化。

SDRAM 使用电容的电荷存储特性存储数据,而 SRAM使用CMOS晶体管存储数据,这决定了SDRAM的运行功耗要远远低于SRAM。由于使用晶体管存储数据,要能够正确的存储一位数据,需要最少6个晶体管。因此,从芯片面积上来说,单片SRAM芯片的容量不可能做到很高。

2.发展

SDRAM从发展到现在已经经历了五代,分别是:

第一代:SDR SDRAM,

第二代:DDR SDRAM,

第三代:DDR2 SDRAM,

第四代:DDR3 SDRAM,

第五代:DDR4 SDRAM。

第一代SDRAM采用单端(Single-Ended)时钟信号,第二、三、四、五代由于工作频率比较快(100MHz以上称为高频时钟),所以采用可降低干扰的差分时钟信号作为同步时钟。

差分时钟的P线与N线电平相反,而外界影响对变化沿作用等同,故外界干扰可通过两根线的处理相互抵消:如图,数据在PN的变化沿交叉处传输,由图可知时钟的高电平周期和低电平周期长度达到一致,如果不用差分时钟,则长短不一;控制信号与地址信号则只在P线的上升沿与N线的下降沿交叉处采集,从而起到触发时钟校准的作用。

SDR SDRAM的时钟频率就是数据存储的频率,第一代内存用时钟频率命名,如pc100,pc133则表明时钟信号为100或133MHz,数据读写速率也为100或133MHz。之后的第二,三,四代DDR(Double Data Rate)内存则采用数据读写速率作为命名标准,并且在前面加上表示其DDR代数的符号,PC-即DDR,PC2=DDR2,PC3=DDR3。如PC2700是DDR333,其工作频率是333/2=166MHz,2700表示带宽为2.7G。

DDR 设备: 1. 功能上实现双速率 2. 增加了差分时钟线(clk,clk_n) 3. 电压等级 SSTL_25 2.5V) 4. 增加了数据线(DQ)的随路时钟(DQS,DQS_n) 5. 速度达到400M (Mbit/s)

DDR2 设备: 1. 电压等级进一步减低( SSTL_18 ) 2. 增加了 ODT(On-Die Termination) 3. 内部 4Bit 预读结构 4. 速度最高达到 1066 (Mbit/s)

DDR3设备:内部 8Bit 预读结构

3.关键时序

时序上,看数据与时钟的对齐位置:

4.应用

为什么要用DDR这些存储器?(高速大容量)

1.大容量需求:DDR3、DDR4和DDR5的最大容量可以达到64GB、128GB和2TB。

2.高速度需求:DDR3内存传输速率可以达到800Mhz-1600MHz,带宽可以达到12.8-16GB/s,更新代的可以更高。

可用于如图像处理等应用,作为数据缓存区。

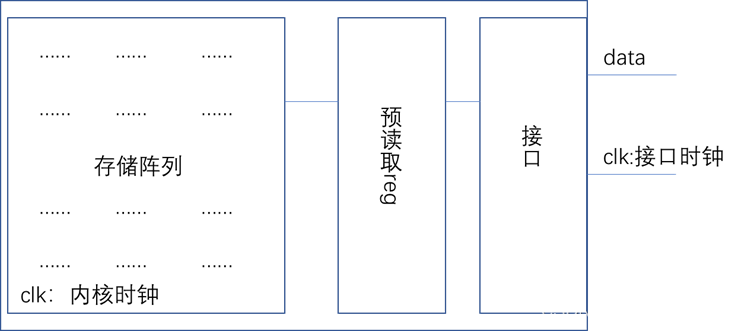

5.新概念:预读取

由于存储器内部支持的最高读取速率是固定的(即内核时钟频率),且只能在上升沿/下降沿读取数据,不能双沿读取,想要提高数据通信带宽,只能通过预读取更高位宽的数据,然后用更高频率的时钟双沿分段送出这些预读取的数据来实现。比如:存储器内部支持的内核时钟最高读取速率是200M,接口数据引脚位宽为16bit,假设每周期读取16位数据,则存储器通信带宽为:200M * 16 =3600Mbit/s ; 对于双数据速率接口,我们要求时钟双沿都读取数据,假如此时接口时钟也为200MHz,那么一个周期就要处理32位数据,所以存储器应该预读取32位数据,此时接口通信带宽为200M * 16 * 2 = 7200 Mbit/s;当我想要提高通信带宽为14400Mbit/s时,即200M * 2 * 16 * 2 = 14400Mbit/s,这时候就需要用200M时钟预读取 2 * 2 * 16= 64 bit位宽的数据,然后用400M的时钟双沿送出即可(存储器内核200MHz时钟一周期单沿读出64bit数据,400MHz接口时钟双沿传输,则刚好能在一个200MHz时钟周期内送出 2*2*16 = 64 bit)。

也就是说,用高速时钟传输低速时钟存取的数据,相当于低速时钟一次性读取出高位宽的数据放在寄存器里,然后用高速时钟分段传输。

ddr3接口时钟频率较高,如400MHz等,而FPGA内部的时钟一般100MHz、200MHz就已经很高的了;为了建立FPGA与DDR3的通信,FPGA内部专门设计了一个转换的物理层PHY,通过选择ratio,如4:1,则可以实现ddr3接口时钟用400MHz,而FPGA内部时钟用100MHz,这样一来FPGA存取数据均用的是100MHz。一般来说,这个PHY会有FIFO来缓存转换。

6.学习方法

DDR与SDR SDRAM底层时序上的区别并不大,但我们一般使用用户接口(IP核)来控制,不自己写代码,因为要作很多优化。我们只需要例化IP核,然后根据需求进行简化封装即可。一般IP核会为我们提供用户接口,可以直接使用(部分IP核可提供AXI4接口,一般用于与NISO II 软核通信)。

一般来说,学习一个复杂的IP核,最直观的学习方式就是通过其仿真模型进行仿真,观察其工作时序,抓住需要重点关注的信号观察。在这里我们需要关注用户接口信号。