Xilinx DDR3 MIG系列——ddr3控制器的时钟架构

本节目录

一、ddr3控制器的时钟架构

1、PLL输入时钟——系统时钟system_clk

2、PLL输出时钟——sync_pulse、mem_refclk、freq_refclk、MMCM1的输入时钟

3、MMCM1的输入时钟和输出时钟

4、MMCM2的输入时钟和输出时钟

一、ddr3控制器的时钟架构

对于FPGA开发来说,调用IP或者移植功能模块时,首先了解的模块的时钟架构。

如何设计时钟架构至关重要,其次对于一些优秀的设计思路可以借鉴参考。

根据ug586_7Series_MIS,我们可以了解下大体上所有的时钟架构,手册提供了具体的时钟设计方式。之后,会对每个时钟进行分析,用于了解对应时钟的功能,以及用途。

从时钟图中可以看出来,PHY设计使用了一个PLL和两个MMCM(其中对应的MMCM1,需要与PLL在同一个Bank,用于补偿插入延迟)。

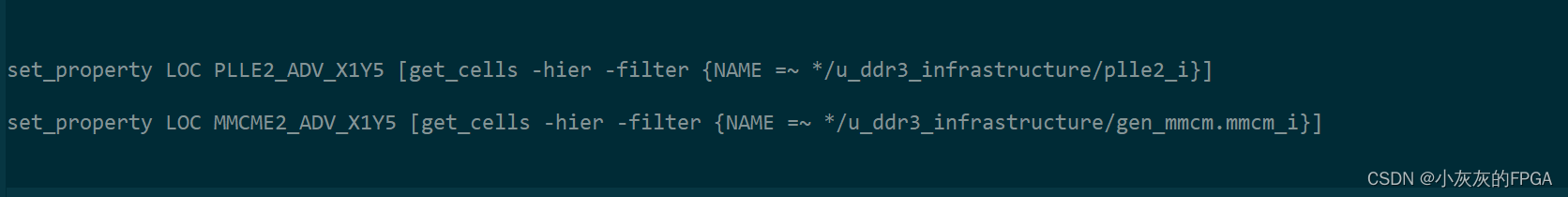

通过位置约束将PLL与MMCM1固定在同一个Bank,此种方法可用于解决时序优化,通过固定位置约束,通过布线保证两路时钟shew几乎一致。

通过位置约束将PLL与MMCM1固定在同一个Bank,此种方法可用于解决时序优化,通过固定位置约束,通过布线保证两路时钟shew几乎一致。