FPGA解析串口协议帧3.0版本,增加了错误重发功能,提供仿真文件以及源码

FPGA解析串口协议帧已经发布2个版本了,分别如下:

版本1:点击查看版本1

版本1详细介绍了串口协议帧的帧组成和设计思想,但设计粗糙,注释不详细;

版本1:点击查看版本2

版本2优化了代码,添加了详细注释;

目前根据用户的反馈,前两个版本都存在一下问题:

1、代码虽然精简,但对新手来说理解比较困难,看不懂,特别是解析模块,建议解析模块使用三段式状态机实现;

2、功能有bug,必须完全按照协议帧发送串口数据,发送错误则FPGA无法解析下一帧串口数据了,必须断电重启或重新烧录才能再次解析;

针对用户的反馈,升级了3.0版本;

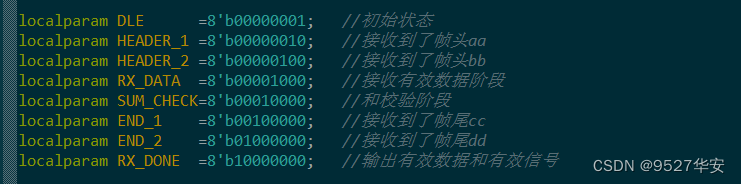

三段式状态机实现,定义了8个状态,每个状态的跳转只有1位数据变化,增强了状态机在组合逻辑和时序逻辑交替工作下的稳定性,这种写法目前在业界已经算是天花板水平了;

各状态跳转图如下:

状态切换说明如下:

DLE初始状态下,收到aa后进入状态HEADER_1; HEADER_1初始状态下,收到bb后进入状态HEADER_2;

HEADER_2初始状态下,接收数据计数器=2后进入状态RX_DATA;

RX_DATA初始状态下,接收数据计数器=7后进入状态SUM_CHECK;

SUM_CHECK初始状态下,和校验指示信号为高后进入状态END_1; END_1初始状态下,收到cc后进入状态END_2;

END_2初始状态下,收到dd后进入状态RX_DONE; RX_DONE状态自动返回DLE状态再次进入循环;

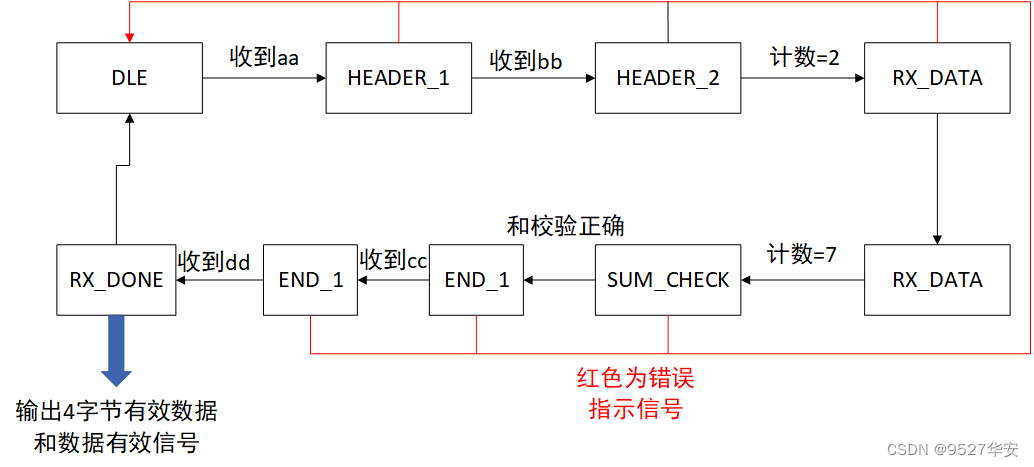

组合逻辑状态切换部分代码如下:

这一步就解决了用户反馈的理解比较困难,看不懂的问题;

错误重发功能功能:

之前的版本确实有这样的问题:

比如发送aa bb 00 00 00 00 01 cc dd的错误帧,再发aa bb 00 00 00 00 00 cc dd的正确帧,FPGA就不能解析了;FPGA直接卡在了某一状态,一直在等满足他跳转的条件,当再次发送串口数据帧时,解析模块还未切换回初始状态,所以卡死;

这里增加了error信号,一旦发送的数据帧单个字节错误,也就是说一帧数据中的某一个字节不符合协议规定,则状态机立即跳转回 DLE初始状态,这样就解决卡死问题,可以错误重发;

关于错误检测信号error部分的代码请联系我获得;

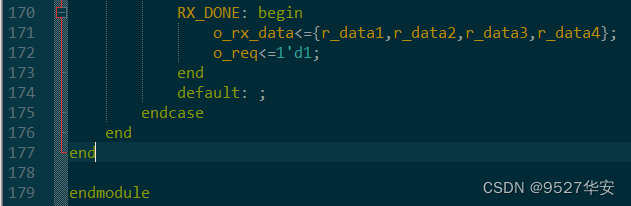

整个解析代码加上注释一共才179行,可谓短小精悍了:

仿真:

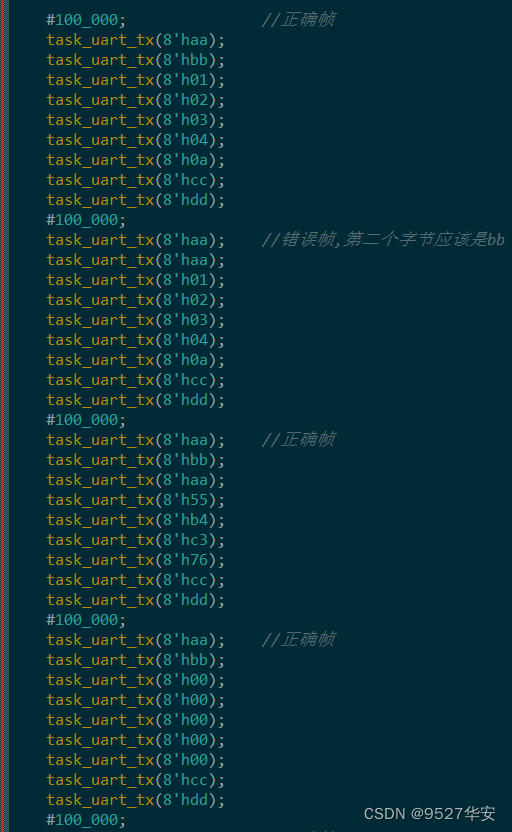

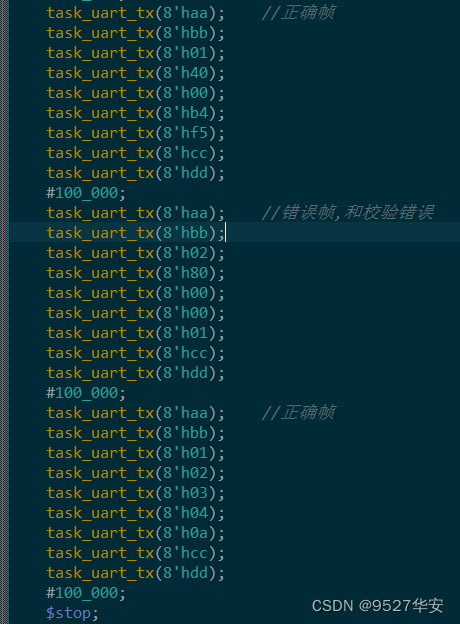

连续发送如下7帧数据:

其中有2帧是错误数据;

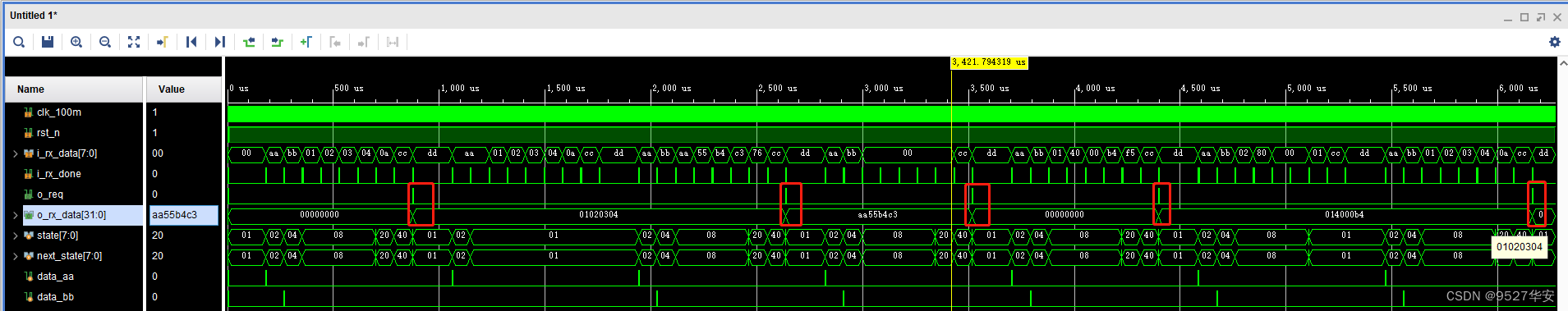

仿真结果如下:

可以看到,即使中间有2帧是错误数据,解析模块依然解析出了正确帧的有效数据,错误帧不解析也不输出;

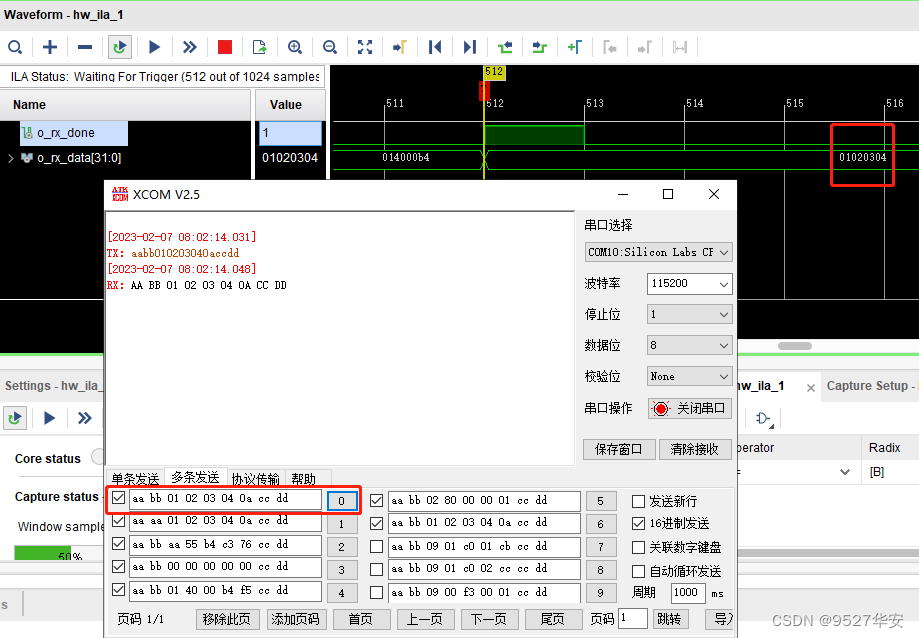

上板调试:

开发板:Xilinx Artix7开发板;

开发环境:vivado2019.1;

输入:串口;

输出:串口;

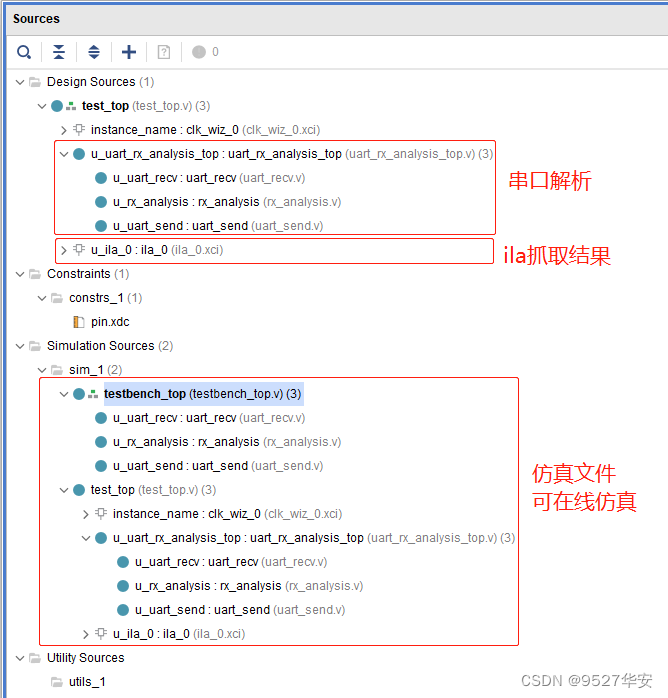

工程代码架构如下:

上板调试:

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:文章末尾的V名片。

网盘资料如下: