「Verilog学习笔记」异步复位的串联T触发器

专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

分析

这道题目里我们有两个需要明确的点:

1. 什么是异步复位

2. 什么是串联的T触发器

关于第一个点,可以看我的这篇文章,已经整理好了:

「数字集成电路笔记」异步复位和同步复位的区别-CSDN博客

那么什么是串联的T触发器?

顾名思义,串联的T触发器就是两个T触发器相串联,第一个T触发器的输出会作为第二个T触发器的输入,对于一个T触发器,它的定义为:如果在时钟上升沿时刻,data为高电平,则输出为当前值的反转,即当前值为0,则会反转为1,反之则反转为0。从波形图我们可以看出最开始的当前值为0,rst一直为高电平,因此不会使T触发器复位。注意观察第65ns的波形图,此时处于时钟上升沿且data为高电平,此时第一个T触发器将输出q1从当前值为0翻转为1。在第75ns时,由于又到了时钟上升沿,此时q1作为第二个T触发器的输入,为高电平,因此第二个T触发器会翻转,因此输出q为1。同时,q1也需要翻转,因为data依然是高电平,因此q1此时变为0。

`timescale 1ns/1ns

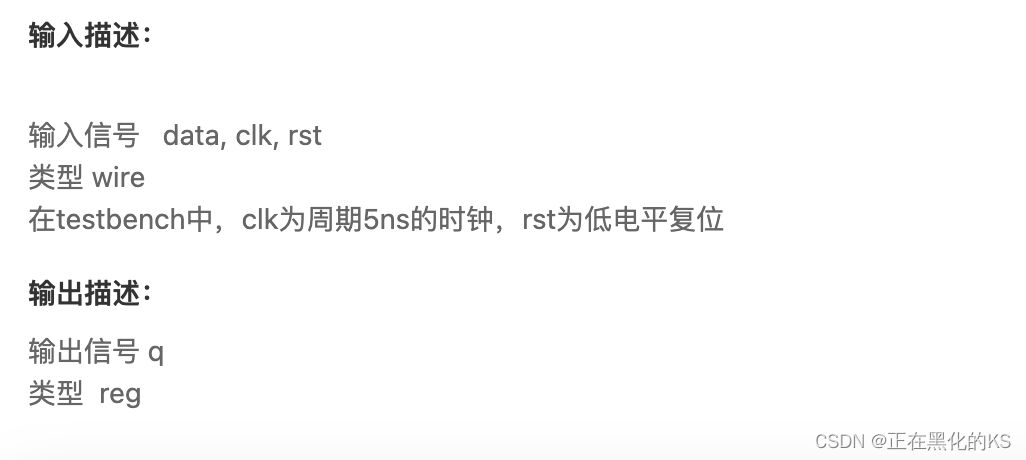

module Tff_2 (

input wire data, clk, rst,

output reg q

);

//*************code***********//reg q1 ; always @ (posedge clk or negedge rst)if (~rst) begin q1 <= 1'b0 ; q <= 1'b0 ; end else begin if (data) begin q1 <= !q1 ; // q1翻转为1之后,下面的if语句不会立刻执行,因为是非阻塞赋值方式end // 即本次always语句结束后才会对q1进行赋值if (q1) begin // 因此在进行这个if语句判断时,不应考虑上面if对q1的影响q <= !q ; end end //*************code***********//

endmodule