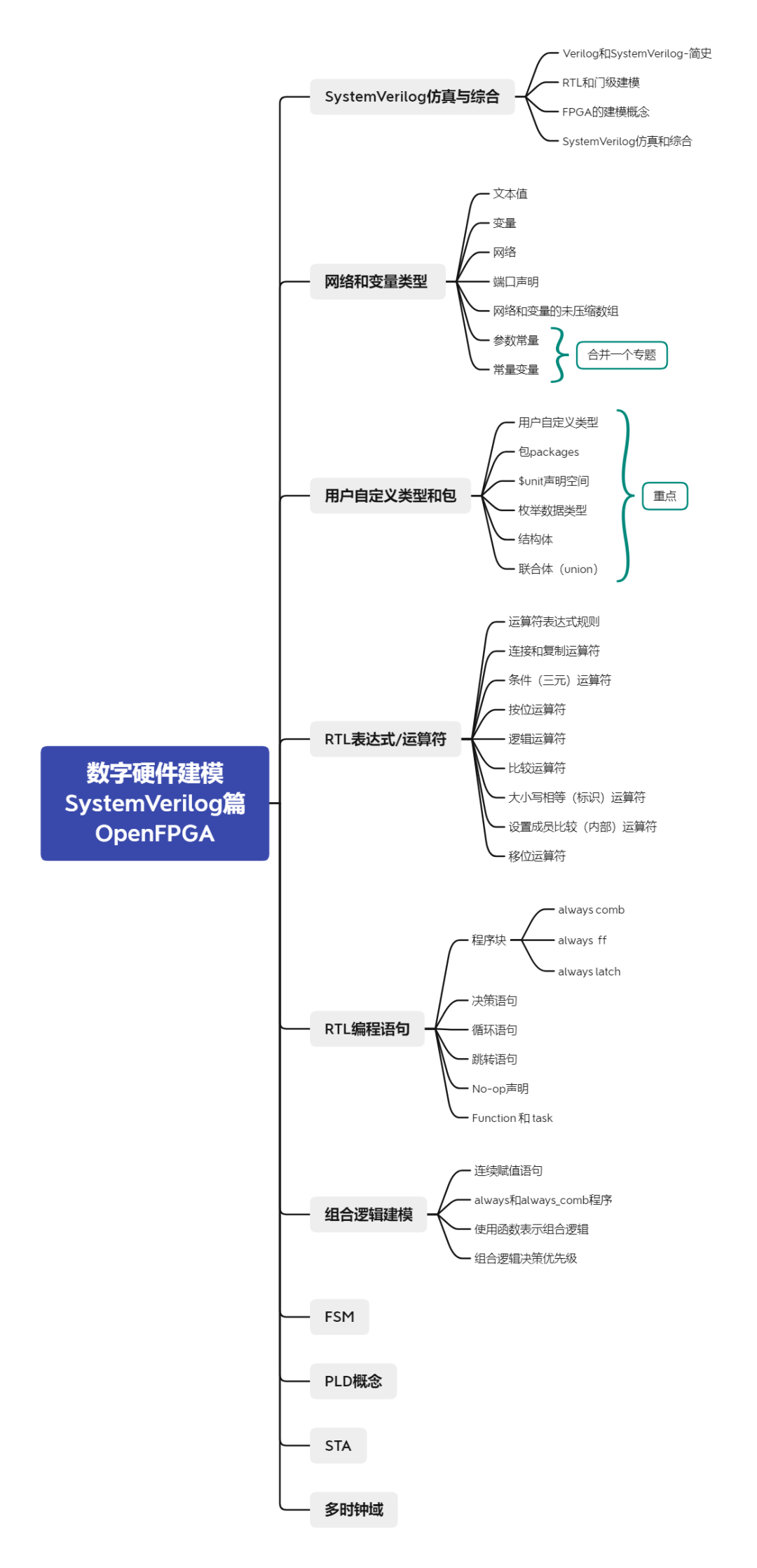

SystemVerilog-时序逻辑建模(5)多个时钟和时钟域交叉

数字硬件建模SystemVerilog-时序逻辑建模(5)多个时钟和时钟域交叉

数字门级电路可分为两大类:组合逻辑和时序逻辑。锁存器是组合逻辑和时序逻辑的一个交叉点,在后面会作为单独的主题处理。

组合逻辑描述了门级电路,其中逻辑块的输出直接反映到该块的输入值的组合,例如,双输入AND门的输出是两个输入的逻辑与。如果输入值发生变化,输出值将反映这一变化,组合逻辑的RTL模型需要反映这种门级行为,这意味着逻辑块的输出必须始终反映该逻辑块当前输入值的组合。

SystemVerilog有三种在可综合RTL级别表示组合逻辑的方法:连续赋值语句、always程序块和函数。接下来几篇文章将探讨每种编码风格,并推荐最佳实践编码风格。

多个时钟和时钟域交叉(CDC)

一个设计使用一个以上的时钟是很常见的,设计的某些部分以比其他部分更快的时钟速度运行。当作为在一个时钟上触发的寄存器的输出的数据或控制信号被存储在不同时钟上触发的寄存器中时,就会发生时钟域交叉(CDC)。

| 最佳实践指南8-8 |

|---|

| 多时钟设计应该被划分为多个模块,以便每个模块只使用一个时钟。 |

当一个模块中的所有时序逻辑都使用相同的时钟时,综合编译器、时序分析器和时钟域交叉(CDC)分析工具会更加有效。

当数据从一个时钟域移动到另一个时钟域时,必须注意避免偏移性问题。当一个触发器的数据输入在离时钟触发器太近的地方发生变化时,就会出现偏移性的情况。触发器的建立时间是在时钟之前输入必须稳定的时间量。保持时间是时钟边沿之后输入必须保持稳定的时间。

建立和保持违规最可能发生在跨时钟域的信号上,因为数据从一个模块的输出传输到另一个使用不同时钟的模块的输入。在多时钟设计中,这些模块可能是,而且经常是,以不同的频率运行。存在这样一种风险,即源于不同时钟域的模块的输入可能与当前模块的时钟域的时钟边沿变化得太近,从而导致偏移状态。为了避免偏移的风险,需要在任何输入端口添加同步器电路,因为该输入来自于不同的时钟域。

从一个时钟域向另一个域传递数据向量的一种常见方式是使用请求和确认握手控制信号。发送数据的模块向接收模块发出一个请求,要求接收模块读取数据总线。请求信号起源于发送模块的时钟域,并有可能接近接收模块的时钟域的时钟边沿到达。为了避免偏移的风险,接收模块通过在登记传入的数据之前,通过一个时钟同步器对传入的请求进行确认。在接收模块登记了数据后,它向发送模块发出确认,发送模块将其同步到其时钟域。发送模块保持数据稳定,直到收到确认握手并同步。

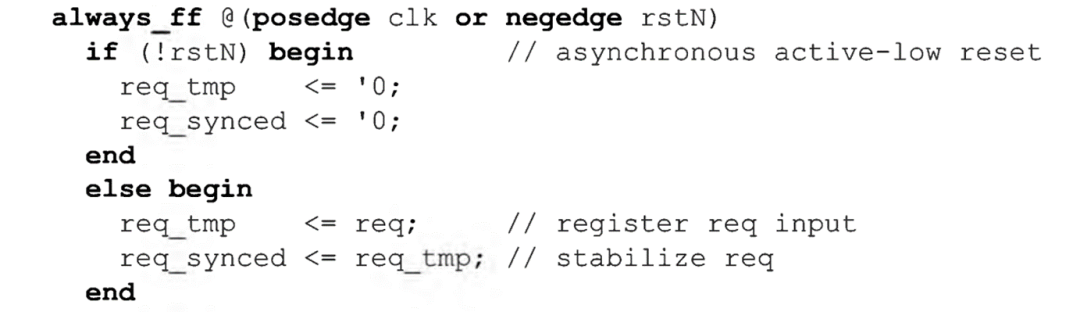

单bit CDC同步器最常使用两级移位寄存器来实现。图8-13显示了一个典型的同步器电路。

图8-13:用于单bit控制信号的两个触发器时钟同步器

图8-13:用于单bit控制信号的两个触发器时钟同步器RTL触发器的模型是零延迟的,没有建立和保持时间。在RTL模型中,即使没有CDC同步化,跨时钟域的信号也会显得始终有效。尽管如此,RTL模型应该包括在RTL模型的门级实现中需要的同步器电路。一个1位控制线同步器的例子是:

ASIC和FPGA器件在其目标库中可能有优化的时钟同步器。综合编译器将识别RTL时钟同步器的行为,并将这种行为映射到适当的目标组件(如果有)。

时钟域交叉同步器(CDC)的正确设计是一个工程课题,不在本文的讨论范围之内。