我的 System Verilog 学习记录(4)

引言

本文简单介绍 System Verilog 语言的 数据类型。

前文链接:

我的 System Verilog 学习记录(1)

我的 System Verilog 学习记录(2)

我的 System Verilog 学习记录(3)

数据类型简介

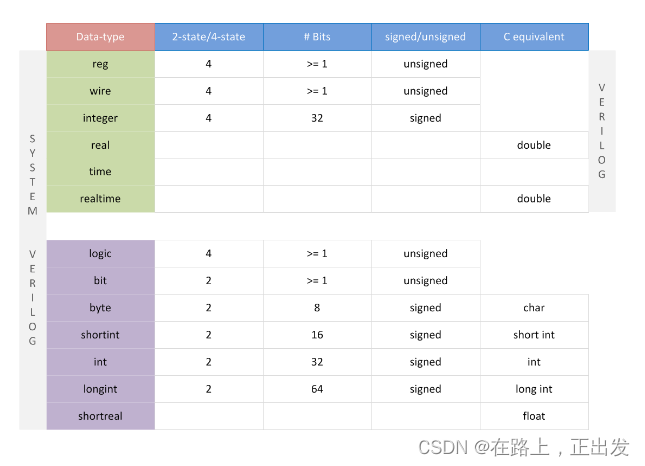

System Verilog 是 Verilog 的一个扩展,也可以用作HDL硬件描述语言。Verilog 具有reg 、wire等数据类型描述硬件行为。由于硬件验证越来越复杂,需求度越来越高,Verilog的数据类型已经不足以开发有效的testbench和testcase。因此 System Verilog 通过增加类似C语言的数据类型将Verilog扩展以实现更好的封装性和紧凑性。

下表给出了主要的数据类型:

System Verilog 的注释和Verilog相同。

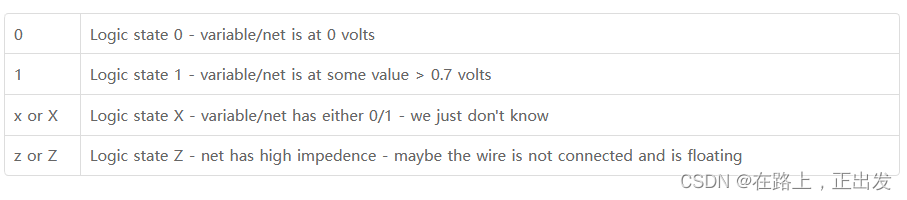

System Verilog 同样支持4态:

怎么写定点数和指数 ?

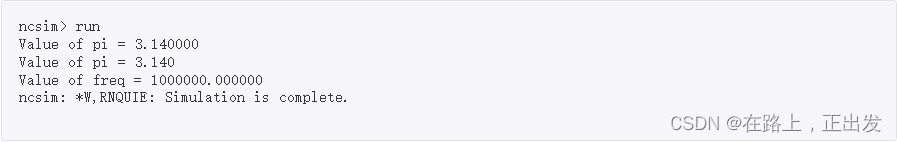

示例:

仿真log:

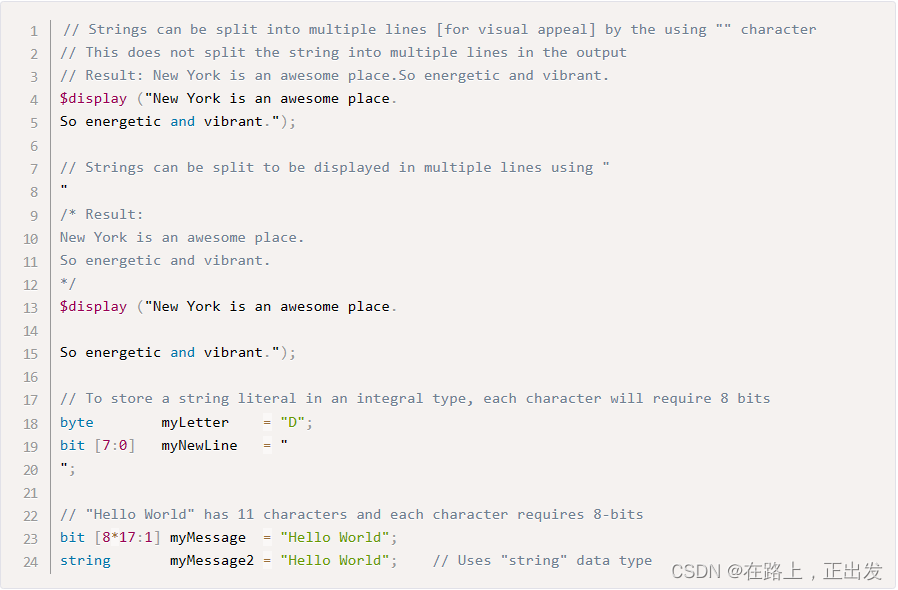

System Verilog 的字符串是啥 ?

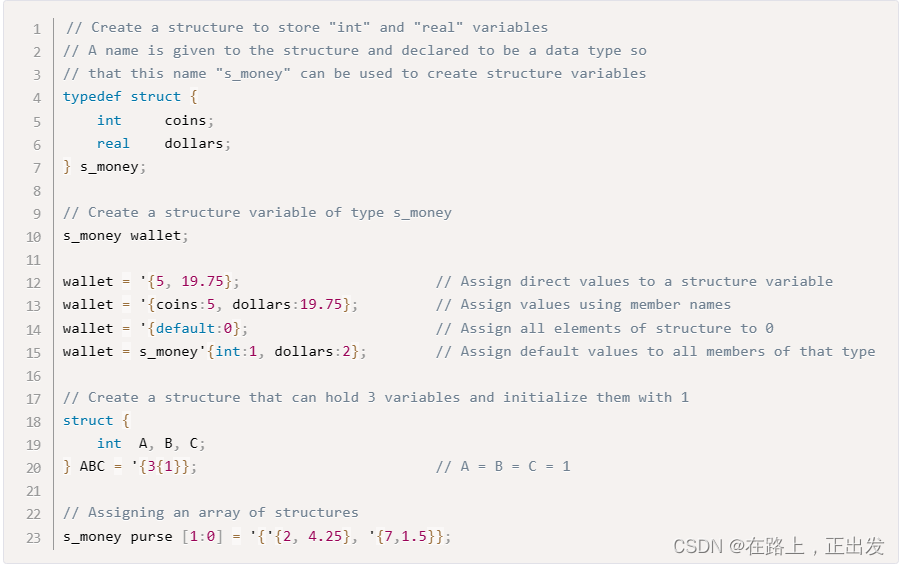

什么是结构体 ?

结构表示存储在一起并通过结构变量引用的数据类型的集合。

示例:

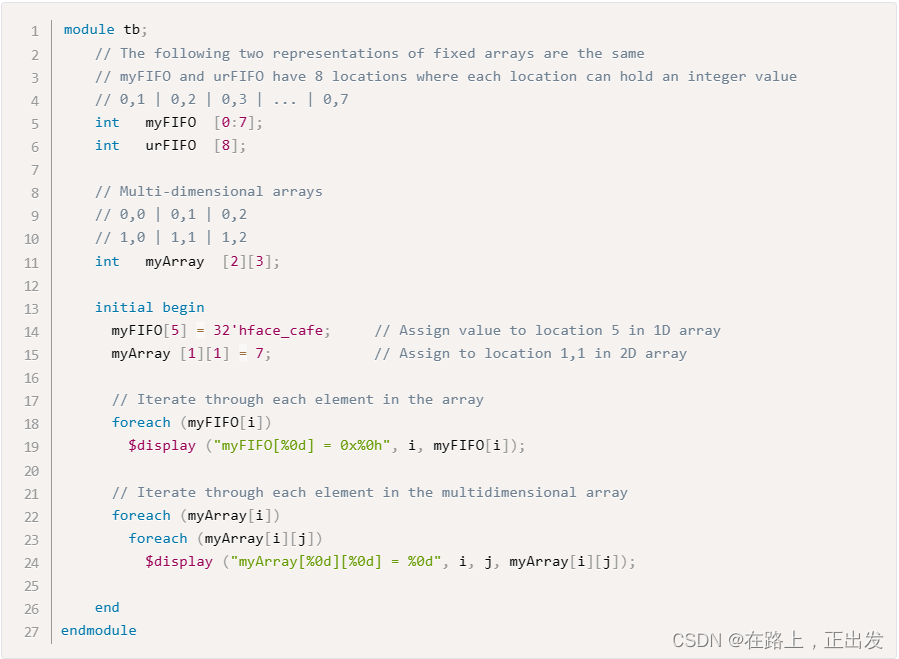

什么是固定大小的数组 ?

数组是在连续位置中存储不同值的变量。

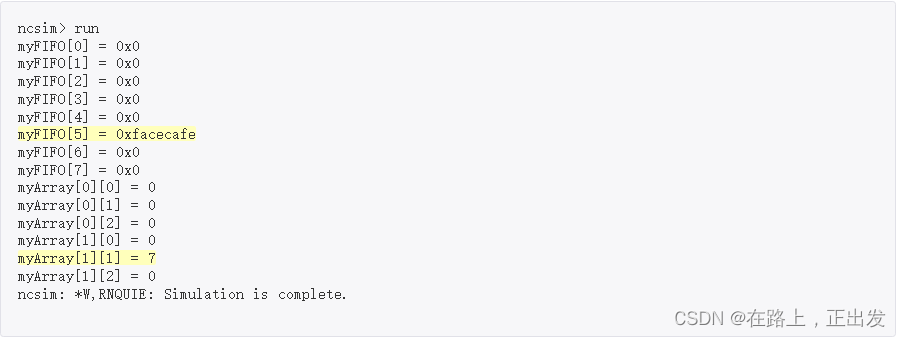

示例:

仿真log:

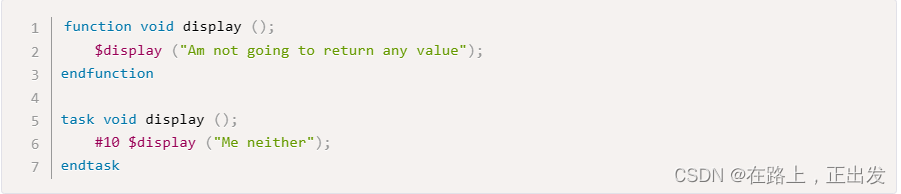

viod 数据类型

Void 数据类型表示不存在的数据,可以指定为函数和任务的返回类型,以指示没有返回值。

示例:

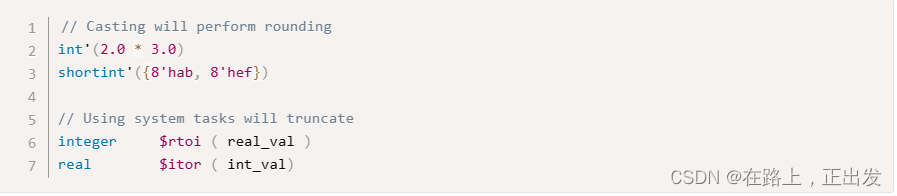

real 转 int

实数将通过将实数舍入到最近的整数而不是截断来转换为整数。如果小数部分正好为0.5,则将从零舍入。可以使用强制转换或使用系统任务指定显式转换。直接将实数值分配给整数类型也是舍入而不是截断。

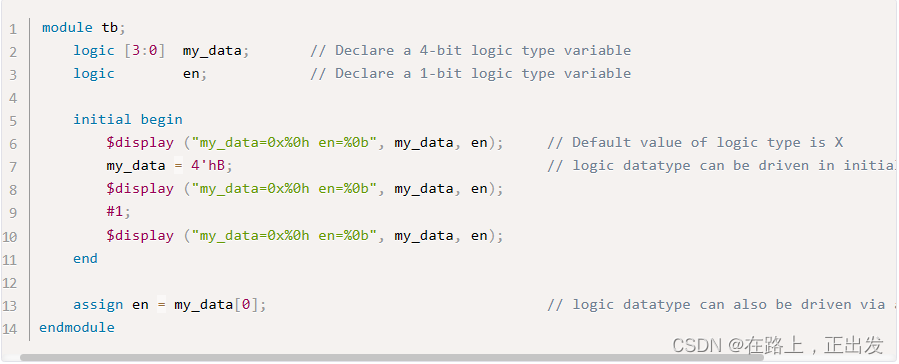

logic 和 bit

4状态数据类型

4状态指的:0、1、X、Z,这和 Verilog 一致。reg类型数据只能在程序块(如 always 、initial)中驱动,而wire数据类型只能在 assign 语句中驱动。System Verilog引入了一个新的4状态数据类型logic,其既可以在程序块内驱动也在一在连续赋值 assign 语句中驱动。但是当一个信号被多个器件驱动时,需要定义为线网类型,如wire,这样System Verilog 可以确定最终值。

logic

示例:

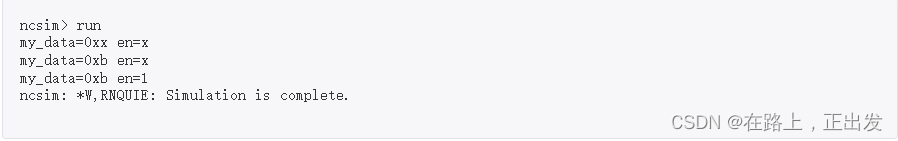

仿真log:

2状态数据类型

在典型的验证测试平台中,有许多情况下我们并不真正需要所有四个值(0,1,x,z),例如,当使用指定包长度的报头对网络包进行建模时。长度通常是一个数字,但不是X和Z。SystemVerilog添加了许多新的两状态数据类型,这些数据类型只能存储,值为0或1。这将有助于更快的仿真,占用更少的内存,并且在某些设计风格中是首选的。

当4状态值转换为2状态值时,任何未知或高阻抗位都应转换为零。

最重要的两态数据类型是bit,它是testbench中最常用的。bit类型的变量可以是0或1,表示单个比特。应该提供从MSB到LSB的范围,使其表示和存储多个比特。

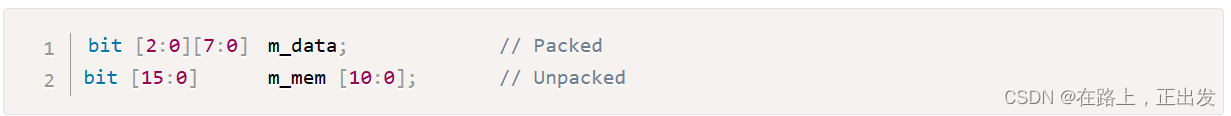

bit

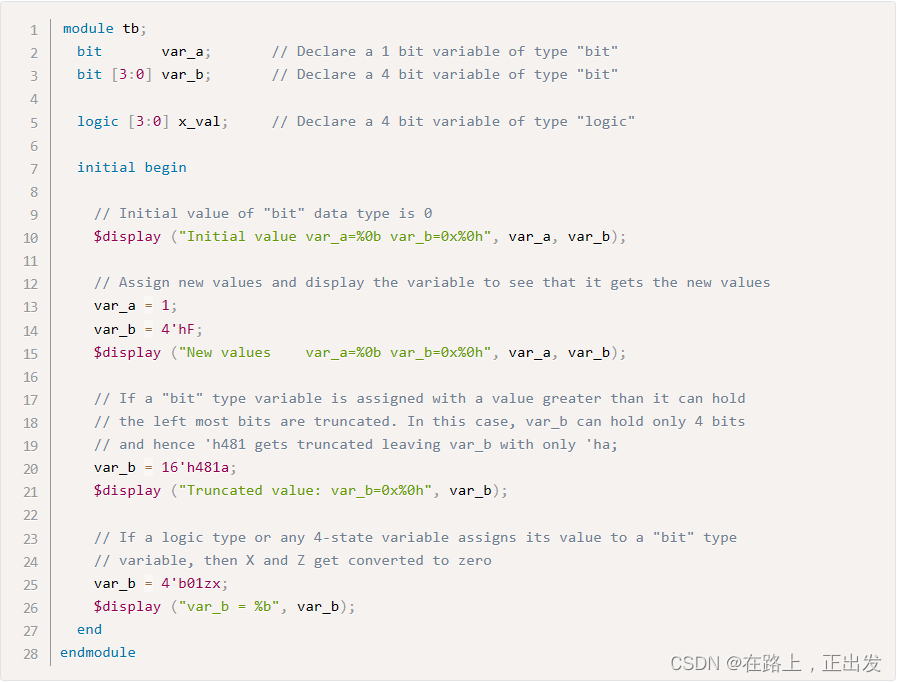

示例:

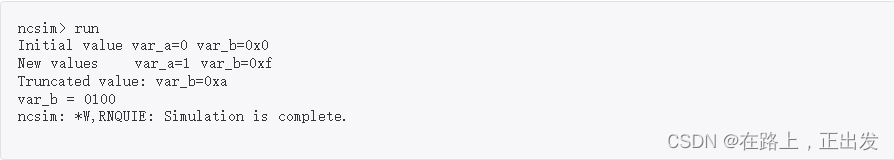

仿真log:

integer 和 byte

除了Verilog支持的所有数据类型外,SystemVerilog还具有许多其他2状态数据类型。现代测试平台中最常用的数据类型有 bit , int , logic , byte。

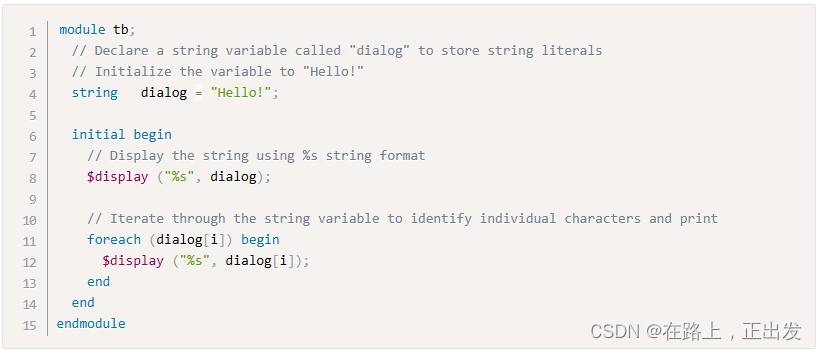

integer

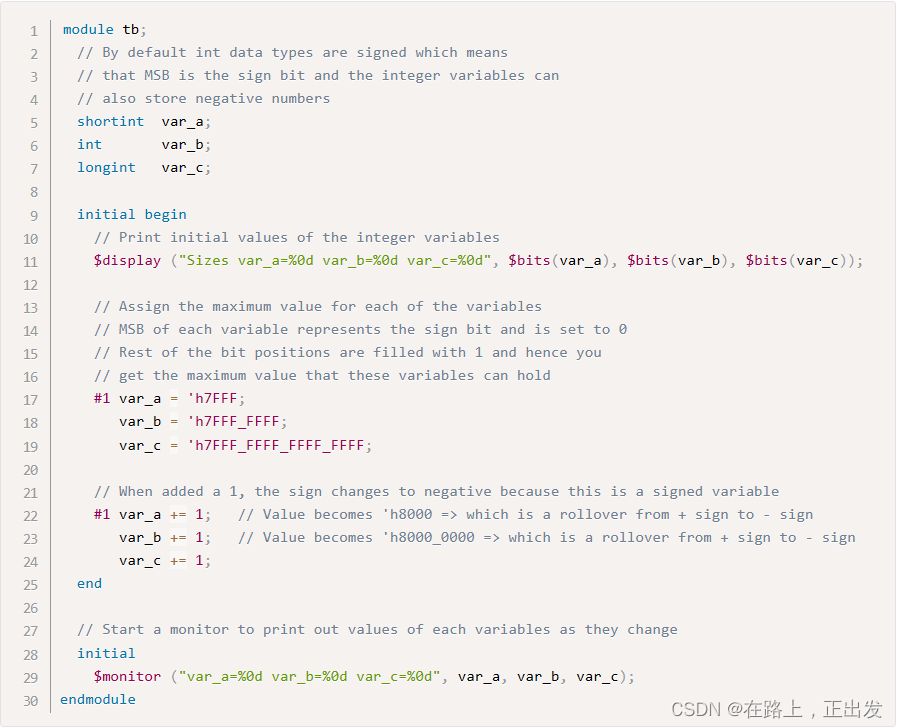

System Verilog 有3种新的有符号数据类型存放整数,每种的 size 不一样,最小的是 shortint ,范围:-32768~32767;最大的是 longint ,可以用通过关键字 signed 或者 unsigned 定义数据的符号性。当然也可以通过强制类型转换改变数据的符号性。

有符号(signed)

默认情况下,integer 变量是有符号数。

示例:

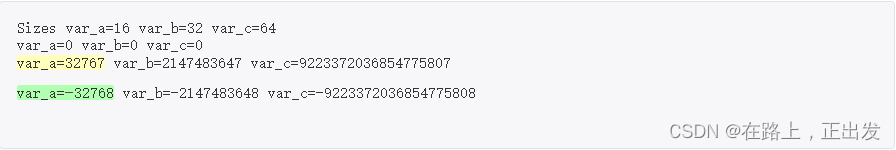

系统任务:$bits 返回变量的位宽。

仿真log:

无符号(unsigned)

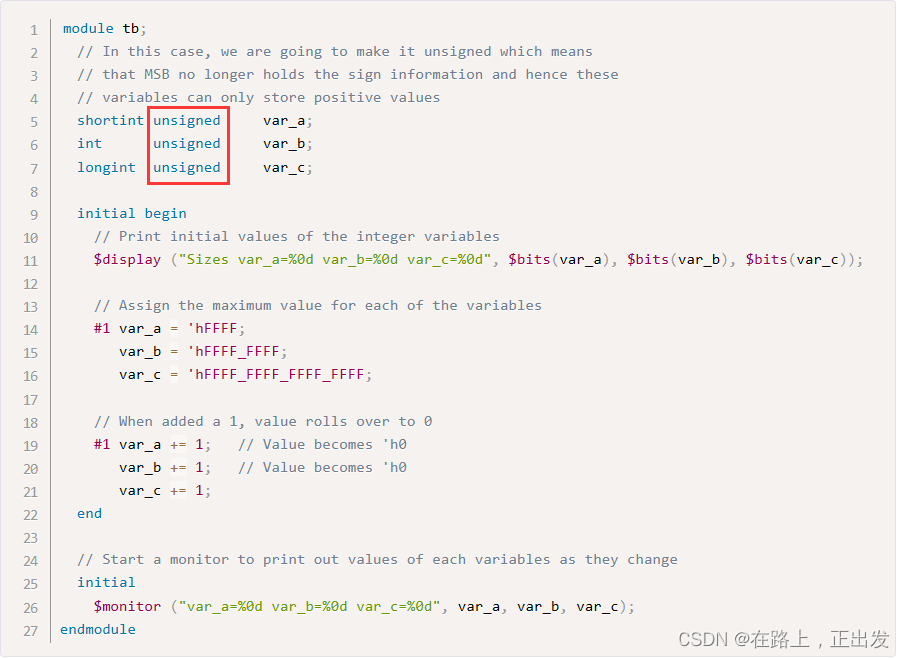

示例:

仿真log:

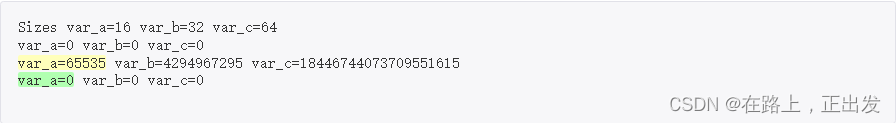

byte

字节是长度为8位的整数的更短版本。默认情况下,字节是带符号变量,并且具有与上一节中描述的整数相同的属性。

示例:

仿真log:

字符串

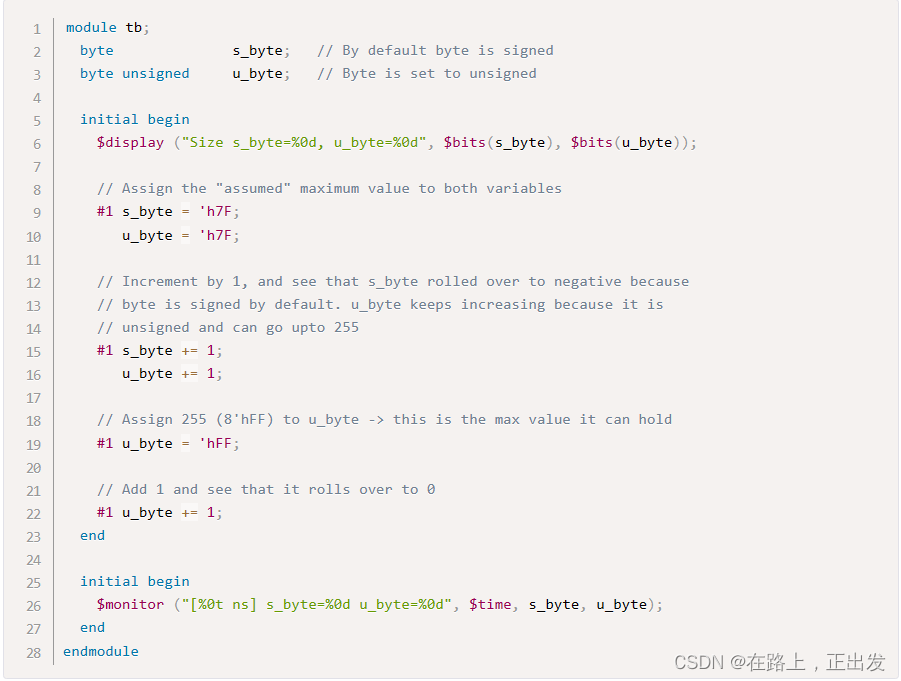

System Verilog 中的字符串是啥 ?

字符串数据类型是字符的有序集合。字符串变量的长度可以具有动态长度且在仿真过程中可变化。字符串变量表示字符串的方式与字符串文字不同。使用字符串变量时不会发生截断。

语法

string variable_name [= initial_value] ;variable_name 是有效的标识符,可选的 initial_value 可以是字符串文字、空字符串的值 " " 或字符串数据类型表达式。如果在声明时未指定初始值,则变量默认为” “空字符串文字。

举个栗子

仿真 log :

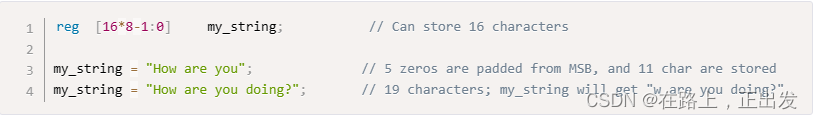

Verilog 中如何表示字符串 ?

单个ASCll字符需要8位(1字节),要存储字符串,我们需要的字节数与字符串中的字符数一样多。

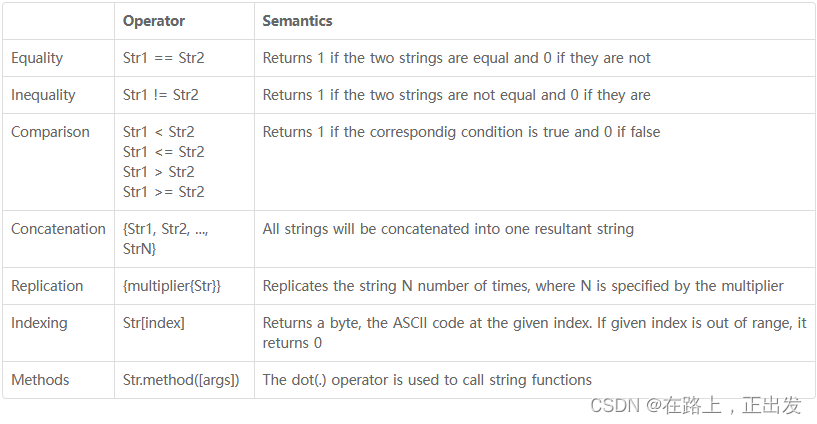

字符串操作符

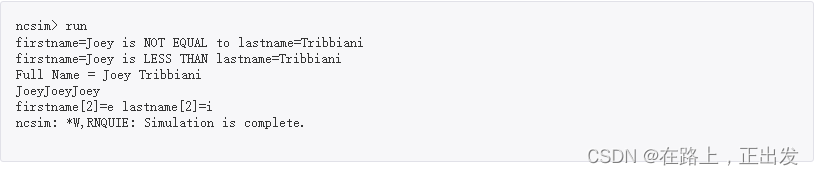

示例:

仿真 log:

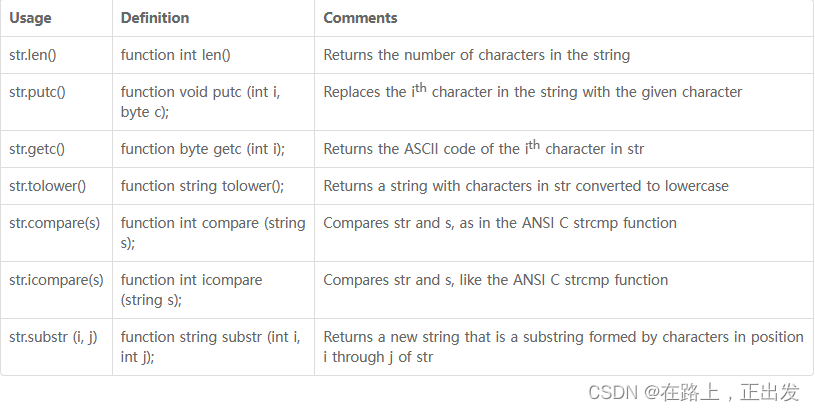

基本字符串方法

System Verilog 还包括许多使用内置方法表示法的特殊方法来处理字符串。

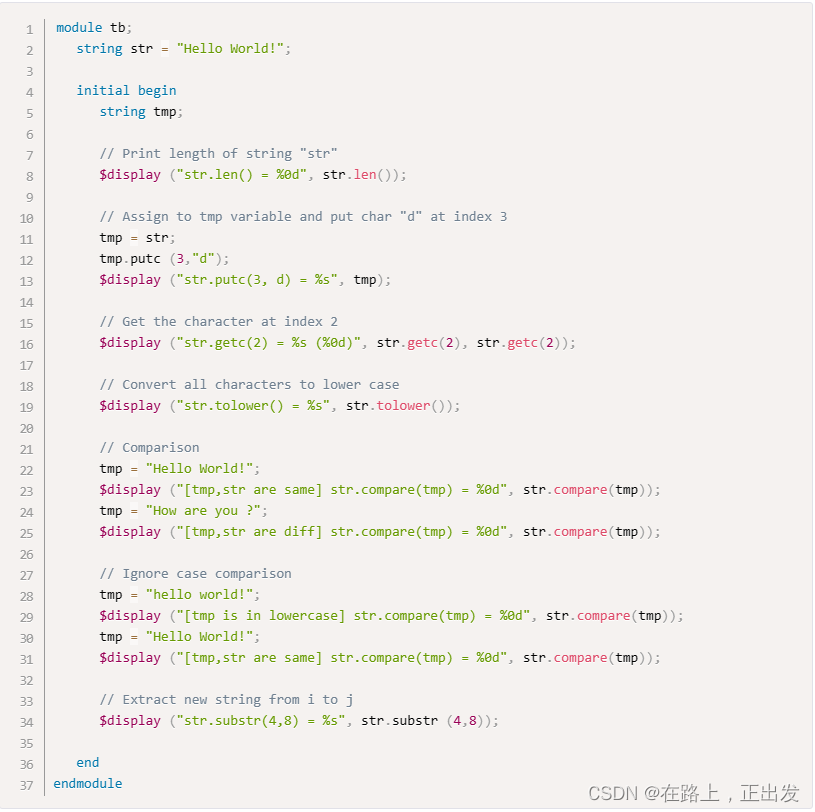

示例:

仿真 log:

字符串转换方法

枚举类型

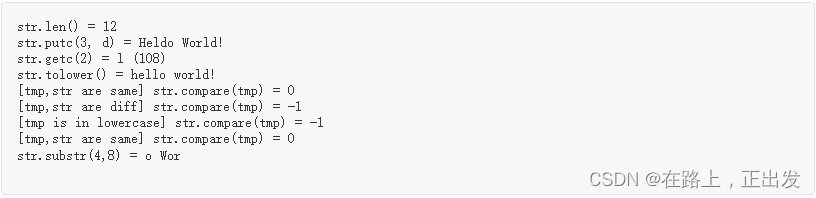

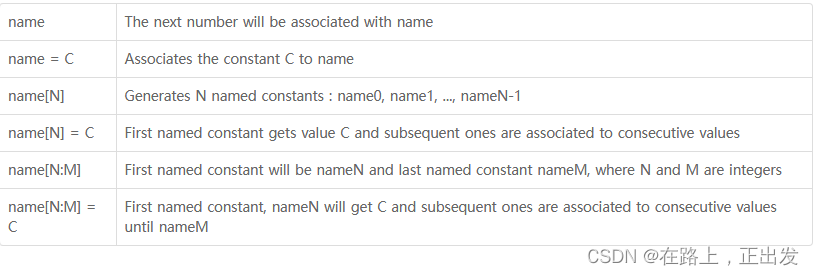

枚举类型定义了一组命名值。在下面的示例中,light_*是一个枚举变量,可以存储三个可能的值(0,1,2)之一。默认情况下,枚举列表中的第一个名称获得值0,后面的名称获得像1和2这样的增量值。

用户可以为任何枚举的名称分配任何整数值。如果任何名称没有赋值,则它会自动采用先前名称的递增后的值。

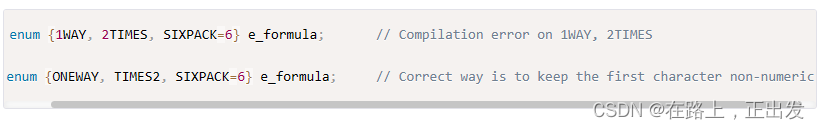

请注意,枚举名不能以数字开头 !

错误示例:

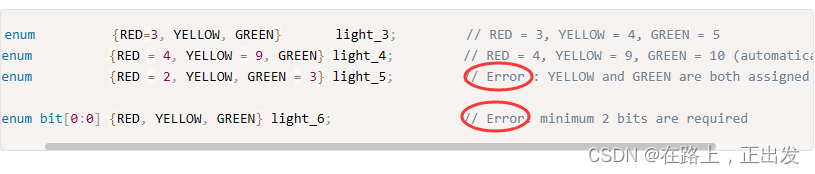

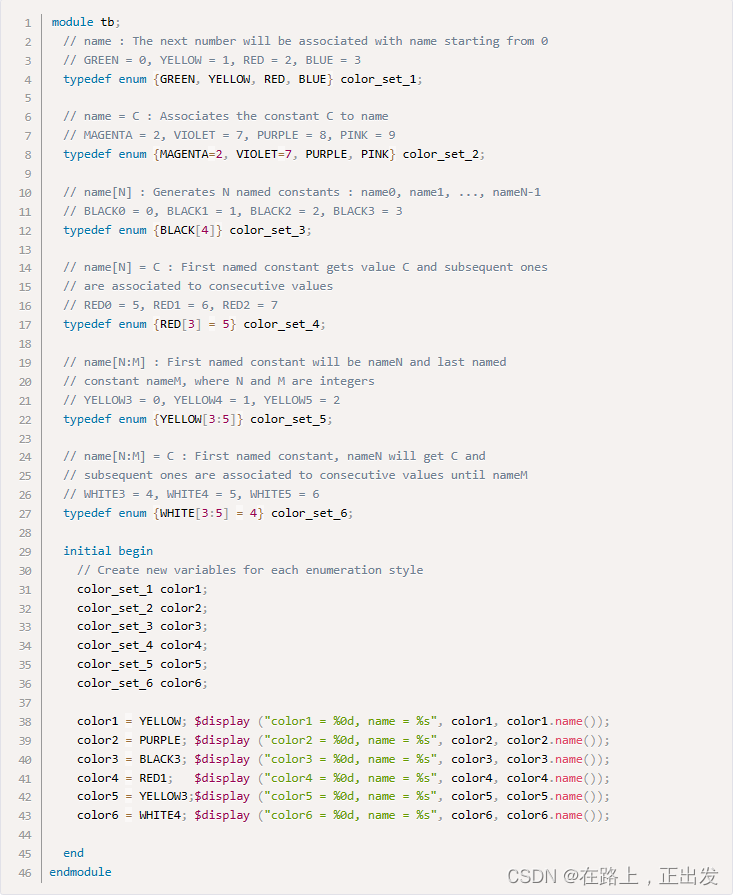

如何定义一个新的枚举类型 ?

可以创建自定义数据类型,以便可以使用相同的数据类型声明其他变量。

示例:

仿真 log:

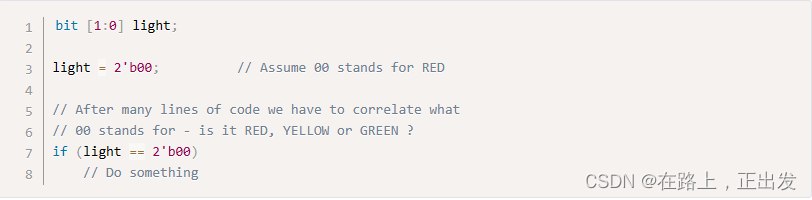

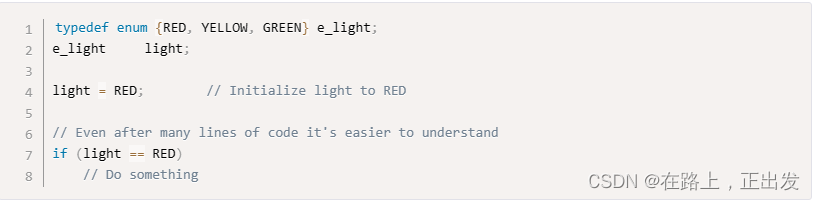

为啥需要枚举啊 ?

为了代码的低复杂度和易读性。

如下的代码没有枚举:

增加枚举更加易读:

枚举类型范围

示例:

仿真 log:

枚举类型方法

示例:

类型检查

枚举类型是强类型的,因此,除非使用显式强制转换,否则不能为枚举类型的变量赋值位于枚举集之外的整数值。

示例:

Questa Sim 运行结果:

主要是赋值的类型不匹配。应该用强制类型转换。

更改强转后,Questa Sim 运行结果:

数组

SV 通过如下的几种数组,给复杂数据结构的建立提供了很大的灵活性。

- 静态数组

- 动态数组

- 关联数组

- 队列

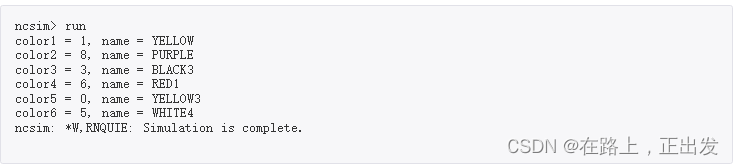

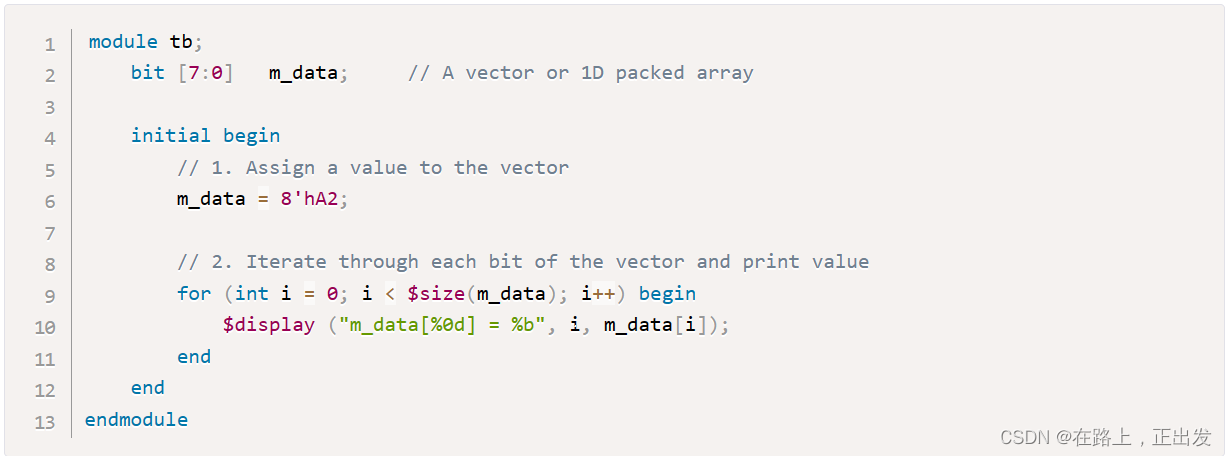

静态数组

静态数组是指其大小在编译前已知的数组。在下面的示例中,声明了一个8位宽的静态数组,为其赋值并迭代以打印其值。

静态数组进一步分为压缩数组和未压缩数组。

未压缩数组可以是固定尺寸数组、动态数组、关联数组或者队列。

动态数组

动态数组是指其大小在编译期间未知,但在运行时根据需要进行定义和扩展的数组。动态数组很容易通过其空方括号识别。

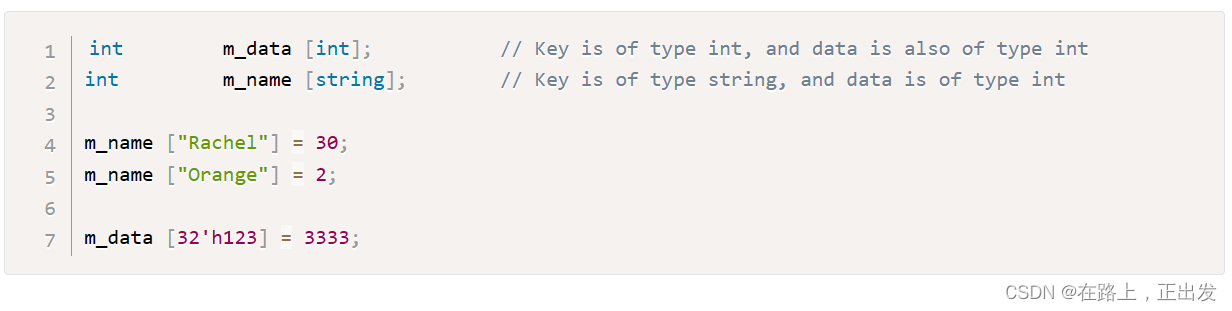

关联数组

关联数组是用某个 键 (Key)存储内容的数组。这很容易通过其方括号中存在的数据类型来识别。该键表示在方括号中。

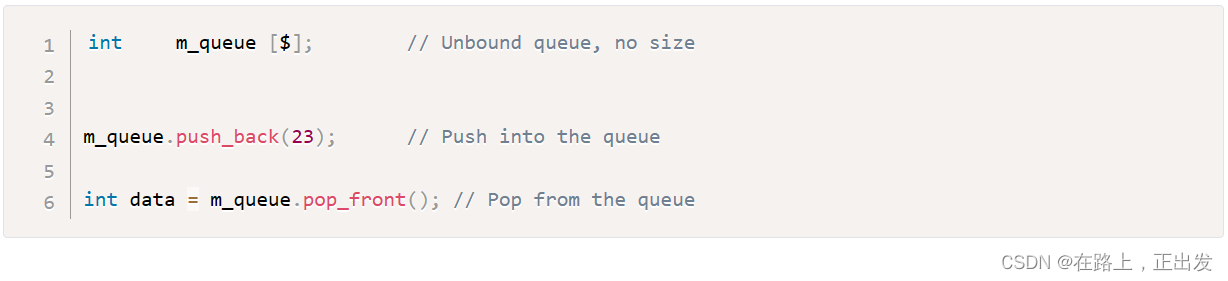

队列

队列是一种数据类型,可以将数据推入队列或从数组中弹出。它很容易通过方括号内的符号 $ 识别。

未完待续~