Matlab Simulink支持system generator插件

文章目录

- 前言

- 一、System Generator 简介

- 二、System Generator 特性

- 三、System Generator 安装

- 1、确定是否已安装 System Generator 工具

- 2、vivado 卸载

- 3、vivado 安装

- 四、解决版本不兼容问题

- 五、使用 System Generator

前言

目前有在 Simulink 中开发完成后将其转换成 Verilog 语言并将其跑在 fpga 上面的需求,因此本文简要介绍了在 matlab 的 simulink 中使用 system generator 的方法。

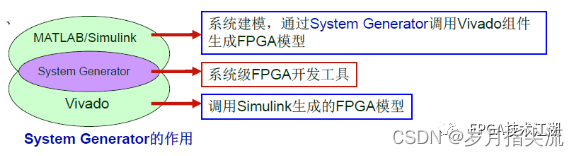

一、System Generator 简介

System Generator 是 Xilinx 公司进行数字信号处理开发的一种设计工具,它通过将 Xilinx 开发的一些模块嵌入到Simulink 的库中,可以在 Simulink 中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成 HDL 文件,或者网表,可以在 ISE 中进行调用。或者直接生成比特流下载文件。能够加快DSP 系统的开发进度。(摘自:百度百科)

二、System Generator 特性

System Generator 具有如下关键特性:

- 超过 90 种 DSP 设计模块,包括加法器、乘法器、寄存器、FFT、滤波器、存储器等等;

- 包含一个与 7 系列 UltraScale 系列 FPGA 相贴合的 FIR 编译模块,支持多种滤波器模式,可以使用 MATLAB 函数或 FDATOOL 工具生成系数;

- 包含一个 Mcode 模块,可以接入 MATLAB 代码完成简单的控制;

- 可以生成 HDL 文件、网表或 IP 核,在 vivado 中调用。

三、System Generator 安装

1、确定是否已安装 System Generator 工具

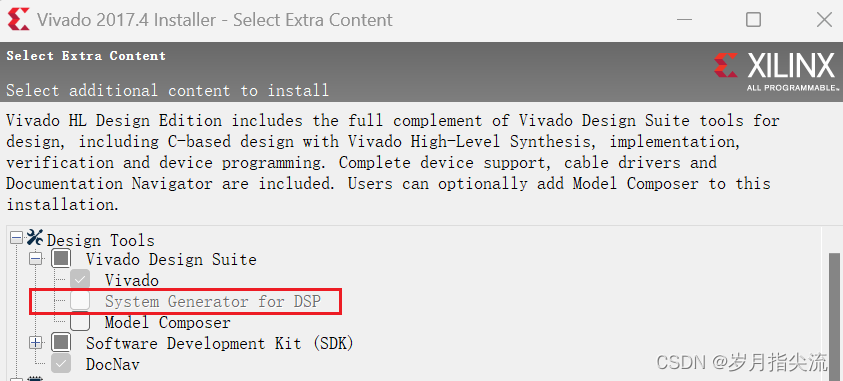

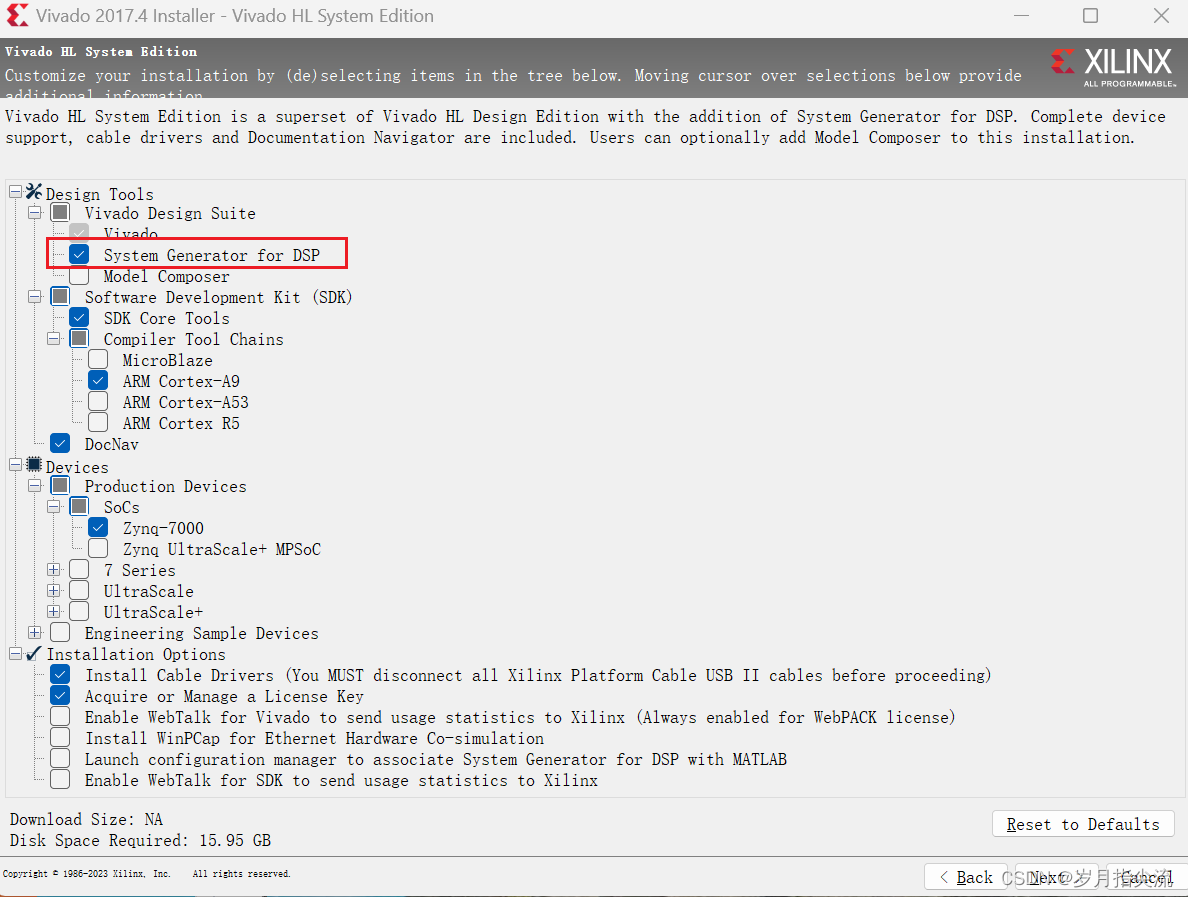

正常在我们安装 vivado 软件后就默认安装了 System Generator 了,但是我本地的 vivado 当时定制化 AC7020 核心板安装时关闭了很多安装选项,因此并没有安装 System Generator,如下图所示是灰色的,而且不支持再次重新配置。

无奈之下只能先卸载了 vivado 进行重新安装

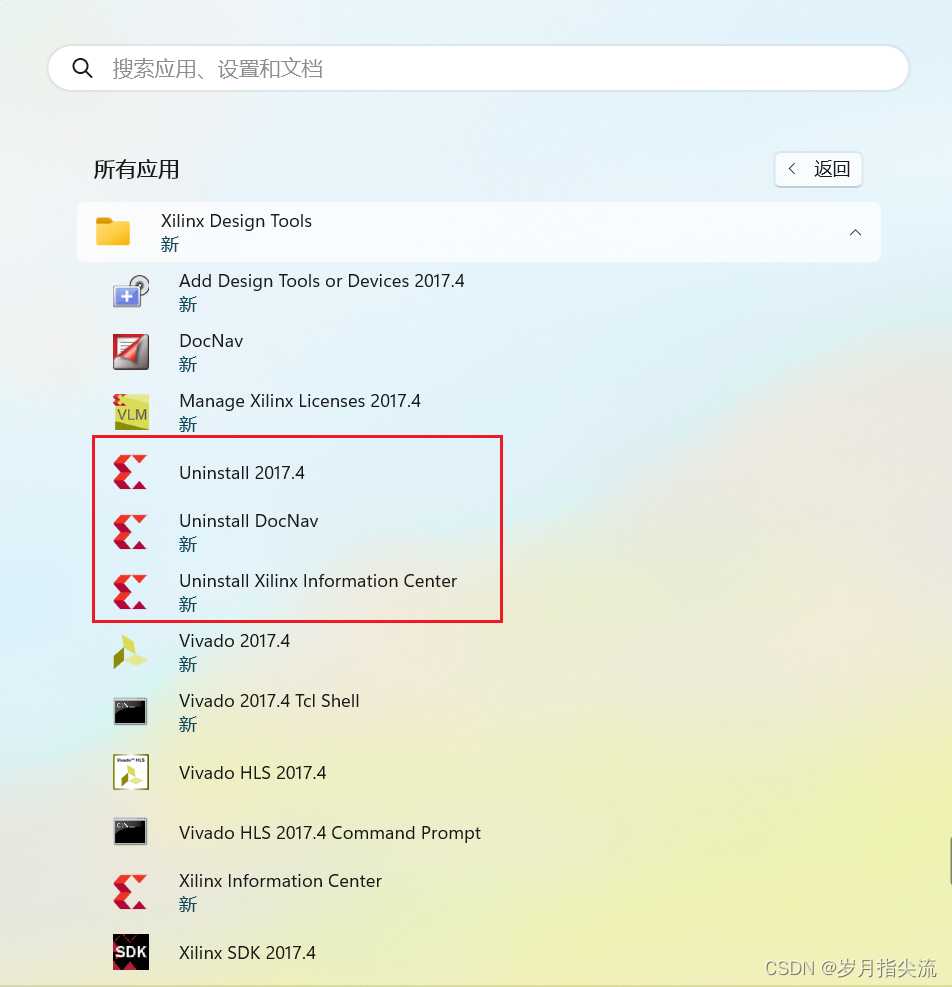

2、vivado 卸载

下图红框中的依次进行卸载

3、vivado 安装

安装步骤参考我之前的博文:Vivado 2017.04版本安装教程

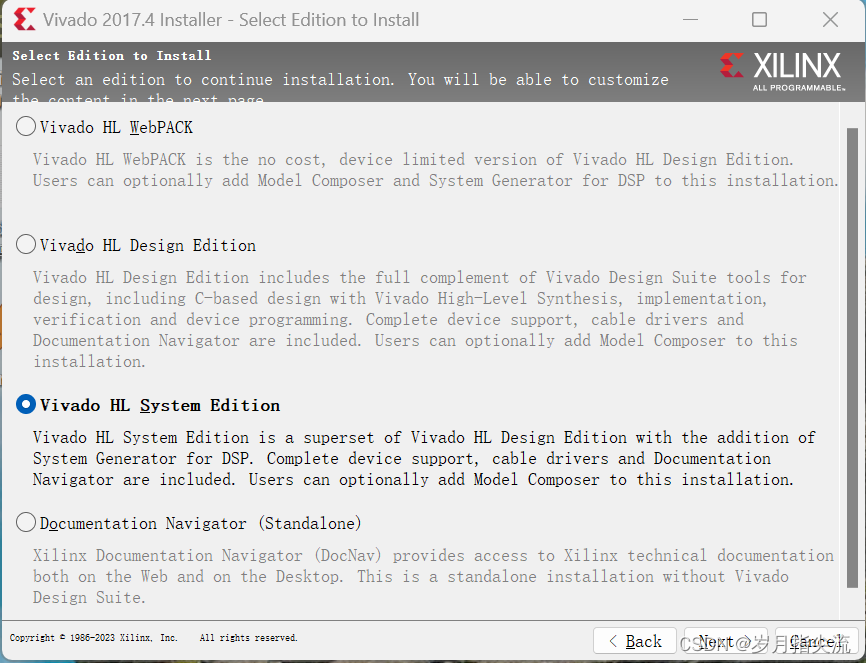

比较重要的一点是这里选择 “Vivado HL System Edition”

Vivado HL System Edition 是 Vivado HL Design Edition 的超集,增加了 DSP 的系统生成器。包括完整的设备支持、电缆驱动程序和 Documentation Navigator。用户可以选择将 Model Composer 添加到此安装中。

除了上述安装教程的配置外,记得勾选 System Generator for DSP

安装完成后,桌面多了一个 System Generator 2017.4 快捷方式

四、解决版本不兼容问题

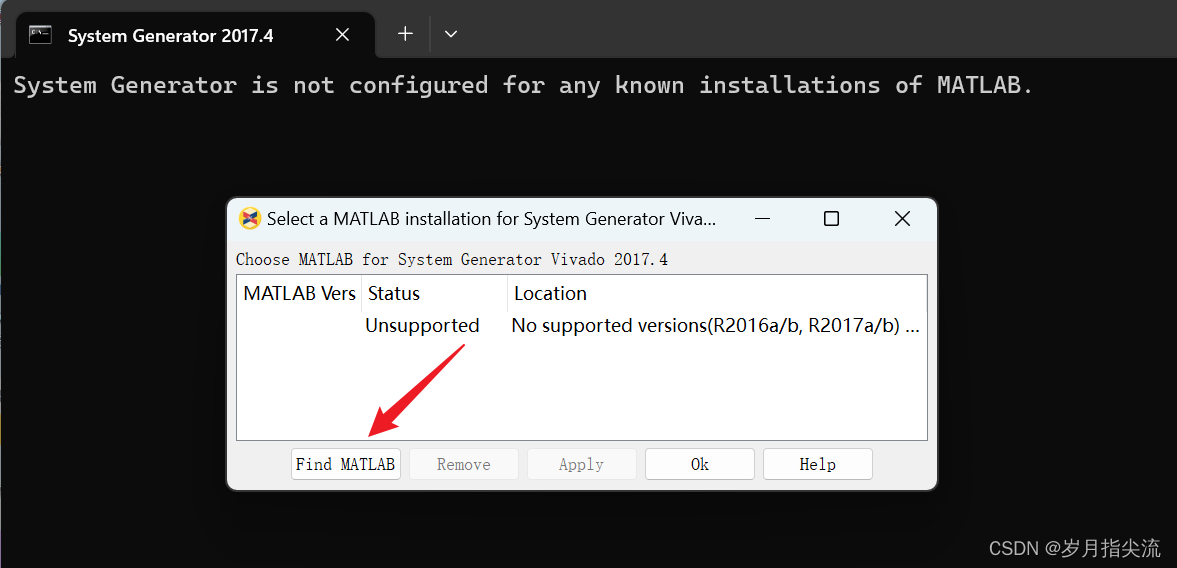

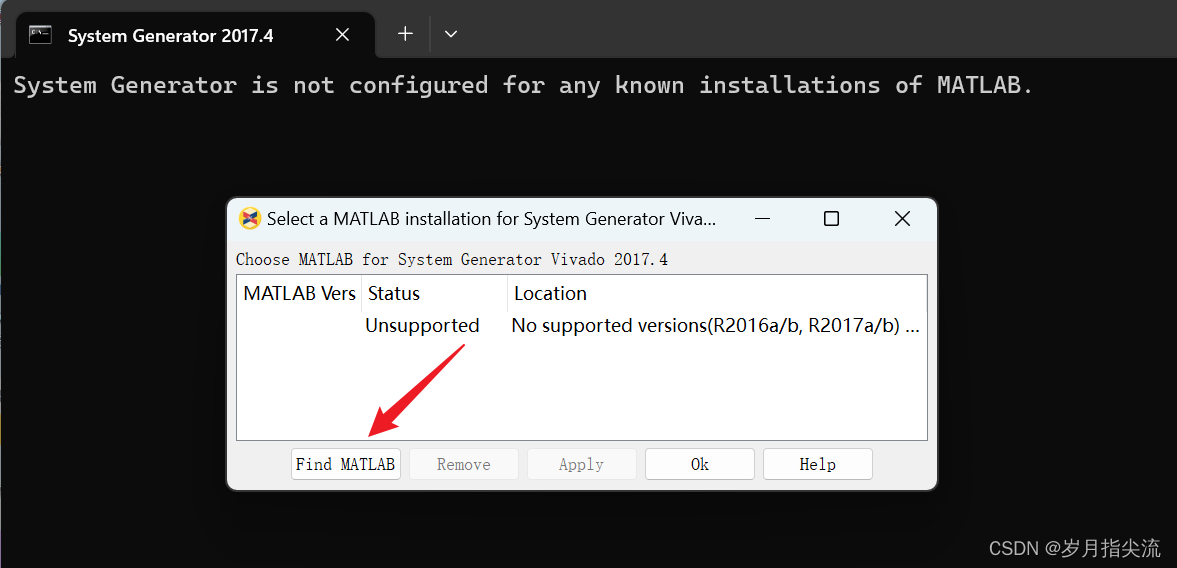

双击 System Generator 2017.4,点击 Find Matlab,选择你本地 Matlab 安装目录

会出现 Matlab Unsupported 相关报错

这个问题是版本不兼容所导致,我的 vivado 是 2017.04 版本的,我的 matlab 是 2019a 版本。具体参考赛灵思官网:https://www.xilinx.com/support/documentation-navigation/see-all-versions.html?xlnxproducttypes=Design%20Tools&xlnxdocumentid=UG973

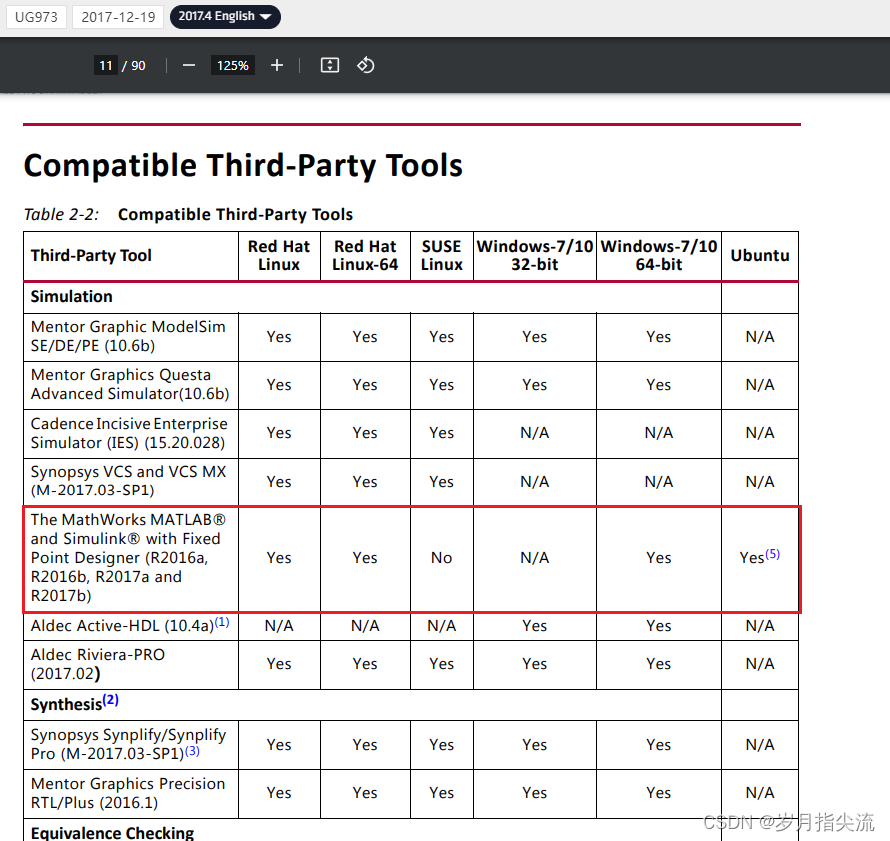

根据自己需要的 vivado 版本查看对应的手册。以 vivado2017.4 为例说明,如下图所示:

可以看到 vivado 2017.4 支持的 matlab 版本为 R2016a,R2016b,R2017a 和 R2017b

解决方法:

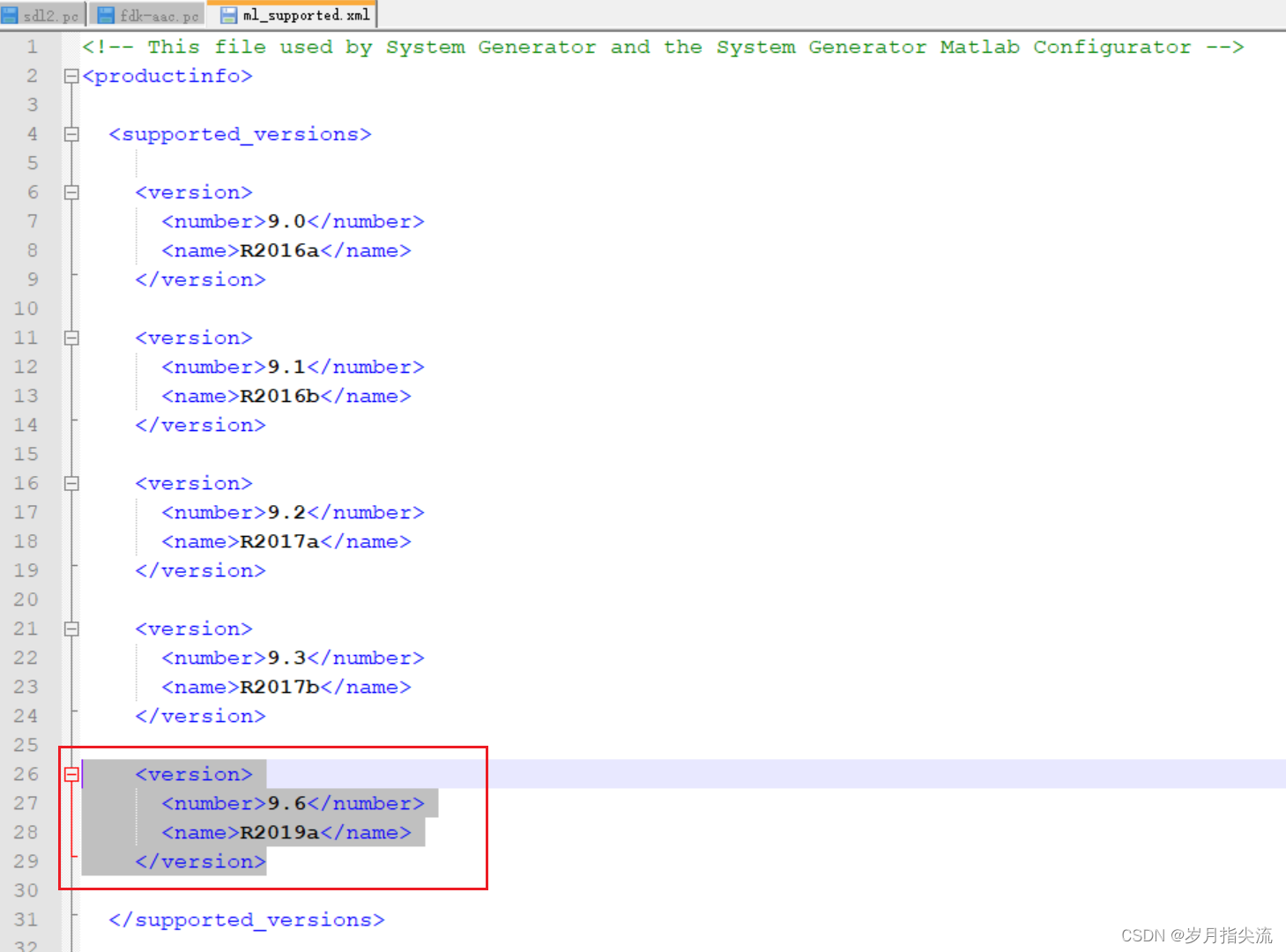

修改 ml_supported.xm 文件,添加你的 Matlab 版本就行。文件目录:D:\Vivado_2017.4\Vivado\2017.4\data\sysgen\sg_config\ml_supported.xml

新增 2019a 版本

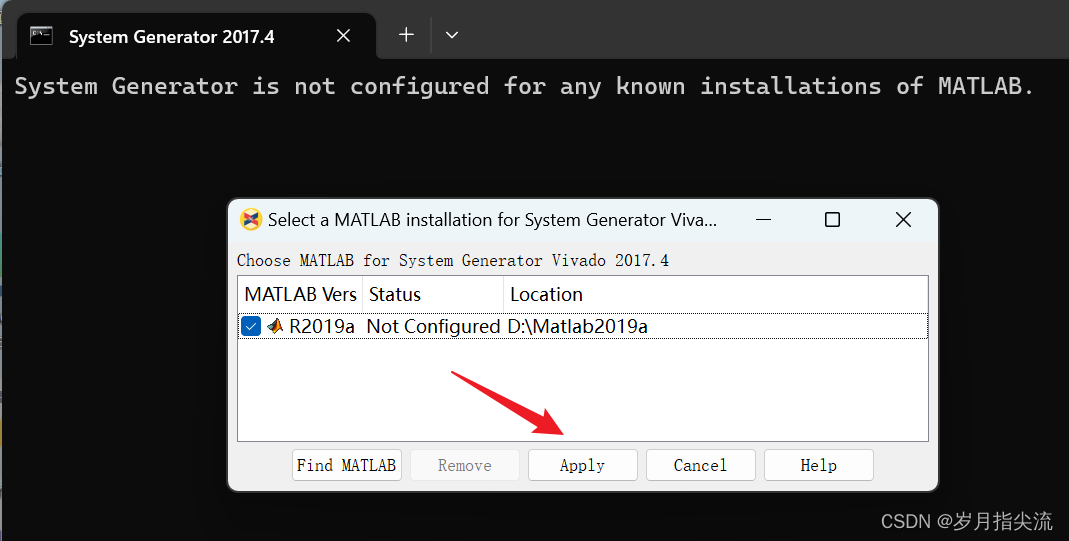

再次双击 System Generator 2017.4,点击 Find Matlab,选择你本地 Matlab 安装目录

点击 Apply

五、使用 System Generator

1、双击桌面图标

2、打开 Simulink

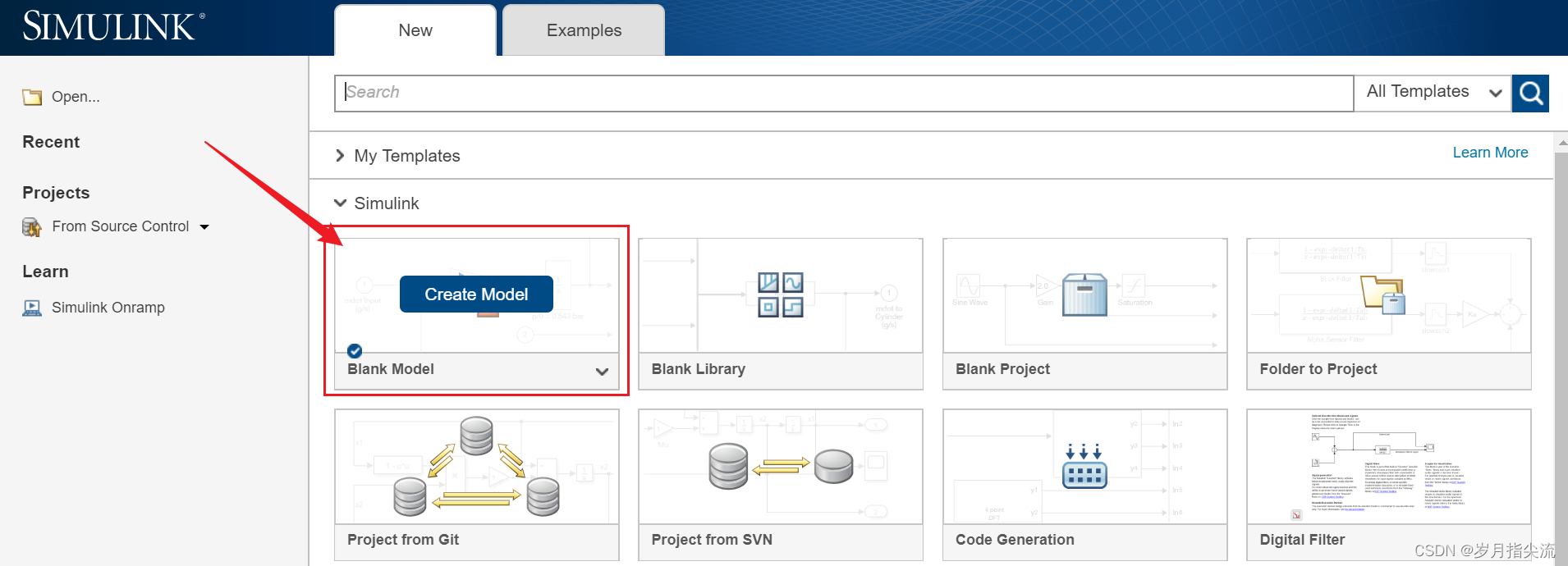

3、创建一个空白的 Simulink 模型

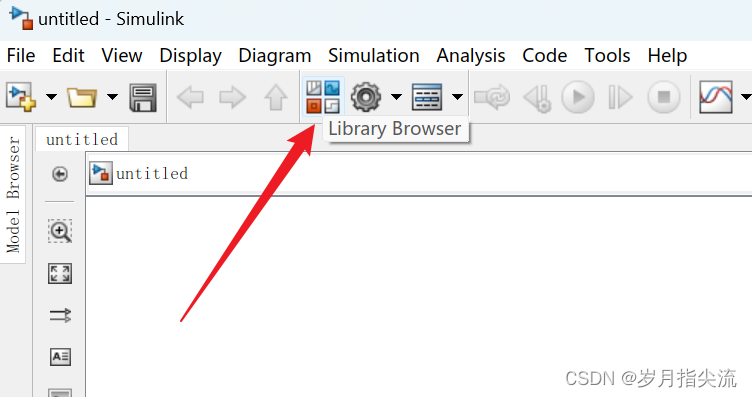

4、点击 Library Browser 库浏览器

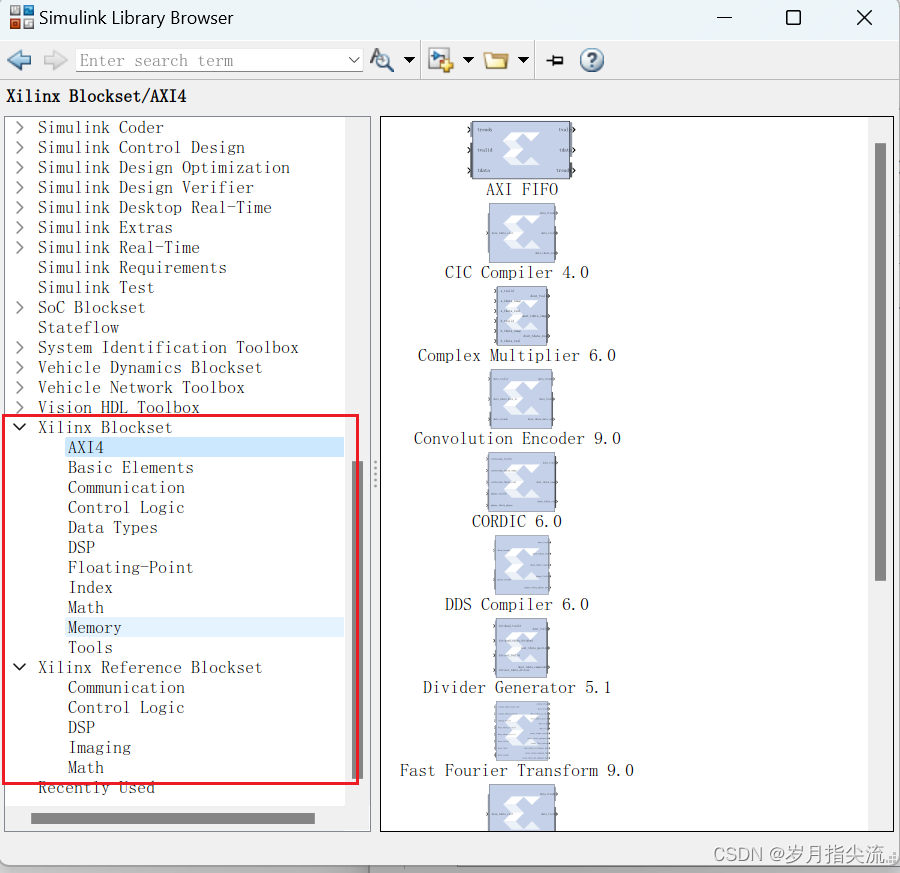

5、可以看到与 Xilinx 相关的模块库

system generator 的简单使用,可参考赛灵思官网 system generator 相关文档

我的qq:2442391036,欢迎交流!