FPGA外部触发信号毛刺产生及滤波

1、背景

最近在某个项目中,遇到输入给FPGA管脚的外部触发信号因为有毛刺产生,导致FPGA接收到的外部触发信号数量多于实际值。比如:用某个信号源产生1000个外部触发信号(上升沿触发方式)给到FPGA输入IO,实际上FPGA内部逻辑判定接收到的触发信号数量大于1000个,且数量为随机性。因为毛刺的产生的个数具有随机性。

2、原理图设计

外部触发信号经过Buffer器件(74HCT125D)输入端整形后,输出端DIO1_IN连接到FPGA的输入管脚。

3、测试过程

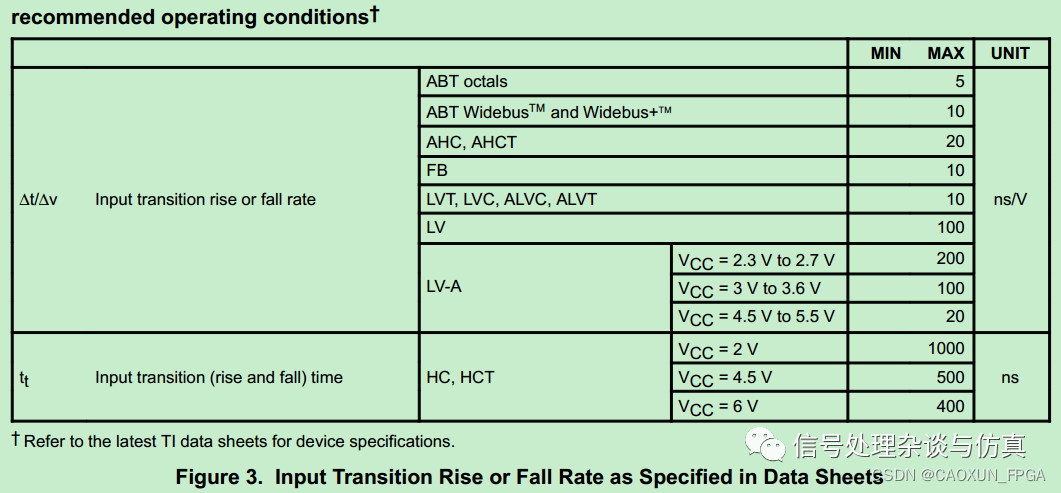

外部上升沿触发信号特征为:高电平脉宽为10us,上升沿时间为5us,故该触发信号对于数字IO输入信号而言,属于一个上升时间缓慢的输入信号。远远不满足输入信号的上升/下降转换时间指标要求。参见下图所示。

实测发现,这个上升时间缓慢的输入信号会导致Buffer(74HCT125D)器件额外产生一个上升沿毛刺。以前没有遇到过这种情况,这次算是增加了一个经验。

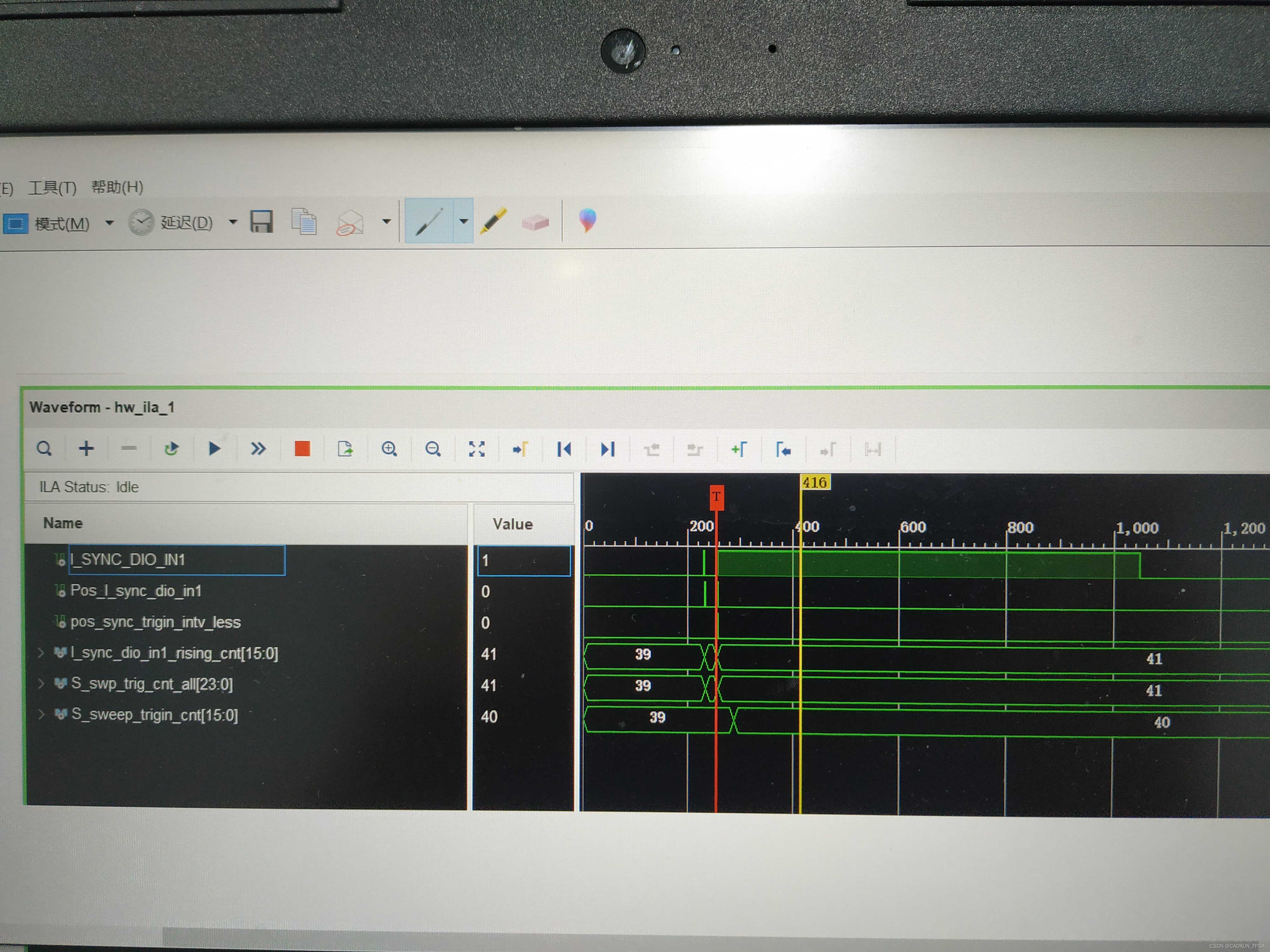

上图中,I_SYNC_DIO_IN1为FPGA管脚,用于接收经过BUFFER器件的外部触发信号。由上图可知,在ila触发时刻附近,I_SYNC_DIO_IN1先有一个上升沿毛刺,持续时间约30ns,然后才是真正的外部触发信号。

I_sync_dio_in1_rising_cnt为抓取已检测到的上升沿数量 - 滤波前。

S_sweep_trigin_cnt为抓取已检测到的上升沿数量 - 滤波后。

4、解决方法

1、增加软件滤波方式:已知上升沿毛刺持续时间为30ns,软件滤波窗口时间设定为300ns,滤波结果是OK的,参见上图S_sweep_trigin_cnt信号,为滤波后的结果。

2、更换硬件BUFFER器件:选型输入信号的上升/下降转换时间指标要求时间长的器件。

实际工程中,最终解决方案为:上述两种方式同时采用,从而确保功能的可靠性和抗干扰性。

5、参考连接

1、CMOS器件的输入信号上升时间为什么不能太长?

2、https://www.icxbk.com/ask/detail/18132.html stm32的单片机识别的高低电平?