赛灵思ZYNQ官方文档UG585自学翻译笔记:UART Controller,通用异步收发传输器控制器

一段话总结

XILINX 的 UART 控制器是全双工异步收发器,支持可编程波特率、64 字节收发 FIFO及多种数据格式(6 - 8 数据位、1 - 2 停止位、多种校验方式),具备错误检测、中断生成等功能。其通过配置和模式寄存器控制操作,状态可从相关状态寄存器读取,包含独立的收发数据路径,支持回环配置,还可用于类调制解调器应用,且有特定的时钟、复位及 I/O 接口配置方式。

基本介绍性质:全双工异步收发器控制:由配置和模式寄存器控制状态读取:通过状态、中断状态和调制解调器状态寄存器结构:独立Rx和Tx数据路径,各含64字节FIFO主要特性波特率:可编程波特率发生器FIFO:64字节收发FIFO协议:可编程(数据位、停止位、校验)错误检测:奇偶校验、帧错误、溢出错误其他:行中断生成、中断生成、多种RxD和TxD模式等功能描述控制逻辑:含控制和模式寄存器波特率发生器:生成相关时钟,有计算公式收发FIFO:存储数据,有多种状态标识数据流转:发送和接收数据的处理过程模式切换:四种操作模式状态和中断:相关寄存器及中断处理调制解调器控制:控制通信及相关配置编程指南启动序列:复位、配置I/O等多步骤控制器配置:字符帧、波特率等设置数据收发: polling和中断两种方式寄存器:各类功能寄存器概述系统功能时钟:参考时钟和CPU_1x时钟复位:控制器复位的两种方式I/O接口MIO编程:信号路由配置MIO - EMIO信号:相关信号及对应引脚

详细总结

1. 基本介绍

- 性质:UART 控制器是全双工异步接收器和发射器。

- 核心控制与状态读取:操作由配置和模式寄存器控制,FIFO 状态、调制解调器信号等通过状态、中断状态和调制解调器状态寄存器读取。

- 结构:含独立的 Rx 和 Tx 数据路径,每条路径都有一个 64 字节 FIFO,支持 RxD 和 TxD 信号的各种回环配置,软件通过 Rx 和 Tx 数据端口寄存器读写数据字节。

- 类调制解调器应用:调制解调器控制模块检测和生成调制解调器握手信号,并根据握手协议控制收发路径。

2. 主要特性

- 波特率:具备可编程波特率发生器。

- FIFO:64 字节接收和发送 FIFO。

- 可编程协议

- 数据位:6、7 或 8 位

- 停止位:1、1.5 或 2 位

- 校验:奇校验、偶校验、空校验、标记校验或无校验

- 错误检测:支持奇偶校验、帧错误和溢出错误检测。

- 其他功能:行中断生成、中断生成、RxD 和 TxD 多种模式(正常 / 回显和诊断回环)、UART 0 与 UART 1 回环选项,调制解调器控制信号(CTS、RTS 等)仅在 EMIO 接口可用。

3. 功能描述

- 控制逻辑:包含控制寄存器和模式寄存器,控制寄存器用于启用、禁用收发器模块等,模式寄存器用于选择波特率发生器使用的时钟等。

- 波特率发生器

- 可使用 uart_ref_clk 或 uart_ref_clk/8 作为时钟,由模式寄存器的 CLKS 位选择。

- 生成 baud_sample、baud_tx_rate 和 baud_rx_rate 三种时钟,计算公式如下

- \(baud\_sample=\frac{sel\_clk}{CD}\)

- \(baud\_rate=\frac{sel\_clk}{CD\times(BDIV + 1)}\)

- 重要提示:写入波特率发生器寄存器或波特率分频器寄存器前必须禁用收发器,并在重新启用前对两者进行软复位。

- 示例:当 UART_Ref_Clk=50MHz 时,部分参数如下表

| Clock | Baud Rate | Actual CD | BDIV | Actual Baud Rate | Error (BPS) | % Error |

|---|---|---|---|---|---|---|

| UART Ref clock | 600 | 10417 | 7 | 599.980 | 0.020 | -0.003 |

| UART Ref clock | 9,600 | 651 | 7 | 9,600.614 | 0.614 | 0.006 |

| UART Ref clock | 115,200 | 62 | 6 | 115,207.37 | 7.373 | 0.0064 |

- 收发 FIFO

- 发送 FIFO(TxFIFO):存储从 APB 接口写入的数据,有满、空、近满等状态标识,可设置填充水平阈值触发(TTRIG)。

- 接收 FIFO(RxFIFO):存储接收器串行移位寄存器接收的数据,有满、空等状态标识,可设置填充水平阈值触发(RTRIG),范围 1 - 63。

- 数据流转

- 发送:发送模块从 TxFIFO 取出并行数据加载到移位寄存器串行发送,按起始位、数据位、校验位、停止位的顺序,最低有效位先发送。

- 接收:UART 使用 baud_sample 对 RxD 信号过采样,检测到有效起始位后重新同步 baud_rx_rate,通过多数投票确定数据位值,组装完成后推入 RxFIFO。

- 错误类型

- 奇偶校验错误:接收数据的奇偶校验结果与接收的奇偶位不同时设置。

- 帧错误:接收器在帧末尾未收到有效停止位时设置。

- 溢出错误:RxFIFO 满时检测到新的起始位,数据丢失时设置。

- 接收器超时机制:使用 10 位递减计数器,可通过寄存器编程超时周期,超时后设置相关中断位。

- I/O 模式切换:由 uart.mode_reg0 [CHMODE] 控制,有正常、自动回显、本地回环、远程回环四种模式。

- UART0 - to - UART1 连接:设置 slcr.LOOP [UA0_LOOP_UA1] 位为 1,可将一个控制器的 RxD 和 CTS 输入信号连接到另一个的 TxD 和 RTS 输出信号。

- 状态和中断

- 状态寄存器:Chnl_int_sts_reg0(可生成中断,位是粘性的)和 Channel_sts_reg0(仅用于读取状态)。

- 中断屏蔽寄存器:Intrpt_mask_reg0,用于屏蔽 Chnl_int_sts_reg0 中的原始中断。

- 中断类型:包括非 FIFO 中断(超时、奇偶校验错误等)和 FIFO 中断(溢出、满、触发等)。

- 调制解调器控制

- 包含调制解调器状态寄存器、控制寄存器等,支持自动和手动流控制模式。

- 自动流控制模式:RTS 信号根据 RxFIFO 填充水平断言和撤销,仅在 CTS 输入断言时发送数据。

- 手动流控制模式:软件通过相关寄存器控制 DTR 和 RTS 信号。

4. 编程指南

- 启动序列:复位控制器、配置 I/O 信号路由、配置 UART_Ref_Clk、配置控制器功能、配置中断、配置调制解调器控制(可选)、管理收发数据。

- 控制器配置:包括配置 UART 字符帧、波特率、FIFO 触发水平、Rx 超时机制和启用控制器等步骤。

- 数据收发

- 发送数据:支持 polling 和中断两种方法。

- 接收数据:同样支持 polling 和中断两种方法。

- RxFIFO 触发水平中断:编程触发水平、启用 / 禁用中断、清除中断等操作。

- 寄存器概述:包括配置、中断处理、数据、接收器、发射器、调制解调器等相关寄存器。

5. 系统功能

- 时钟:控制器和 I/O 接口由 UART_REF_CLK 驱动,互连需要 APB 接口时钟(CPU_1x),均来自 PS 时钟子系统,可通过相关寄存器配置。

- 复位:控制器复位位由 PS 生成,有断言和撤销控制器复位两种选项。

6. I/O 接口

- MIO 编程:UART 的 RxD 和 TxD 信号可路由到多个 MIO 引脚或 EMIO 接口,调制解调器控制信号仅路由到 EMIO 接口,可通过相关寄存器配置 MIO 引脚。

- MIO - EMIO 信号:列出了 UART 各接口信号对应的 MIO 引脚和 EMIO 信号。

关键问题

问题:UART 控制器的波特率是如何计算的?其计算涉及哪些关键参数? 答案:UART 控制器的波特率计算公式为\(baud\_rate=\frac{sel\_clk}{CD\times(BDIV + 1)}\),其中 sel_clk 是由模式寄存器的 CLKS 位选择的时钟(uart_ref_clk 或 uart_ref_clk/8),CD 是波特率发生器寄存器中的 CD 字段值(1 - 65535),BDIV 是波特率分频器寄存器中的 BDIV 字段值(4 - 255,复位值为 15)。

问题:UART 控制器的收发 FIFO 有哪些主要状态标识?各自的含义是什么? 答案:- 发送 FIFO(TxFIFO):TFULL 表示 TxFIFO 完全满,无法再加载数据;TEMPTY 表示 TxFIFO 为空;TNFULL 表示 TxFIFO 仅剩 1 字节空闲;TTRIG 表示 TxFIFO 填充水平达到编程的触发值。

- 接收 FIFO(RxFIFO):RFUL 表示 RxFIFO 满,无法再加载数据;REMPTY 表示 RxFIFO 为空;RTRIG 表示 RxFIFO 填充水平达到编程的触发值。

问题:UART 控制器的 I/O 模式切换有哪几种模式?每种模式的特点是什么? 答案:- 正常模式:用于标准 UART 操作。

- 自动回显模式:在 RxD 上接收数据,模式开关将数据路由到接收器和 TxD 引脚,发送器的数据无法从控制器发送出去。

- 本地回环模式:不连接到 RxD 或 TxD 引脚,发送的数据回环到接收器。

- 远程回环模式:将 RxD 信号连接到 TxD 信号,控制器不能在 TxD 上发送任何内容,也不能在 RxD 上接收任何内容。

XILINX UART 控制器

第 19 章

19.1 概述

UART 控制器是一种全双工异步收发器,支持多种可编程波特率和 I/O 信号格式。该控制器可支持自动奇偶校验生成和多主机检测模式。

UART 的操作由配置寄存器和模式寄存器控制。FIFO 的状态、调制解调器信号和其他控制器功能可通过状态寄存器、中断状态寄存器和调制解调器状态寄存器读取。

控制器采用独立的接收(Rx)和发送(Tx)数据路径,每条路径均包含一个 64 字节的 FIFO。控制器对 Tx 和 Rx FIFO 中的数据进行串行化和反串行化处理,并包含模式切换功能,以支持 RxD 和 TxD 信号的多种回环配置。FIFO 中断状态位支持轮询或中断驱动的处理程序。软件通过 Rx 和 Tx 数据端口寄存器读写数据字节。

当 UART 用于类调制解调器应用时,调制解调器控制模块会检测并生成调制解调器握手信号,并根据握手协议控制接收和发送路径。

19.1.1 特性

每个 UART 控制器(UART 0 和 UART 1)具有以下特性:

- 可编程波特率发生器

- 64 字节接收和发送 FIFO

- 可编程协议:

- 6、7 或 8 个数据位

- 1、1.5 或 2 个停止位

- 奇校验、偶校验、空校验、标记校验或无校验

- 奇偶校验、帧错误和溢出错误检测

- 行中断生成

- 中断生成

- RxD 和 TxD 模式:正常 / 回显模式以及使用模式切换的诊断回环模式

- UART 0 与 UART 1 回环选项

- 调制解调器控制信号:CTS、RTS、DSR、DTR、RI 和 DCD 仅在 EMIO 接口可用

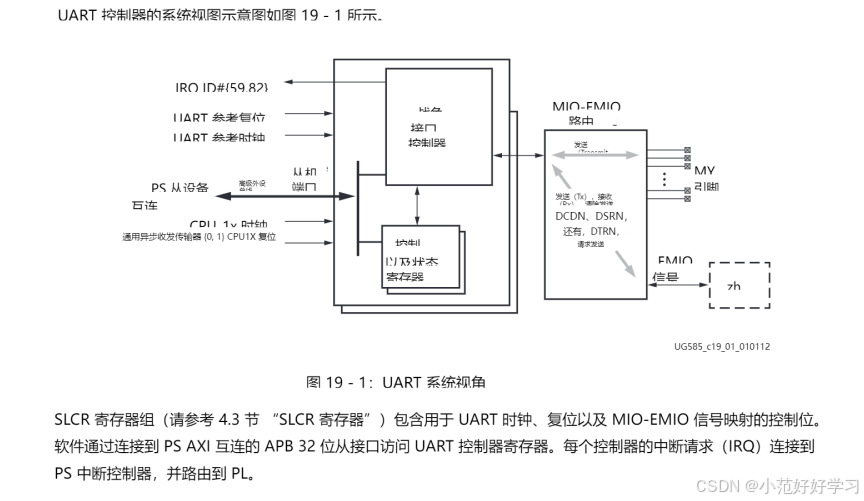

19.1.2 系统视角

UART 控制器的系统视角图如图 19-1 所示。

(图 19-1:UART 系统视角图,包含 IRQ ID# {59, 82}、MIO-EMIO 路由、UART 接口控制器、UART REF_RST、UART REF_CLK、Tx/Rx、MIO、PS 从 APB 引脚、互连、从端口、UART {0,1}、CPU1X_RST、CPU_1x 时钟、控制和状态寄存器、EMIO 信号、PL 等元素)

slcr 寄存器组(参见 4.3 节 slcr 寄存器)包含用于 UART 时钟、复位和 MIO-EMIO 信号映射的控制位。软件通过连接到 PS AXI 互连的 APB 32 位从接口访问 UART 控制器寄存器。每个控制器的 IRQ 连接到 PS 中断控制器并路由到 PL。

19.1.3 注意事项

参考时钟操作限制 两个 UART 控制器共用一个 PS 时钟发生器。送至每个 UART 控制器波特率发生器的参考时钟(UART_Ref_Clk)频率相同,但可单独启用,参见 25.6.3 节 SDIO、SMC、SPI、Quad-SPI 和 UART 时钟。控制器始终由内部 PS 时钟发生器提供时钟。

注意:CPU_1x 和 UART_Ref_clk 时钟之间的频率关系没有限制。

7z007s 和 7z010 CLG225 器件 7z007s 单核和 7z010 双核 CLG225 器件支持 32 个 MIO 引脚,如 MIO 概览表(第 52 页)所示。这限制了 UART 信号在 MIO 引脚上的可用性。如有需要,UART 的 TxD 和 RxD 信号可通过 EMIO 接口路由并传递到 PL 引脚。所有 CLG225 器件的限制列于 1.1.3 节注意事项中。

19.2 功能描述

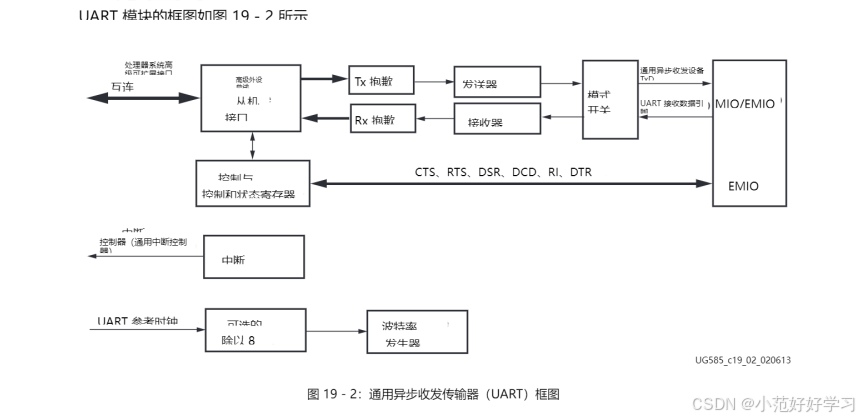

19.2.1 框图

UART 模块的框图如图 19-2 所示。

(图 19-2:UART 框图,包含互连 PS AXI APB 从接口、UART TxD、TxFIFO、发送器、模式切换、MIO/EMIO、UART RxD、RxFIFO、接收器、CTS/RTS/DSR/DCD/RI/DTR、控制和状态寄存器、EMIO、中断控制器(GIC)、中断、UART 参考时钟、可选的 8 分频、波特率发生器等元素)

19.2.2 控制逻辑

控制逻辑包含控制寄存器和模式寄存器,用于选择 UART 的各种操作模式。

控制寄存器用于启用、禁用接收器和发送器模块,以及对其发出软复位。此外,它还可重启接收器超时周期,并控制发送器中断逻辑。

接收行中断检测必须通过软件实现,它会由帧错误后接 RxFIFO 中的一个或多个零字节来指示。

模式寄存器选择波特率发生器使用的时钟,还选择发送和接收数据所用的数据位长度、奇偶校验位和停止位。此外,它还选择 UART 的操作模式,可根据需要在正常 UART 模式、自动回显模式、本地回环模式或远程回环模式之间切换。

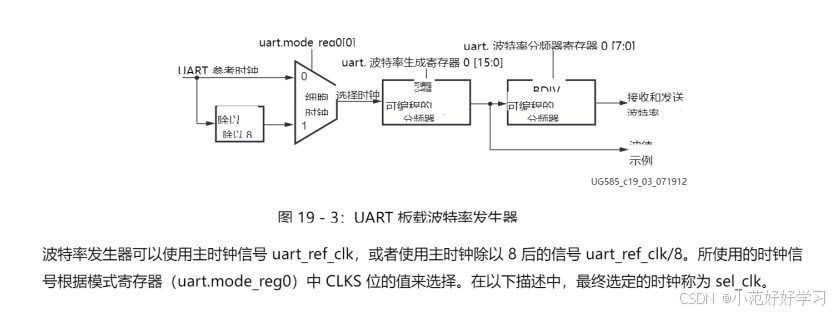

19.2.3 波特率发生器

波特率发生器为接收器和发送器提供位周期时钟(即波特率时钟)。波特率时钟通过分配基准时钟 uart_clk 和单周期时钟使能来实现,以达到相应的分频效果。波特率生成的有效逻辑如图 19-3 所示。

(图 19-3:UART 波特率发生器,包含 uart.Baud_rate_divider_reg0 [7:0]、uart.mode_reg0 [0]、uart.Baud_rate_gen_reg0 [15:0]、UART 参考时钟、CD 可编程分频器、BDIV 可编程分频器、Sel、Clk、sel_clk、Rx 和 Tx 波特率、8 分频、波特采样等元素)

波特率发生器可使用主时钟信号 uart_ref_clk 或主时钟除以 8 的信号 uart_ref_clk/8。所用时钟信号由模式寄存器(uart.mode_reg0)中的 CLKS 位的值选择。所选时钟在以下描述中称为 sel_clk。

sel_clk 时钟经过分频生成另外三个时钟:baud_sample、baud_tx_rate 和 baud_rx_rate。baud_tx_rate 是用于发送数据的目标波特率;baud_rx_rate 名义上与 baud_tx_rate 速率相同,但会与输入的接收数据重新同步;baud_sample 的速率是 baud_rx_rate 和 baud_tx_rate 的([BDIV]+1)倍,用于对接收数据进行过采样。

sel_clk 时钟频率除以波特率发生器寄存器中的 CD 字段值,生成 baud_sample 时钟使能。该寄存器可编程为 1 到 65535 之间的值。

baud_sample 时钟除以([BDIV]+1)。BDIV 是波特率分频器寄存器中的可编程字段,可编程为 4 到 255 之间的值,其复位值为 15,意味着默认情况下每个 baud_tx_clock/baud_rx_rate 对应 16 个 baud_sample 时钟。

因此,baud_sample 时钟使能的频率如公式 19-1 所示: \(baud\_sample=\frac{sel\_clk}{CD}\quad(公式19-1)\)

baud_rx_rate 和 baud_tx_rate 时钟使能的频率如公式 19-2 所示: \(baud\_rate=\frac{sel\_clk}{CD\times(BDIV + 1)}\quad(公式19-2)\)

重要提示:在写入波特率发生器寄存器(uart.Baud_rate_gen_reg0)或波特率分频器寄存器(uart.Baud_rate_divider_reg0)之前,必须禁用发送器和接收器。在重新启用它们之前,必须对发送器和接收器发出软复位。

表 19-1 展示了 uart_ref_clk 时钟、波特率、时钟分频器(CD 和 BDIV)之间的关系以及误差率的一些示例。高亮条目显示了 CD 和 BDIV 的默认复位值。这些示例假设系统时钟频率为 UART_Ref_Clk=50 MHz,Uart_ref_clk/8=6.25 MHz。可更改 UART 参考时钟的频率以获得更精确的波特率频率,有关编程 UART_Ref_Clk 的详细信息,请参见第 25 章时钟。

表 19-1:UART 参数值示例

| 时钟 | 波特率 | 计算的 CD 值 | 实际的 CD 值 | BDIV | 实际波特率 | 误差(BPS) | 误差百分比 |

|---|---|---|---|---|---|---|---|

| UART 参考时钟 | 600 | 10416.667 | 10417 | 7 | 599.980 | 0.020 | -0.003 |

| UART 参考时钟 / 8 | 9600 | 81.380 | 81 | 7 | 9645.061 | 45.061 | 0.469 |

| UART 参考时钟 | 9600 | 651.041 | 651 | 7 | 9600.614 | 0.614 | 0.006 |

| UART 参考时钟 | 28800 | 347.222 | 347 | 4 | 28818.44 | 18.44 | 0.064 |

| UART 参考时钟 | 115200 | 62.004 | 62 | 6 | 115207.37 | 7.373 | 0.0064 |

| UART 参考时钟 | 230400 | 31.002 | 31 | 6 | 230414.75 | 14.75 | 0.006 |

| UART 参考时钟 | 460800 | 27.127 | 9 | 11 | 462962.96 | 2162.96 | 0.469 |

| UART 参考时钟 | 921600 | 9.042 | 9 | 5 | 925925.92 | 4325.93 | 0.469 |

19.2.4 发送 FIFO

发送 FIFO(TxFIFO)存储从 APB 接口写入的数据,直到发送模块将其取出并加载到其移位寄存器中。TxFIFO 的最大数据宽度为 8 位。通过写入 TxFIFO 寄存器将数据加载到 TxFIFO 中。

当数据加载到 TxFIFO 中时,TxFIFO 空标志被清除,并保持低电平状态,直到 TxFIFO 中的最后一个字被取出并加载到发送器移位寄存器中。这意味着主机软件在需要下一个数据之前有一个完整的串行字时间,使其能够在空标志置位时做出反应,并在 TxFIFO 中写入另一个字而不会损失传输时间。

TxFIFO 满中断状态(TFULL)指示 TxFIFO 已完全满,防止更多数据加载到 TxFIFO 中。如果对 TxFIFO 执行另一次 APB 写入,将触发溢出,且写入的数据不会加载到 TxFIFO 中。发送 FIFO 近满标志(TNFULL)指示 FIFO 中没有足够的空闲空间来进行另一次编程大小的写入,这由模式寄存器的 WSIZE 位控制。

TxFIFO 近满标志(TNFULL)指示 TxFIFO 中仅剩 1 字节空闲。

可在 TxFIFO 填充水平上设置阈值触发(TTRIG)。发送器触发寄存器可用于设置该值,当 TxFIFO 填充水平达到该编程值时,触发置位。

19.2.5 发送器数据流

发送模块从 TxFIFO 中取出并行数据并加载到发送器移位寄存器中,以便进行串行化处理。

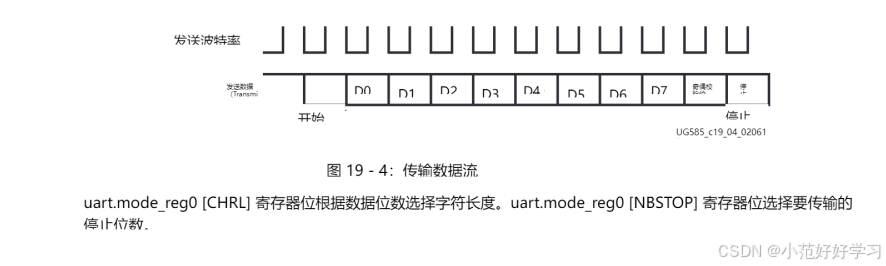

发送模块将起始位、数据位、奇偶校验位和停止位移出为串行数据流。数据在发送波特率时钟使能(baud_tx_rate)的下降沿发送,最低有效位优先。典型的发送数据流如图 19-4 所示。

(图 19-4:发送数据流,包含 baud_tx_rate、TXD、D0-D7、PA、START、STOP 等元素)

uart.mode_reg0 [CHRL] 寄存器位选择字符长度(以数据位数量表示)。uart.mode_reg0 [NBSTOP] 寄存器位选择要发送的停止位数量。

19.2.6 接收 FIFO

接收 FIFO(RxFIFO)存储由接收器串行移位寄存器接收的数据。RxFIFO 的最大数据宽度为 8 位。

当数据加载到 RxFIFO 中时,RxFIFO 空标志被清除,并保持低电平状态,直到 RxFIFO 中的所有数据都通过 APB 接口传输完毕。从空的 RxFIFO 读取数据将返回零。

RxFIFO 满状态(Chnl_int_sts_reg0 [RFUL] 和 Channel_sts_reg0 [RFUL] 位)指示 RxFIFO 已满,防止更多数据加载到 RxFIFO 中。当 RxFIFO 中有空间可用时,接收器中存储的任何字符都将被加载。

可在 RxFIFO 填充水平上设置阈值触发(RTRIG)。接收 FIFO 触发电平寄存器(Rcvr_FIFO_trigger_level0)可用于设置该值,当 RxFIFO 填充水平超过该编程值时,触发置位。范围为 1 到 63。

19.2.7 接收器数据捕获

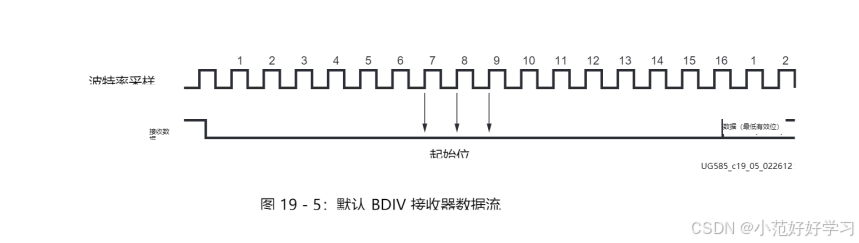

UART 使用 UARTx_REF_CLK 和时钟使能(baud_sample)对 UARTx_RxD 信号进行持续过采样。当采样检测到向低电平的跳变时,可能指示起始位的开始。当 UART 检测到 UART_RxD 输入为低电平时,它等待 BDIV 波特率时钟周期的一半计数,然后再采样三次。如果这三个位仍指示低电平,则接收器认为这是有效的起始位,如图 19-5(默认 BDIV 为 15 时)所示。

(图 19-5:默认 BDIV 的接收器数据流,包含 baud_sample、Data (LSB)、rxd、Start Bit 等元素及 6-15 的计数标识)

当识别到有效的起始位时,接收器波特率时钟使能(baud_rx_rate)会重新同步,以便对输入的 UART RxD 信号的进一步采样在每个位的理论中点附近进行,如图 19-6 所示。

(图 19-6:重新同步的接收器数据流,包含 baud_rx_rate、baud_sample、Data Bit、rxd 等元素及 1-2 的标识)

当重新同步的 baud_rx_rate 为高电平时,比较最后三次采样的位。逻辑值通过多数投票确定:两个具有相同值的采样定义数据位的值。当确定串行数据位的值后,将其移位到接收移位寄存器中。当组装完成一个完整的字符后,寄存器的内容将被推入 RxFIFO。

接收器奇偶校验错误 每次接收一个字符时,接收器会根据 uart.mode_reg0 [PAR] 位字段计算接收数据位的奇偶校验,然后将结果与接收的奇偶校验位进行比较。如果检测到差异,则奇偶校验错误位置位(=1),即 uart.Chnl_int_sts_reg0 [PARE]。如果启用,将生成中断。

接收器帧错误 当接收器在一帧的末尾未收到有效的停止位时,帧错误位置位(=1),即 uart.Chnl_int_sts_reg0 [FRAME]。如果启用,将生成中断。

接收器溢出错误 当接收到一个字符时,控制器会检查 RxFIFO 是否有空间。如果有空间,则将该字符写入 RxFIFO;如果 RxFIFO 已满,控制器会等待。如果检测到 RxD 上的后续起始位且 RxFIFO 仍满,则数据将丢失,控制器会设置 Rx 溢出中断位,即 uart.Chnl_int_sts_reg0 [ROVR]=1。如果启用,将生成中断。

接收器超时机制 接收器超时机制使接收器能够检测到 inactive 的 RxD 信号(持续高电平)。超时周期通过写入 uart.Rcvr_timeout_reg0 [RTO] 位字段进行编程。超时机制使用一个 10 位递减计数器。每当在 RxD 信号上收到新的起始位,或者每当软件向 uart.Control_reg0 [RSTTO] 写入 1(无论之前的 [RSTTO] 值如何),计数器都会重新加载并开始倒计时。

如果在 1023 个位周期内没有起始位或复位超时,则会发生超时。中断状态寄存器中的接收器超时错误位 [TIMEOUT] 将置位,并且应向控制寄存器中的 [RSTTO] 位写入 1 以重启超时计数器,该计数器会加载新编程的超时值。

计数器的高 8 位从 [RTO] 位字段的值重新加载,低 2 位初始化为零。计数器由 UART 位时钟提供时钟。例如,如果 [RTO]=0xFF,则超时周期为 1023 个位时钟(256×4 减 1)。如果向 [RTO] 位写入 0,则超时机制被禁用。

当递减计数器达到 0 时,发生接收器超时,控制器设置超时中断状态位 uart.Chnl_int_sts_reg0 [TIMEOUT]=1。如果中断已启用(uart.Intrpt_mask_reg0 [TIMEOUT]=1),则向 PS 中断控制器的 IRQ 信号被断言。

每当发生超时中断时,通过向 Chnl_int_sts_reg0 [TIMEOUT] 位写回 1 来清除它。软件必须设置 uart.Control_reg0 [RSTTO]=1 才能生成更多的接收超时中断。

19.2.8 I/O 模式切换

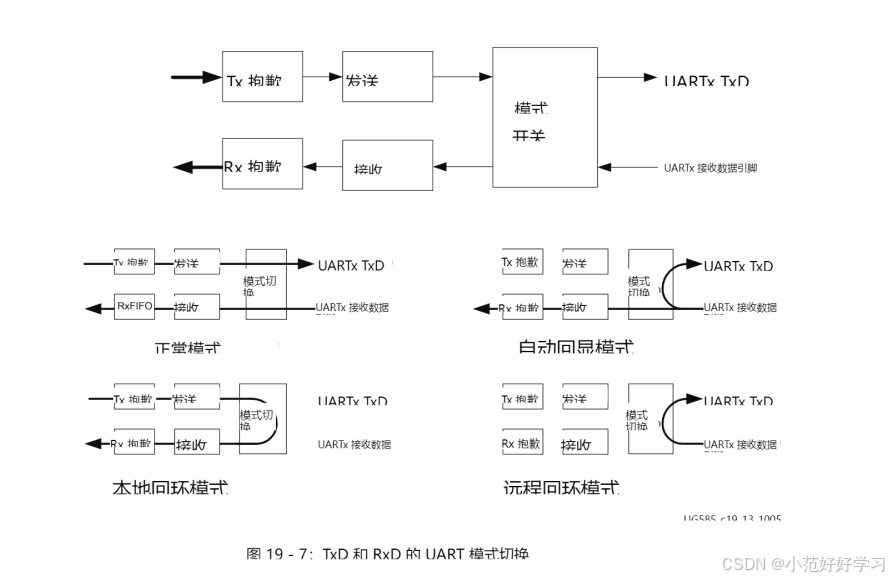

模式切换控制控制器内 RxD 和 TxD 信号的路由,如图 19-7 所示。无论 UARTx TxD/RxD I/O 信号的 MIO-EMIO 路由如何,使用模式切换的回环都会发生。如图 19-7 所示,有四种操作模式。模式由 uart.mode_reg0 [CHMODE] 寄存器位字段控制:正常模式、自动回显模式、本地回环模式和远程回环模式。

(图 19-7:UART TxD 和 RxD 的模式切换,包含四种模式:正常模式、自动回显模式、本地回环模式、远程回环模式,每种模式均展示 TxFIFO、UARTx TxD、发送器、模式切换、RxFIFO、UARTx RxD、接收器等元素的连接关系)

正常模式 正常模式用于标准 UART 操作。

自动回显模式 回显模式在 RxD 上接收数据,模式切换将数据路由到接收器和 TxD 引脚。发送器的数据无法从控制器发送出去。

本地回环模式 本地回环模式不连接到 RxD 或 TxD 引脚,而是将发送的数据回环到接收器。

远程回环模式 远程回环模式将 RxD 信号连接到 TxD 信号。在这种模式下,控制器不能在 TxD 上发送任何内容,也不能在 RxD 上接收任何内容。

19.2.9 UART0 与 UART1 连接

PS 中的两个 UART 控制器的 I/O 信号可以连接在一起。在这种模式下,通过设置 slcr.LOOP [UA0_LOOP_UA1] 位 = 1,一个控制器的 RxD 和 CTS 输入信号连接到另一个 UART 控制器的 TxD 和 RTS 输出信号。其他流控制信号不连接。无论 MIO-EMIO 编程如何,这种 UART 到 UART 的连接都会发生。

19.2.10 状态和中断

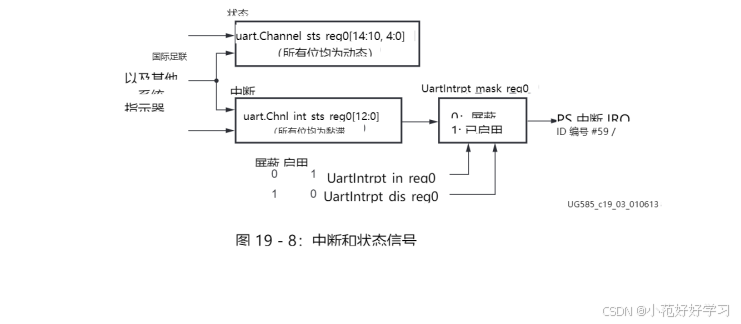

中断和状态寄存器 有两个状态寄存器可由软件读取,均显示原始状态。Chnl_int_sts_reg0 寄存器可读取状态并生成中断;Channel_sts_reg0 寄存器仅可读取状态。

Chnl_int_sts_reg0 寄存器是粘性的,一旦某位置位,该位将保持置位状态,直到软件将其清除。写入 1 可清除该位。该寄存器与 Intrpt_mask_reg0 掩码寄存器进行按位与运算。如果任何按位与运算的结果 = 1,则向 PS 中断控制器的 UART 中断被断言。

- Channel_sts_reg0:只读原始状态,写入被忽略。

各种 FIFO 和系统指示器被路由到 uart.Channel_sts_reg0 寄存器和 / 或 uart.Chnl_int_sts_reg0 寄存器,如图 19-8 所示。

(图 19-8:中断和状态信号,包含 Status、uart.Channel_sts_reg0 [14:10,4:0](所有位均为动态)、其他 FIFO 指示器、系统、uart.Intrpt_mask_reg0、中断、PS 中断 IRQ ID#59/#82、uart.Chnl_int_sts_reg0 [12:0](所有位均为粘性)、0:屏蔽 1:启用、掩码使能、uart.Intrpt_en_reg0、uart.Intrpt_dis_reg0 等元素及连接关系)

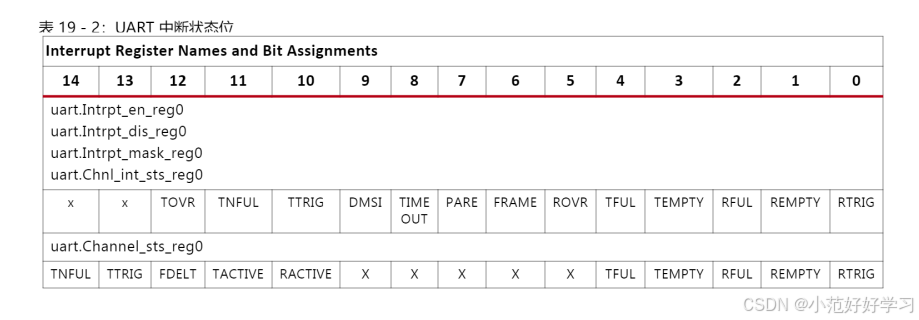

中断寄存器和位字段汇总于表 19-2。

表 19-2:UART 中断状态位

| 中断寄存器名称和位分配 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| uart.Intrpt_en_reg0、uart.Intrpt_dis_reg0、uart.Intrpt_mask_reg0、uart.Chnl_int_sts_reg0 | x | x | TOVR | TNFUL | TTRIG | DMSI | TIMEOUT | PARE | FRAME | ROVR | TFUL | TEMPTY | RFUL | REMPTY | RTRIG |

| uart.Channel_sts_reg0 | TNFUL | TTRIG | FDELT | TACTIVE | RACTIVE | X | X | X | X | X | TFUL | TEMPTY | RFUL | REMPTY | RTRIG |

中断掩码寄存器 Intrpt_mask_reg0 是只读中断掩码 / 使能寄存器,用于屏蔽 Chnl_int_sts_reg0 寄存器中的各个原始中断:

- 如果掩码位 = 0,则中断被屏蔽;

- 如果掩码位 = 1,则中断被启用。

该掩码由只写的 Intrpt_en_reg0 和 Intrpt_dis_reg0 寄存器控制。每个相关的使能 / 禁用中断位应互斥设置(例如,要启用中断,向 Intrpt_en_reg0 [x] 写入 1,向 Intrpt_dis_reg0 [x] 写入 0)。

通道状态 这些状态位位于 Channel_sts_reg0 寄存器中。

- TACTIVE:发送器状态机活动状态。如果处于活动状态,发送器当前正在移出一个字符。

- RACTIVE:接收器状态机活动状态。如果处于活动状态,接收器已检测到起始位且当前正在移入一个字符。

- FDELT:接收器流延迟触发持续状态。FDELT 状态位用于监控 RxFIFO 水平与流延迟触发水平的比较情况。

非 FIFO 中断 这些中断状态位位于 Chnl_int_sts_reg0 寄存器中。

- TIMEOUT:接收器超时错误中断状态。每当接收器超时计数器因长时间空闲状态而到期时,触发此事件。

- PARE:接收器奇偶校验错误中断状态。每当接收的奇偶校验位与预期值不匹配时,触发此事件。

- FRAME:接收器帧错误中断状态。每当接收器未能检测到有效的停止位时,触发此事件(参见 19.2.7 节接收器数据捕获)。

- DMSI:指示 DCD、DSR、RI 或 CTS 调制解调器流控制信号的逻辑电平变化,包括这些信号中的任何高到低或低到高的逻辑跳变。

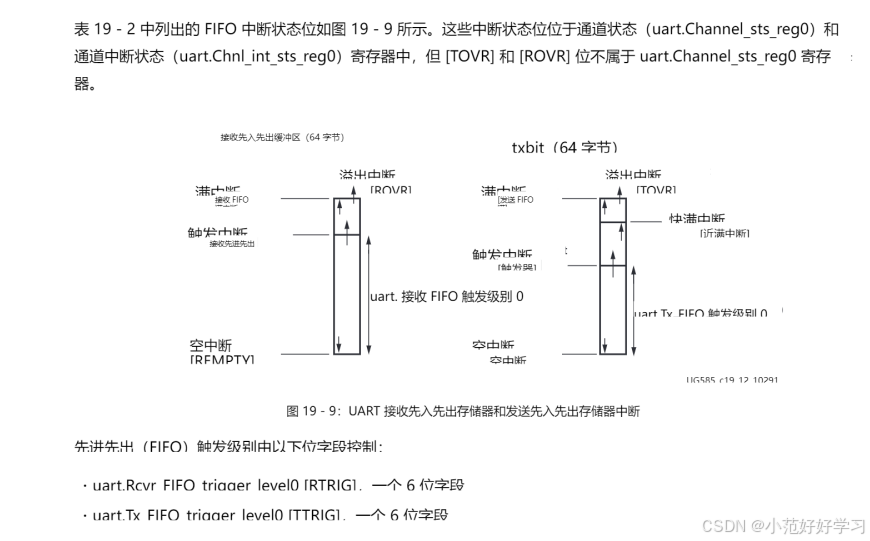

FIFO 中断 表 19-2 中列出的 FIFO 中断的状态位如图 19-9 所示。这些中断状态位位于通道状态(uart.Channel_sts_reg0)和通道中断状态(uart.Chnl_int_sts_reg0)寄存器中,例外的是 [TOVR] 和 [ROVR] 位不属于 uart.Channel_sts_reg0 寄存器。

(图 19-9:UART RxFIFO 和 TxFIFO 中断,包含 64 字节的 RxFIFO 和 TxFIFO,以及各自的溢出中断 [ROVR] 和 [TOVR]、满中断 [RFUL] 和 [TFUL]、近满中断 [TNFUL]、触发中断 [RTRIG] 和 [TTRIG]、空中断 [REMPTY] 和 [TEMPTY],以及 uart.Rcvr_FIFO_trigger_level0 和 uart.Tx_FIFO_trigger_level0)

FIFO 触发电平由以下位字段控制:

- uart.Rcvr_FIFO_trigger_level0 [RTRIG],6 位字段

- uart.Tx_FIFO_trigger_level0 [TTRIG],6 位字段

19.2.11 调制解调器控制

调制解调器控制模块便于控制调制解调器与 UART 之间的通信。它包含调制解调器状态寄存器、调制解调器控制寄存器、中断状态寄存器中的 DMSI 位以及通道状态寄存器中的 FDELT。每当调制解调器状态寄存器中的 DCTS、DDSR、TERI 或 DDCD 置位时,触发此事件。

只读的调制解调器状态寄存器用于读取清除发送(CTS)、数据载波检测(DCD)、数据设备就绪(DSR)和振铃指示(RI)调制解调器输入的值。它还报告这些输入中的任何变化,并指示当前是否启用自动流控制模式。调制解调器状态寄存器中的位通过向特定位写入 1 来清除。

可读写的调制解调器控制寄存器用于设置数据终端就绪(DTR)和请求发送(RTS)输出,并启用自动流控制模式寄存器。

默认情况下,自动流控制模式被禁用,这意味着调制解调器输入和输出完全在软件控制下工作。当通过设置调制解调器控制寄存器中的 FCM 位启用自动流控制模式时,UART 的发送和接收状态由调制解调器握手输入和输出自动控制。

在自动流控制模式下,请求发送输出根据接收器 FIFO 的当前填充水平进行断言和撤销,这导致远端发送器暂停传输,防止 UART 接收器 FIFO 溢出。流延迟寄存器(Flow_delay_reg0)中的 FDEL 字段用于在接收器 FIFO 上设置触发电平,该电平导致请求发送的撤销。它保持低电平,直到 FIFO 水平降至低于 FDEL 减 4。

此外,在自动流控制模式下,UART 仅在清除发送输入被断言时发送。当清除发送被撤销时,UART 在 next 字符边界处暂停传输。

如果选择自动流控制,则必须对流量延迟寄存器进行编程,以便通过撤销 RTS 信号来控制数据的流入。该值对应于 RTS 信号将被撤销时的 RxFIFO 水平。当 RxFIFO 水平降至流量延迟寄存器中编程值的四以下时,它将重新断言。

uart.Channel_sts_reg0 [FDELT] 寄存器位用于监控 RxFIFO 水平与流延迟触发水平的比较情况。每当 RxFIFO 水平大于或等于流延迟寄存器中编程的触发电平时,[FDELT] 位置位。

流延迟寄存器中编程的触发电平与 Rx 触发电平寄存器无关。这仅用于使用 RTS 调制解调器信号控制数据的流入。

CPU 仅在收到 Rx 触发中断时才会被接收数据中断。根据 Rx 触发电平寄存器中编程的触发电平检索数据。

可编程参数 UART 流控制信号 DTR 和 RTS 由 UART 控制器生成。

- RTS 流控制信号用于为 Rx 发信号(向连接的终端发送就绪信号)。

- DTR 流控制信号指示 UART 控制器的状态(数据终端就绪)。

DTR 和 RTS 可由软件手动控制或由控制器自动控制。

- 在自动模式下,调制解调器控制单元断言和撤销 RTS 和 DTR 信号。

- 在手动模式下,软件使用 uart.Modem_ctrl_reg0 控制 RTS 和 DTR 信号。

uart.Modem_ctrl_reg0:

- [DTR]:数据终端就绪输出信号

- [RTS]:请求发送输出信号

- [FCM]:选择自动或手动流控制

uart.Modem_sts_reg0:

- [DCTS]:Delta 清除发送(输入)状态

- [DDSR]:Delta 数据设备就绪(输入)状态

- [TERI]:后沿振铃指示(输入)状态

- [DDCD]:Delta 数据载波检测(输入)状态

选择以下操作选项之一:

示例:自动流控制

- 设置 RTS 触发电平。写入 uart.Flow_Delay_reg0 寄存器,这是撤销调制解调器信号 RTS 的触发电平。

- 选择自动流控制。向 uart.Modem_ctrl_reg0 [FCM] 写入 1。

- 验证模式是否切换到自动模式。读取 uart.Modem_sts_reg0 [FCMS],直到其等于 1。

当软件向 uart.Modem_ctrl_reg0 [FCM] 写入 1 时,调制解调器切换到自动模式。通过读取调制解调器状态寄存器中的 FCMS 状态位来验证从手动模式到自动模式的切换。

示例:手动流控制

- 选择手动流控制。向 uart.Modem_ctrl_reg0 [FCM] 写入 0。

- 选项 a:使用 uart.Modem_ctrl_reg0 [DTR] 控制 DTR 输出信号。

- 选项 b:使用 uart.Modem_ctrl_reg0 [RTS] 控制 RTS 输出信号。

示例:监控 DCD、DSR、RI、CTS 流控制信号的变化 控制器检测到 DCD、DSR、RI、CTS 流控制信号的逻辑电平变化。当检测到逻辑电平变化时,硬件设置 uart.Chnl_int_sts_reg0 [DMSI] 位。这种变化或通道状态可以选择性地生成中断。

- 检查流控制信号状态。uart.Modem_sts_reg0 寄存器报告调制解调器状态。

在中断模式下,当调制解调器线路上的状态发生变化而产生 DMSI 中断时,ISR 可以运行。

19.3 编程指南

19.3.1 启动序列

主要示例:启动序列

- 复位控制器:复位编程模型在 19.4.2 节复位中描述。

- 配置 I/O 信号路由:Rx/Tx 可路由到 MIO 或 EMIO。调制解调器控制信号仅在 EMIO 接口上可用(参见 19.5.1 节 MIO 编程)。

- 配置 UART_Ref_Clk:UART 时钟架构和编程模型在 19.4.1 节时钟中描述。

- 配置控制器功能:使用 uart.Control_reg0 和 uart.mode_reg0 寄存器编程 I/O 信号特性和控制器功能(示例见 19.3.2 节配置控制器功能)。

- 配置中断:在所有模式下,中断用于管理 Rx/Tx FIFO(参见 19.2.10 节状态和中断以及 19.3.5 节 RxFIFO 触发电平中断中的程序示例)。

- 配置调制解调器控制(可选):轮询和中断驱动选项(参见 19.2.11 节调制解调器控制)。

- 管理发送和接收数据:支持轮询和中断驱动的处理程序(参见 19.3.3 节发送数据和 19.3.4 节接收数据)。

19.3.2 配置控制器功能

示例:配置控制器功能 本示例配置字符帧、波特率、FIFO 触发电平、Rx 超时机制并启用控制器。所有这些步骤在复位后都是必要的,但在启用和禁用控制器之间不是必需的。

配置 UART 字符帧。向 uart.mode_reg0 写入 0x0000_0020: a. 禁用时钟预分频器 UART_REF_CLK/8:[CLKS]=0 b. 选择 8 位字符长度:[CHRL]=00 c. 选择无校验:[PAR]=100 d. 选择 1 个停止位:[NBSTOP]=00 e. 选择正常通道模式(模式切换):[CHMODE]=00

配置波特率。写入三个寄存器:uart.Control_reg0、uart.Baud_rate_gen_reg0 和 uart.Baud_rate_divider_reg0。计算的 CD 和 BDIV 值示例如表 19-1(第 587 页)所示。波特率发生器在 19.2.3 节波特率发生器中描述。 a. 禁用 Rx 路径:设置 uart.Control_reg0 [RXEN]=0,[RXDIS]=1 b. 禁用 Tx 路径:设置 uart.Control_reg0 [TXEN]=0,[TXDIS]=1 c. 将计算的 CD 值写入 uart.Baud_rate_gen_reg0 [CD] 位字段 d. 将计算的 BDIV 值写入 uart.Baud_rate_divider_reg0 [BDIV] 位值 e. 复位 Tx 和 Rx 路径:uart.Control_reg0 [TXRST] 和 [RXRST]=1(这些位是自清除的) f. 启用 Rx 路径:设置 [RXEN]=1,[RXDIS]=0 g. 启用 Tx 路径:设置 [TXEN]=1,[TXDIS]=0

设置 RxFIFO 触发电平。向 uart.Rcvr_FIFO_trigger_level0 寄存器写入触发电平:

- 选项 a:启用 Rx 触发电平:向 [RTRIG] 位字段写入 1 到 63 之间的值

- 选项 b:禁用 Rx 触发电平:向 [RTRIG] 位字段写入 0

启用控制器。向 uart.Control_reg0 寄存器写入 0x0000_0117: a. 复位 Tx 和 Rx 路径:uart.Control_reg0 [TXRST] 和 [RXRST]=1(这些位是自清除的) b. 启用 Rx 路径:[RXEN]=1,[RXDIS]=0 c. 启用 Tx 路径:[TXEN]=1,[TXDIS]=0 d. 重启接收器超时计数器:[RSTTO]=1 e. 不开始发送中断:[STTBRK]=0 f. 停止中断发送器:[STPBRK]=1

编程接收器超时机制。向 uart.Rcvr_timeout_reg0 寄存器写入超时值(参见第 589 页接收器超时机制): a. 要启用超时机制,向 [RSTTO] 位字段写入 1 到 255 之间的值 b. 要禁用超时机制,向 [RSTTO] 位字段写入 0

19.3.3 发送数据

软件可使用轮询或中断来控制向 TxFIFO 和 RxFIFO 的数据流动。

注意:当 TxFIFO 空状态为真时,软件可以写入 64 字节(TxFIFO 的大小)而无需检查 TxFIFO 状态。实际上,当发送器处于活动状态时,软件可以写入超过 64 字节的数据,因为在软件向 TxFIFO 写入数据时,控制器正在取出数据并将其串行化到 TxD 信号上。

示例:使用轮询方法发送数据 在本示例中,软件可以选择填充 TxFIFO 直到满状态位置位,或者等待 TxFIFO 为空(并写入最多 64 字节)。当 TxFIFO 近满时,软件始终可以写入一个字节。

- 检查 TxFIFO 是否为空。等待直到 uart.Channel_sts_reg0 [TEMPTY]=1。

- 用数据填充 TxFIFO。向 uart.TX_RX_FIFO0 寄存器写入 64 字节数据。

- 向 TxFIFO 写入更多数据。有两种方法:

- 选项 A:检查 TxFIFO 是否有空间再写入一个字节的数据(即 TxFIFO 未满):读取 uart.Channel_sts_reg0 [TFUL] 直到其等于 0。当 [TFUL]=0 时,向 TxFIFO 写入一个字节的数据,然后再次读取 [TFUL]。

- 选项 B:等待直到 TxFIFO 为空。读取 uart.Channel_sts_reg0 [TEMPTY] 直到其等于 1,然后转到步骤 2 用 64 字节数据填充 TxFIFO。

示例:使用中断方法发送数据 本示例最初以与轮询方法类似的方式填充 TxFIFO。然后,软件启用 TxFIFO 空中断,以提醒软件再次填充 TxFIFO。

- 禁用 TxFIFO 空中断。向 uart.Intrpt_dis_reg0 [TEMPTY] 写入 1。

- 用数据填充 TxFIFO。向 uart.TX_RX_FIFO0 寄存器写入 64 字节数据。

- 检查 TxFIFO 是否有空间再写入一个字节的数据(即 TxFIFO 未满):读取 uart.Channel_sts_reg0 [TFUL] 直到其等于 0。当 [TFUL]=0 时,向 TxFIFO 写入一个字节的数据,然后再次读取 [TFUL]。

- 重复步骤 2 和 3,直到 uart.Channel_sts_reg0 [TFUL] 未置位。

- 启用中断。向 uart.Intrpt_en_reg0 [TEMPTY] 写入 1 以启用中断。

- 等待直到 TxFIFO 为空。当 uart.Channel_int_sts_reg0 [TEMPTY] 置位为 1 时,从步骤 1 重复。

19.3.4 接收数据

示例:使用轮询方法接收数据

- 等待直到 RxFIFO 填充到触发电平。检查 uart.Channel_sts_reg0 [RTRIG]=1 或 uart.Chnl_int_sts_reg0 [TIMEOUT]=1。

- 从 RxFIFO 读取数据。从 uart.TX_RX_FIFO0 寄存器读取数据。

- 重复步骤 2 直到 FIFO 为空。检查 uart.Channel_sts_reg0 [REMPTY]=1。

- 如果 Rx 超时中断状态位已置位,则清除它。向 Chnl_int_sts_reg0 [TIMEOUT] 写入 1。

示例:使用中断方法接收数据

- 启用中断。向 uart.Intrpt_en_reg0 [TIMEOUT] 和 uart.Intrpt_en_reg0 [RTRIG] 写入 1。

- 等待直到 RxFIFO 填充到触发电平或 Rx 超时。检查 uart.Chnl_int_sts_reg0 [RTRIG]=1 或 uart.Chnl_int_sts_reg0 [TIMEOUT]=1。

- 从 RxFIFO 读取数据。从 uart.TX_RX_FIFO0 寄存器读取数据。

- 重复步骤 2 和 3 直到 FIFO 为空。检查 uart.Channel_sts_reg0 [REMPTY]=1。

- 如果中断状态位已置位,则清除它们。向 Chnl_int_sts_reg0 [TIMEOUT] 或 Chnl_int_sts_reg0 [RTRIG] 写入 1。

19.3.5 RxFIFO 触发电平中断

示例:设置 RxFIFO 触发电平并启用中断 Intrpt_en_reg0 寄存器有位用于启用中断掩码,Intrpt_dis_reg0 有位用于强制禁用中断。每对位应互斥设置(即一个寄存器的某位置 1,另一个寄存器的同位置 0):

- Intrpt_en_reg0:只写,启用中断位。

- Intrpt_dis_reg0:只写,强制禁用中断位。

- 编程触发电平。写入 6 位字段 uart.Rcvr_FIFO_trigger_level0 [RTRIG]。

- 启用 RTRIG 中断。设置使能位,清除禁用位,并验证掩码值: a. 设置 uart.Intrpt_en_reg0 [RTRIG]=1。 b. 清除 uart.Intrpt_dis_reg0 [RTRIG]=0。 c. uart.intrpt_mask_reg0 [RTRIG] 读回 = 1(已启用中断)。

- 禁用 RTRIG 中断。设置禁用位,清除使能位,并验证掩码值: a. 设置 uart.Intrpt_dis_reg0 [RTRIG]=1。 b. 清除 uart.Intrp_en_reg0 [RTRIG]=0。 c. uart.intrpt_mask_reg0 [RTRIG] 读回 = 0(已禁用中断)。

- 清除 RTRIG 中断。向 uart.Intrpt_dis_reg0 [RTRIG] 位字段写入 1。

当一个中断的使能位和禁用位都被设置时,该中断被禁用。

通过读取 uart.Intrpt_mask_reg0 寄存器可以确定中断启用 / 禁用机制的状态。如果掩码位 = 1,则中断已启用。

19.3.6 寄存器概述

UART 寄存器的概述如表 19-3 所示。详细信息在附录 B 寄存器详情中提供。

表 19-3:UART 寄存器概述

| 功能 | uart. 寄存器名称概述 |

|---|---|

| 配置 | Control_reg0、mode_reg0、Baud_rate_gen_reg0、Baud_rate_divider_reg0(配置模式和波特率) |

| 中断处理 | Intrpt_en_reg0、Intrpt_dis_reg0、Intrpt_mask_reg0、Chnl_int_sts_reg0、Channel_sts_reg0(启用 / 禁用中断掩码、通道中断状态、通道状态) |

| Rx 和 Tx 数据 | TX_RX_FIFO0(读取接收的数据,写入要发送的数据) |

| 接收器 | Rcvr_timeout_reg0、Rcvr_FIFO_trigger_level0(配置接收器超时和 RxFIFO 触发电平值) |

| 发送器 | Tx_FIFO_trigger_level0(配置 TxFIFO 触发电平值) |

| 调制解调器 | Modem_ctrl_reg0、Modem_sts_reg0、Flow_delay_reg0(配置类调制解调器应用) |

19.4 系统功能

19.4.1 时钟

控制器和 I/O 接口由参考时钟(UART_REF_CLK)驱动。控制器的互连还需要 APB 接口时钟(CPU_1x)。这两种时钟均来自 PS 时钟子系统。

CPU_1x 时钟 有关一般时钟编程信息,请参见 25.2 节 CPU 时钟。CPU_1x 时钟与 UART 参考时钟异步运行。

参考时钟 PS 时钟子系统中参考时钟的生成由 slcr.UART_CLK_CTRL 寄存器控制。该寄存器可以选择时钟所源自的 PLL,并设置分频频率。该寄存器还控制每个 UART 控制器的时钟使能。UART 参考时钟的生成在 25.6.3 节 SDIO、SMC、SPI、Quad-SPI 和 UART 时钟中描述。

操作限制 注意:时钟操作限制在 19.1.3 节注意事项中描述。

示例:配置参考时钟 时钟可以基于 PS 时钟子系统中的任何 PLL。在本示例中,I/O PLL 使用 1000 MHz 时钟,时钟分频器为 0x14,为 UART 控制器生成 50 MHz 时钟。

- 编程 UART 参考时钟。向 slcr.UART_CLK_CTRL 寄存器写入 0x0000_1401: a. 时钟分频器,slcr.UART_CLK_CTRL [DIVISOR]=0x14。 b. 选择 IO PLL,slcr.UART_CLK_CTRL [SRCSEL]=0。 c. 启用 UART 0 参考时钟,slcr.UART_CLK_CTRL [CLKACT0]=1。 d. 禁用 UART 1 参考时钟,slcr.UART_CLK_CTRL [CLKACT1] 位 = 0。

19.4.2 复位

控制器复位位由 PS 生成,参见第 26 章复位系统。

示例:控制器复位

- 选项 1:断言控制器复位:设置 slcr.UART_RST_CTRL [UARTx_REF_RST、UARTx_CPU1X_RST] 位 = 1。

- 选项 2:撤销控制器复位:清除 slcr.UART_RST_CTRL [UARTx_REF_RST、UARTx_CPU1X_RST] 位 = 0。

19.5 I/O 接口

19.5.1 MIO 编程

UART 的 RxD 和 TxD 信号可路由到多个 MIO 引脚组中的一组或 EMIO 接口。所有调制解调器流控制信号始终路由到 EMIO 接口,在 MIO 引脚上不可用。所有 UART 信号列于表 19-4 中。RxD 和 TxD 信号的路由在 2.4 节 PS-PL 电压电平转换器使能中描述。

示例:将 UART 0 RxD/TxD 信号路由到 MIO 引脚 46、47 在本示例中,UART 0 的 RxD 和 TxD 信号通过 MIO 引脚 46 和 47 路由。还有许多其他引脚选项可用。

- 配置 MIO 引脚 46 用于 RxD 信号。向 slcr.MIO_PIN_46 寄存器写入 0x0000_12E1: a. 将 UART 0 RxD 信号路由到引脚 46。 b. 输出禁用(设置 TRI_ENABLE=1)。 c. LVCMOS18(其他电压选项参见寄存器定义)。 d. 慢 CMOS 边沿(良性设置)。 e. 启用内部上拉电阻。 f. 禁用 HSTL 接收器。

- 配置 MIO 引脚 47 用于 TxD 信号。向 slcr.MIO_PIN_47 寄存器写入 0x0000_12E0: a. 将 UART 0 TxD 信号路由到引脚 47。 b. 三态由 UART 控制(TRI_ENABLE=0)。 c. LVCMOS18(其他电压选项参见寄存器定义)。 d. 慢 CMOS 驱动边沿。 e. 启用内部上拉电阻。 f. 禁用 HSTL 接收器。

19.5.2 MIO-EMIO 信号

UART I/O 信号在表 19-4 中标识。基于器件版本的 MIO 引脚和任何限制在 2.5.4 节 MIO 概览表中显示。

表 19-4:UART MIO 引脚和 EMIO 信号

| UART 接口信号 | 默认控制器输入值 | MIO 引脚编号 | I/O | EMIO 信号 | I/O |

|---|---|---|---|---|---|

| UART 0 发送 | ~ | 11、15、19、23、27、31、35、39、43、47、51 | O | EMIOUART0TX | O |

| UART 0 接收 | 10、14、18、22、26、30、34、38、42、46、50 | I | EMIOUART0RX | I | |

| UART 0 清除发送 | ~ | ~ | EMIOUART0CTSN | I | |

| UART 0 准备发送 | ~ | ~ | ~ | EMIOUART0RTSN | O |

| UART 0 数据设备就绪 | ~ | ~ | EMIOUART0DSRN | I | |

| UART 0 数据载波检测 | ~ | ~ | EMIOUART0DCDN | I | |

| UART 0 振铃指示 | ~ | ~ | EMIOUART0RIN | I | |

| UART 0 数据终端就绪 | ~ | ~ | ~ | EMIOUART0DTRN | O |

| UART 1 发送 | ~ | 8、12、16、20、24、28、32、36、40、44、48、52 | O | EMIOUART1TX | O |

| UART 1 接收 | 9、13、17、21、25、29、33、37、41、45、49、53 | I | EMIOUART1RX | I | |

| UART 1 清除发送 | ~ | ~ | EMIOUART1CTSN | I | |

| UART 1 准备发送 | ~ | ~ | ~ | EMIOUART1RTSN | O |

| UART 1 数据设备就绪 | ~ | ~ | EMIOUART1DSRN | I | |

| UART 1 数据载波检测 | ~ | ~ | EMIOUART1DCDN | I | |

| UART 1 振铃指示 | ~ | ~ | EMIOUART1RIN | I | |

| UART 1 数据终端就绪 | ~ | ~ | ~ | EMIOUART1DTRN | O |

Zynq-7000 AP SoC 技术参考手册 UG585(v1.11)2016 年 9 月 27 日

详细总结

1. UART 控制器简介

- 定义:UART 控制器是全双工异步收发控制器,用于设备间串行通信,ZYNQ/MPSoC 内部包含两个 UART 控制器(UART0 和 UART1)。

- 核心特性

- 波特率:支持可编程波特率发生器,可根据需求设置通信速率。

- 数据格式:数据位可配置为 6bit、7bit、8bit;校验位可配置为奇、偶、空格、标记、无校验;停止位可配置为 1bit、1.5bit、2bit。

- 错误检测:支持奇偶校验错误、帧错误、溢出错误检测。

- 环回模式:包括正常模式、自动回音模式、本地环回模式、远程环回模式。

- 中断支持:支持接收 FIFO 达阈值、接收超时等多种状态触发中断。

- 系统视图:包含 IRQ ID# {59, 82}、MIO-EMIO 路由、UART 接口控制器、UART REF_RST、UART REF_CLK、Tx/Rx、PS Slave APB Pins、CPU_1x 时钟等元素,展示了 UART 控制器与其他模块的连接关系。

- 系统框图:涵盖波特率发生器、收发器、TxFIFO、RxFIFO、中断控制器、EMIO 接口、调制解调器信号(CTS、RTS 等)等模块,体现 UART 的整体工作架构。

- FIFO 功能

- Transmit FIFO:64 字节,存储从 APB 接口写入的数据,直至被发送器读出并加载到移位寄存器;用户通过写 TxFIFO 寄存器写入数据,支持溢出中断(TOVR)、满中断(TFUL)、近满中断(TNFUL)、触发中断(TTRIG)、空中断(TEMPTY)。

- Receiver FIFO:64 字节,存储从移位寄存器接收的数据,直至被 APB 接口读出;用户通过读 RxFIFO 寄存器读出数据,支持溢出中断(ROVR)、满中断(RFUL)、触发中断(RTRIG)、空中断(REMPTY)。

- I/O 模式切换:通过模式开关控制 RxD 和 TxD 信号路由,四种模式如下表:

| 模式 | 特点 |

|---|---|

| 正常模式 | 用于标准 UART 操作 |

| 自动回音模式 | RxD 接收数据,路由至接收器和 TxD 引脚,发送器数据无法输出 |

| 本地环回模式 | 不连接 RxD/TxD 引脚,发送数据回环至接收器 |

| 远程环回模式 | RxD 信号连接 TxD 信号,无法发送 / 接收数据 |

2. UART 原理图介绍

以领航者 / 启明星为例,USB UART 原理图包含 CH340C 芯片(实现 USB 转 UART 功能)、电容(C57、C58 等)、电阻(R91、R93 等)、USB Type-C 接口等元件,展示了 UART 信号与 USB 接口的硬件连接关系,其中 CH340C 的 TXD、RXD 分别与 UART1 的 TXD、RXD 等信号连接。

3. 实验任务

使用 UART 控制器完成串口中断数据环回功能,即通过中断机制实现接收数据后环回发送。

4. 硬件设计

- ZYNQ 系统框图:包含 ARM Cortex-A9 处理器、DDR3 内存控制器、MIO 接口、UART 控制器,UART 通过 MIO 连接至 USB_UART 模块,实现与外部设备的通信。

- MPSoC 系统框图:包含 ARM Cortex-A53 处理器、DDR4 内存控制器、MIO 接口、UART 控制器,UART 通过 MIO 连接至 USB_UART 模块,架构与 ZYNQ 类似但处理器和内存类型不同。

5. 软件设计

围绕 UART 串口中断实验展开,涉及 UART 控制器的初始化、中断配置、数据收发处理等软件实现细节,以完成中断数据环回功能。

6. 课堂总结

对 UART 串口中断实验的关键知识点、实验要点等进行总结回顾。

关键问题

问题:UART 控制器有哪些核心特性?这些特性如何提升其适用性?

答案:UART 控制器的核心特性包括:①可编程波特率,支持灵活设置通信速率;②可配置数据位(6-8bit)、校验位(奇 / 偶 / 无等)、停止位(1/1.5/2bit),适配不同通信协议;③支持奇偶校验、帧错误、溢出错误检测,提升数据传输可靠性;④多种环回模式,便于调试;⑤支持多种中断触发,适合中断驱动的通信场景。这些特性使其能适应不同设备和通信需求,增强了通用性和可靠性。问题:Transmit FIFO 和 Receiver FIFO 的作用是什么?它们支持哪些中断类型?

答案:Transmit FIFO(64 字节)用于存储从 APB 接口写入的数据,直至被发送器读出加载到移位寄存器,支持溢出中断(TOVR)、满中断(TFUL)、近满中断(TNFUL)、触发中断(TTRIG)、空中断(TEMPTY)。Receiver FIFO(64 字节)用于存储从移位寄存器接收的数据,直至被 APB 接口读出,支持溢出中断(ROVR)、满中断(RFUL)、触发中断(RTRIG)、空中断(REMPTY)。FIFO 的存在减少了 CPU 频繁干预,中断机制可及时通知 CPU 处理数据,提升通信效率。问题:本次实验的任务是什么?实现该任务的硬件基础是什么?

答案:本次实验任务是使用 UART 控制器完成串口中断数据环回功能。硬件基础包括:ZYNQ/MPSoC 内部的 UART 控制器(UART0 或 UART1)、MIO 接口(用于 UART 信号路由)、USB_UART 模块(含 CH340C 等元件,实现 USB 与 UART 信号转换)、DDR 内存(用于数据缓存)等,通过这些硬件模块的协同工作,为中断数据环回提供物理支持。

以下是基于文档内容实现的 UART 控制器 C 语言代码,涵盖初始化、收发(轮询 / 中断)、模式切换等核心功能,并包含详细注释:

UART 控制器驱动代码(基于 Zynq-7000 系列)

/*************************************************************************** 头文件与寄存器地址定义* 参考文档:Zynq-7000 AP SoC Technical Reference Manual (UG585) Chapter 19**************************************************************************/

#include <stdint.h>// UART0基地址(根据实际硬件调整)

#define UART0_BASE_ADDR 0xE0000000

// UART1基地址

#define UART1_BASE_ADDR 0xE0001000// 寄存器偏移量(文档19.3.6节寄存器概述)

#define UART_CTRL_REG0 0x00 // 控制寄存器

#define UART_MODE_REG0 0x04 // 模式寄存器

#define UART_BAUD_GEN_REG0 0x08 // 波特率发生器寄存器

#define UART_BAUD_DIV_REG0 0x0C // 波特率分频寄存器

#define UART_TX_RX_FIFO0 0x10 // 收发FIFO寄存器

#define UART_CHNL_INT_STS0 0x14 // 通道中断状态寄存器

#define UART_CHNL_STS0 0x18 // 通道状态寄存器

#define UART_INTRPT_EN0 0x1C // 中断使能寄存器

#define UART_INTRPT_DIS0 0x20 // 中断禁用寄存器

#define UART_INTRPT_MASK0 0x24 // 中断掩码寄存器

#define UART_RCVR_TIMEOUT0 0x28 // 接收超时寄存器

#define UART_RCVR_TRIG0 0x2C // 接收FIFO触发寄存器

#define UART_TX_TRIG0 0x30 // 发送FIFO触发寄存器

#define UART_MODEM_CTRL0 0x34 // 调制解调器控制寄存器

#define UART_MODEM_STS0 0x38 // 调制解调器状态寄存器

#define UART_FLOW_DELAY0 0x3C // 流延迟寄存器// 寄存器指针定义

#define UART_REG(base, offset) (*(volatile uint32_t*)(base + offset))// 控制寄存器位定义(文档19.2.2节)

#define UART_CTRL_RXEN (1 << 0) // 接收使能

#define UART_CTRL_RXDIS (1 << 1) // 接收禁用

#define UART_CTRL_TXEN (1 << 2) // 发送使能

#define UART_CTRL_TXDIS (1 << 3) // 发送禁用

#define UART_CTRL_TXRST (1 << 4) // 发送软复位

#define UART_CTRL_RXRST (1 << 5) // 接收软复位

#define UART_CTRL_RSTTO (1 << 6) // 接收超时计数器复位

#define UART_CTRL_STTBRK (1 << 7) // 开始发送中断

#define UART_CTRL_STPBRK (1 << 8) // 停止发送中断// 模式寄存器位定义(文档19.2.2节)

#define UART_MODE_CLKS (1 << 0) // 时钟选择(0:uart_ref_clk,1:uart_ref_clk/8)

#define UART_MODE_CHRL_6 (0 << 1) // 6数据位

#define UART_MODE_CHRL_7 (1 << 1) // 7数据位

#define UART_MODE_CHRL_8 (2 << 1) // 8数据位(bit1-2)

#define UART_MODE_PAR_NONE (4 << 3) // 无校验(bit3-5)

#define UART_MODE_PAR_ODD (5 << 3) // 奇校验

#define UART_MODE_PAR_EVEN (6 << 3) // 偶校验

#define UART_MODE_NBSTOP_1 (0 << 6) // 1停止位(bit6-7)

#define UART_MODE_NBSTOP_2 (2 << 6) // 2停止位

#define UART_MODE_CHMODE_NORMAL (0 << 8) // 正常模式(bit8-9)

#define UART_MODE_CHMODE_ECHO (1 << 8) // 自动回显模式

#define UART_MODE_CHMODE_LOOPBACK (2 << 8) // 本地环回模式

#define UART_MODE_CHMODE_REMOTE (3 << 8) // 远程环回模式// 中断状态位定义(文档19.2.10节表19-2)

#define UART_INT_RTRIG (1 << 0) // 接收FIFO触发

#define UART_INT_REMPTY (1 << 1) // 接收FIFO空

#define UART_INT_RFUL (1 << 2) // 接收FIFO满

#define UART_INT_TEMPTY (1 << 3) // 发送FIFO空

#define UART_INT_TFUL (1 << 4) // 发送FIFO满

#define UART_INT_ROVR (1 << 5) // 接收溢出

#define UART_INT_FRAME (1 << 6) // 帧错误

#define UART_INT_PARE (1 << 7) // 奇偶校验错误

#define UART_INT_TIMEOUT (1 << 8) // 接收超时

#define UART_INT_DMSI (1 << 9) // 调制解调器信号变化

#define UART_INT_TTRIG (1 << 10) // 发送FIFO触发

#define UART_INT_TNFUL (1 << 11) // 发送FIFO近满

#define UART_INT_TOVR (1 << 12) // 发送溢出/*************************************************************************** 波特率计算函数* 公式参考文档19.2.3节:baud_rate = sel_clk / (CD * (BDIV + 1))* 输入:目标波特率、参考时钟频率(Hz)、是否使用clk/8分频* 输出:CD和BDIV值(通过指针返回)**************************************************************************/

void uart_calc_baud(uint32_t baud_rate, uint32_t ref_clk, uint8_t use_div8, uint16_t *cd, uint8_t *bdiv) {uint32_t sel_clk = use_div8 ? (ref_clk / 8) : ref_clk;// 文档推荐BDIV范围4-255,默认15(16倍过采样)*bdiv = 15; // 初始值,可根据误差调整*cd = sel_clk / (baud_rate * (*bdiv + 1));// 误差修正(若计算值与实际值偏差大,可调整BDIV)uint32_t actual_baud = sel_clk / (*cd * (*bdiv + 1));if (actual_baud > baud_rate + 10 || actual_baud < baud_rate - 10) {// 尝试其他BDIV值减小误差(参考文档表19-1示例)for (*bdiv = 4; *bdiv <= 255; (*bdiv)++) {*cd = sel_clk / (baud_rate * (*bdiv + 1));actual_baud = sel_clk / (*cd * (*bdiv + 1));if (actual_baud >= baud_rate - 5 && actual_baud <= baud_rate + 5) {break;}}}

}/*************************************************************************** UART初始化函数* 功能:配置数据格式、波特率、FIFO触发、中断等* 参数:* base_addr:UART基地址(UART0_BASE_ADDR/UART1_BASE_ADDR)* baud_rate:目标波特率(如115200)* ref_clk:参考时钟频率(如50MHz)**************************************************************************/

void uart_init(uint32_t base_addr, uint32_t baud_rate, uint32_t ref_clk) {// 1. 复位控制器(文档19.4.2节)UART_REG(base_addr, UART_CTRL_REG0) = UART_CTRL_RXDIS | UART_CTRL_TXDIS;UART_REG(base_addr, UART_CTRL_REG0) |= UART_CTRL_TXRST | UART_CTRL_RXRST;while (UART_REG(base_addr, UART_CTRL_REG0) & (UART_CTRL_TXRST | UART_CTRL_RXRST));// 2. 配置模式寄存器(8数据位、1停止位、无校验、正常模式)uint32_t mode = 0;mode |= UART_MODE_CHRL_8; // 8数据位mode |= UART_MODE_PAR_NONE; // 无校验mode |= UART_MODE_NBSTOP_1; // 1停止位mode |= UART_MODE_CHMODE_NORMAL;// 正常模式mode &= ~UART_MODE_CLKS; // 使用uart_ref_clk(不除以8)UART_REG(base_addr, UART_MODE_REG0) = mode;// 3. 配置波特率(文档19.2.3节)uint16_t cd;uint8_t bdiv;uart_calc_baud(baud_rate, ref_clk, 0, &cd, &bdiv);// 写入前必须禁用收发器(文档19.2.3节IMPORTANT)UART_REG(base_addr, UART_BAUD_GEN_REG0) = cd; // 写入CD值UART_REG(base_addr, UART_BAUD_DIV_REG0) = bdiv; // 写入BDIV值// 4. 配置FIFO触发阈值(接收FIFO满16字节触发中断,发送FIFO空触发)UART_REG(base_addr, UART_RCVR_TRIG0) = 16; // 接收触发阈值16字节(1-63)UART_REG(base_addr, UART_TX_TRIG0) = 0; // 发送空触发// 5. 配置中断(启用接收触发、发送空、错误中断)UART_REG(base_addr, UART_INTRPT_DIS0) = 0xFFFFFFFF; // 先禁用所有中断UART_REG(base_addr, UART_INTRPT_EN0) = UART_INT_RTRIG | UART_INT_TEMPTY | UART_INT_ROVR | UART_INT_FRAME | UART_INT_PARE;// 6. 启用收发器UART_REG(base_addr, UART_CTRL_REG0) = UART_CTRL_RXEN | UART_CTRL_TXEN | UART_CTRL_RSTTO;

}/*************************************************************************** 轮询方式发送字节* 参数:* base_addr:UART基地址* data:待发送字节**************************************************************************/

void uart_poll_send_byte(uint32_t base_addr, uint8_t data) {// 等待发送FIFO非满(文档19.2.4节TFUL位)while (UART_REG(base_addr, UART_CHNL_STS0) & UART_INT_TFUL);// 写入FIFOUART_REG(base_addr, UART_TX_RX_FIFO0) = data;

}/*************************************************************************** 轮询方式发送字符串* 参数:* base_addr:UART基地址* str:以'\0'结尾的字符串**************************************************************************/

void uart_poll_send_str(uint32_t base_addr, const char *str) {while (*str != '\0') {uart_poll_send_byte(base_addr, (uint8_t)*str);str++;}

}/*************************************************************************** 轮询方式接收字节(带超时)* 参数:* base_addr:UART基地址* data:接收数据指针* timeout:超时计数(循环次数)* 返回:0=成功,1=超时,2=错误**************************************************************************/

uint8_t uart_poll_recv_byte(uint32_t base_addr, uint8_t *data, uint32_t timeout) {// 检查错误状态(文档19.2.7节)uint32_t int_sts = UART_REG(base_addr, UART_CHNL_INT_STS0);if (int_sts & (UART_INT_ROVR | UART_INT_FRAME | UART_INT_PARE)) {// 清除错误标志(写1清除)UART_REG(base_addr, UART_CHNL_INT_STS0) = int_sts & (UART_INT_ROVR | UART_INT_FRAME | UART_INT_PARE);return 2; // 错误}// 等待接收FIFO非空(文档19.2.6节REMPTY位)while (!(UART_REG(base_addr, UART_CHNL_STS0) & UART_INT_REMPTY)) {if (timeout-- == 0) {return 1; // 超时}}// 读取数据*data = UART_REG(base_addr, UART_TX_RX_FIFO0) & 0xFF;return 0; // 成功

}/*************************************************************************** 中断方式发送初始化(配置发送空中断)**************************************************************************/

void uart_int_send_init(uint32_t base_addr) {// 启用发送FIFO空中断UART_REG(base_addr, UART_INTRPT_EN0) |= UART_INT_TEMPTY;UART_REG(base_addr, UART_INTRPT_DIS0) &= ~UART_INT_TEMPTY;

}/*************************************************************************** 中断服务程序(发送部分)* 功能:当发送FIFO空时,填充数据**************************************************************************/

void uart_int_send_isr(uint32_t base_addr, const uint8_t *buf, uint32_t len) {static uint32_t send_idx = 0;if (UART_REG(base_addr, UART_CHNL_INT_STS0) & UART_INT_TEMPTY) {// 填充FIFO直到满或数据发送完毕while (send_idx < len && !(UART_REG(base_addr, UART_CHNL_STS0) & UART_INT_TFUL)) {UART_REG(base_addr, UART_TX_RX_FIFO0) = buf[send_idx++];}// 数据发送完毕,禁用发送中断if (send_idx >= len) {UART_REG(base_addr, UART_INTRPT_DIS0) |= UART_INT_TEMPTY;send_idx = 0; // 重置索引}// 清除中断标志UART_REG(base_addr, UART_CHNL_INT_STS0) = UART_INT_TEMPTY;}

}/*************************************************************************** 中断方式接收初始化(配置接收触发中断)**************************************************************************/

void uart_int_recv_init(uint32_t base_addr) {// 启用接收FIFO触发中断UART_REG(base_addr, UART_INTRPT_EN0) |= UART_INT_RTRIG;UART_REG(base_addr, UART_INTRPT_DIS0) &= ~UART_INT_RTRIG;

}/*************************************************************************** 中断服务程序(接收部分)* 功能:当接收FIFO达到触发阈值时,读取数据**************************************************************************/

void uart_int_recv_isr(uint32_t base_addr, uint8_t *buf, uint32_t *recv_len) {if (UART_REG(base_addr, UART_CHNL_INT_STS0) & UART_INT_RTRIG) {// 读取FIFO直到空while (!(UART_REG(base_addr, UART_CHNL_STS0) & UART_INT_REMPTY)) {buf[*recv_len] = UART_REG(base_addr, UART_TX_RX_FIFO0) & 0xFF;(*recv_len)++;}// 清除中断标志UART_REG(base_addr, UART_CHNL_INT_STS0) = UART_INT_RTRIG;}

}/*************************************************************************** 配置UART模式(正常/回显/环回)* 参数:* base_addr:UART基地址* mode:0=正常,1=自动回显,2=本地环回,3=远程环回**************************************************************************/

void uart_set_mode(uint32_t base_addr, uint8_t mode) {uint32_t curr_mode = UART_REG(base_addr, UART_MODE_REG0);// 清除原模式位curr_mode &= ~(0x3 << 8);// 设置新模式(文档19.2.8节)switch (mode) {case 0:curr_mode |= UART_MODE_CHMODE_NORMAL;break;case 1:curr_mode |= UART_MODE_CHMODE_ECHO;break;case 2:curr_mode |= UART_MODE_CHMODE_LOOPBACK;break;case 3:curr_mode |= UART_MODE_CHMODE_REMOTE;break;default:return;}UART_REG(base_addr, UART_MODE_REG0) = curr_mode;

}/*************************************************************************** 配置自动流控制(文档19.2.11节)* 参数:* base_addr:UART基地址* rts_trigger:RTS信号撤销的RxFIFO阈值(如32)**************************************************************************/

void uart_enable_auto_flowctrl(uint32_t base_addr, uint8_t rts_trigger) {// 设置RTS触发阈值(FDEL字段)UART_REG(base_addr, UART_FLOW_DELAY0) = rts_trigger;// 启用自动流控制(FCM位)UART_REG(base_addr, UART_MODEM_CTRL0) |= (1 << 0);// 等待模式切换完成while (!(UART_REG(base_addr, UART_MODEM_STS0) & (1 << 0)));

}/*************************************************************************** 主函数示例**************************************************************************/

int main() {// 初始化UART0(50MHz参考时钟,115200波特率)uart_init(UART0_BASE_ADDR, 115200, 50000000);// 测试轮询发送uart_poll_send_str(UART0_BASE_ADDR, "UART Poll Test: Hello World!\r\n");// 测试模式切换(本地环回模式,自发自收)uart_set_mode(UART0_BASE_ADDR, 2); // 本地环回uart_poll_send_byte(UART0_BASE_ADDR, 0xAA);uint8_t recv_data;uart_poll_recv_byte(UART0_BASE_ADDR, &recv_data, 100000); // 应收到0xAAuart_set_mode(UART0_BASE_ADDR, 0); // 恢复正常模式// 初始化中断收发uint8_t send_buf[] = "UART Interrupt Test: Hello Interrupt!\r\n";uint8_t recv_buf[128];uint32_t recv_len = 0;uart_int_send_init(UART0_BASE_ADDR);uart_int_recv_init(UART0_BASE_ADDR);while (1) {// 触发发送中断(实际应在中断中处理)uart_int_send_isr(UART0_BASE_ADDR, send_buf, sizeof(send_buf)-1);// 处理接收中断(实际应在中断中处理)uart_int_recv_isr(UART0_BASE_ADDR, recv_buf, &recv_len);}return 0;

}代码说明

- 寄存器定义:严格按照文档 19.3.6 节寄存器地址和位功能定义,确保与硬件匹配。

- 初始化流程:遵循文档 19.3.1 节启动序列,包括复位、模式配置、波特率计算(参考 19.2.3 节公式)、FIFO 设置等。

- 多种收发方式:

- 轮询方式:通过查询 FIFO 状态位(如 TFUL、REMPTY)实现,适合简单场景。

- 中断方式:配置中断使能寄存器,在 ISR 中处理收发,适合高实时性场景。

- 模式切换:支持正常、自动回显、本地环回、远程环回四种模式(文档 19.2.8 节)。

- 流控制:实现自动流控制配置(文档 19.2.11 节),通过 RTS 信号控制数据流入。

- 错误处理:检查并清除溢出、帧错误、奇偶校验错误等状态(文档 19.2.7 节)。

使用时需根据实际硬件调整基地址和参考时钟频率,中断服务程序需结合具体 RTOS 或裸机中断控制器配置。