单片机ADC采集机理层面详细分析(二)

文章目录

- 二、ADC采样原理

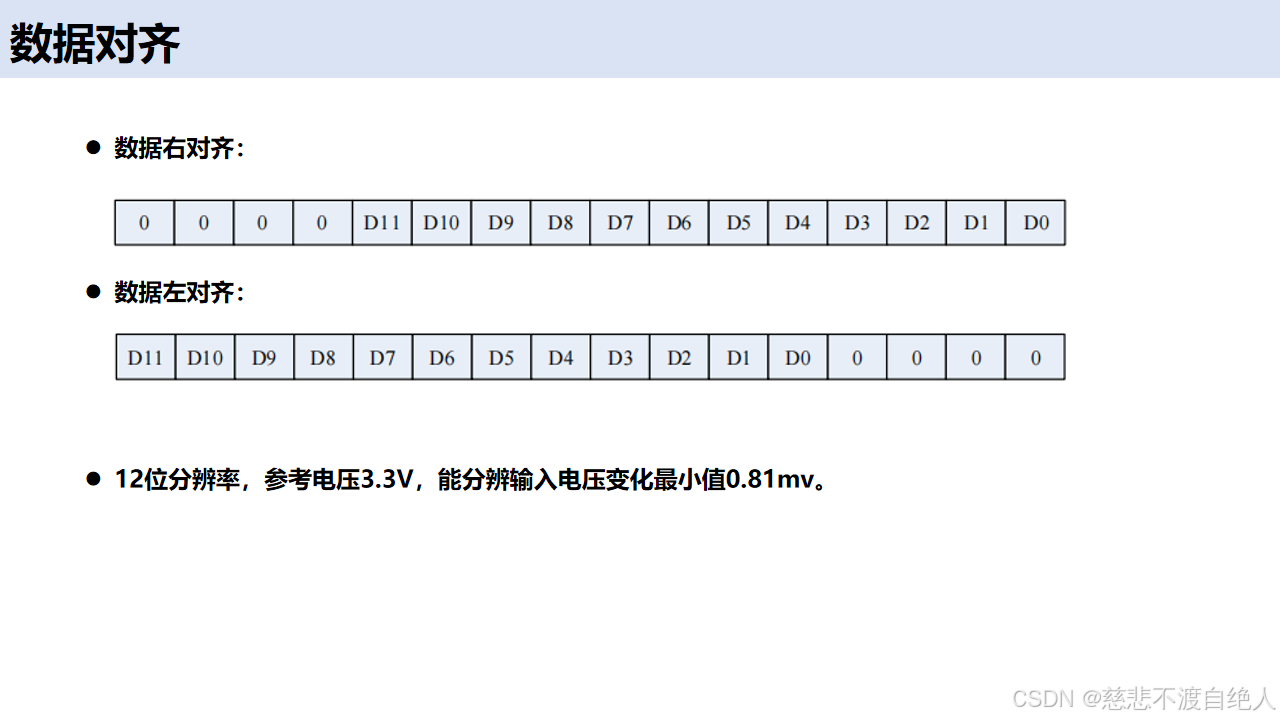

- 2.1 数据对齐

- 2.2 采样原理

- 2.2.1 采样频率对精度影响分析

- ADC低时钟频率

- ADC高时钟频率

- 关于误差的一点好奇

- 2.2.2 能否采样电流

- 2.3 采样原理详细分析

二、ADC采样原理

2.1 数据对齐

针对GD32F303分析,对于规则组:

将转换的数据可以在寄存器中配置为右对齐或者左对齐,就是将没有填充的数据填充0。右对齐就是高位补充为0,这是因为数据最先存放的位置就是低位,那么数据没有那么多,就只能填充0。同理左对齐就是低位补充为0,原理也是如此。

在日常开发中通常使用的都是规则组转换,数据右对齐。

这里其实有一个疑问就是左对齐和右对齐有什么区别吗?或者说应该在什么应用场景应用什么对齐方式?

-

先说左对齐,因为我相信大多数情况下都是使用右对齐,对应的左对齐就是少数,那么我们就先分析什么时候使用左对齐。

-

左对齐:适合高性能应用(如实时控制、过采样),或需高效数据截断的场景。

-

例如:

-

高位数据快速访问:适用于需要快速比较或阈值判断的场景。例如,若设定阈值为满量程的50%,左对齐时可直接比较寄存器高8位(如

0x80代表2048),无需读取完整12位数据。 -

兼容8位系统:在8位总线或外设(如某些DAC)中,可直接使用寄存器高字节作为有效数据,减少数据传输量。

-

简化高分辨率应用:若后续使用过采样技术(如16位精度),左对齐可为高位扩展预留空间。

-

| 场景 | 推荐对齐方式 | 原因 |

|---|---|---|

| 常规电压测量 | 右对齐 | 直接获取0~4095的原始值,计算电压更直观。 |

| 高速阈值比较(如看门狗) | 左对齐 | 直接比较寄存器高8位,减少实时计算开销。 |

| 过采样至16位精度 | 左对齐 | 保留高位空间,便于累加和移位操作。 |

| 8位数据总线通信 | 左对齐 | 高字节即为有效数据,无需额外处理。 |

- 右对齐:优先用于通用场景,简化代码逻辑,避免额外操作。

12位分辨率参考电压3.3V,能分辨输入电压变化最小值0.81mv。 针对这句话我们要详细分析一下:

3.3V/2^12=0.81mv 能分辨输入电压变化最小值。

因为是12位的分辨率,那就是说明有4095中可能,因此就是3.3V除以4095可能,得到的就是每一种可能表示的最小电压,这就是模数转化,将模拟信号转换为数组信号。

为什么是4095不是4096这是因为12位的分辨率表示的是0~4095,因此就只能使用4095这个数作为除数。

分辨率的大小,就是代表了ADC的精度,分辨率越高,就意味着能识别的最小电压是多少,也就是说一些微弱的电压都能被我们的ADC给采集到。

也就是之前在本科阶段,某一天晚上老师所讲的可能精度问题,曾经有一位学长做到了温度传感器很精准的温度读取,就是模拟信号转换为数字信号。

这个问题暂时先保留这,等接下来分析完以后再简单分析该问题。

2.2 采样原理

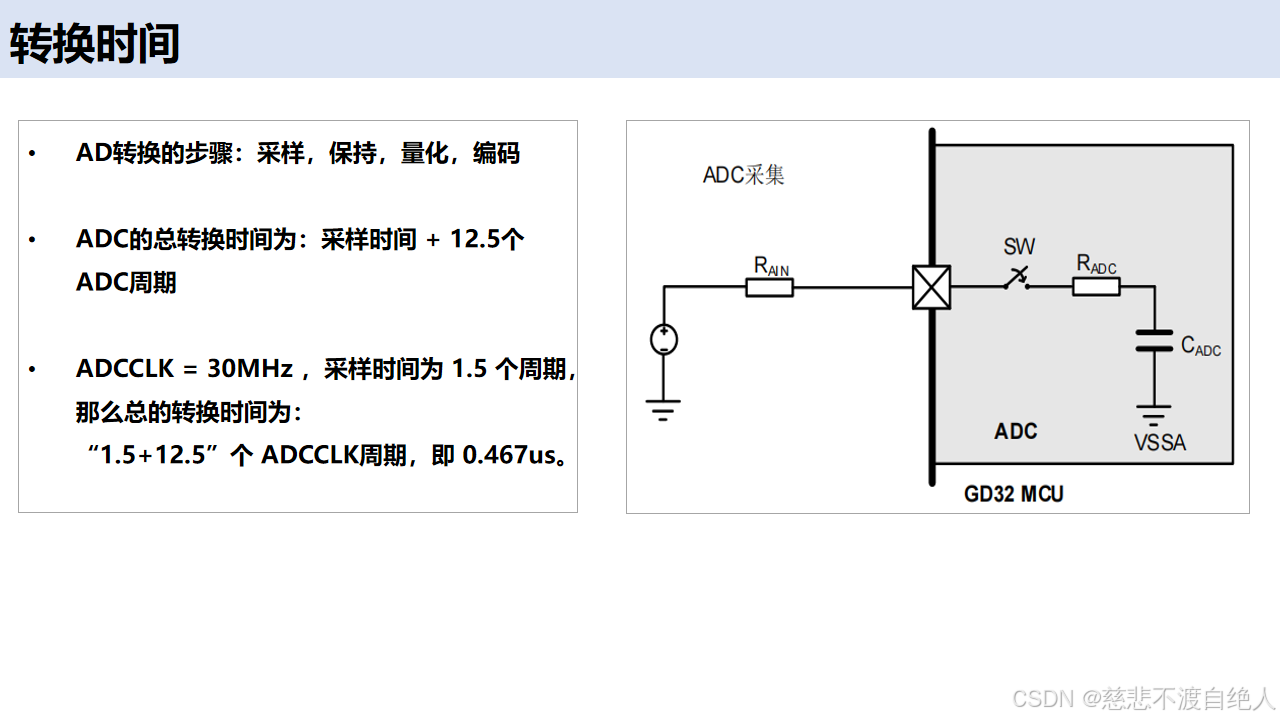

ADC有一个很重要的指标:转换时间。

ADC采样步骤:

-

1、采样

-

2、保持

-

3、量化

-

4、编码

ADC的总转换时间就是:采样时间+12.5个ADC周期

采样时间:可以理解为采样和保持步骤,采样时间是1.5个周期(GD32F303)。

12.5个ADC周期:可以理解为量化和编码步骤消耗的时间。

并且ADC的时钟频率(ADCCLK)需要从系统时钟树中单独配置,且其来源和分频方式会直接影响ADC的转换时间和精度。关于时钟树其实也只是知道概念,因为这个地方是芯片内部的暂时还是没有精力去研究明白。(留坑—时钟树解读)

-

若系统时钟为72MHz,选择6分频:ADCCLK = 72MHz / 6 = 12MHz。

-

若需更高ADCCLK(如30MHz),需降低分频比(如PCLK2=60MHz时选择2分频)或提升PCLK2频率。

关键限制:ADCCLK最大频率一般为14MHz(STM32F1系列),超频可能导致精度损失(如12位精度降至10位)。

而本文的GD32F303芯片的ADC频率ADCCLK 是30MHZ,根据该ADC时钟频率就可以算出一个ADC时钟周期是多少。结果是:(1/30MHZ)= (1/30)us

然后总的周期消耗是14周期,那么最终的时间就是(14/30)us=0.467us。

2.2.1 采样频率对精度影响分析

采样频率的又分为ADC低时钟频率频率和ADC时钟高频率。

ADC低时钟频率

低时钟频率通俗易懂,就是反应迟钝,这个很好理解,太慢了就会导致信号采集不到,从而丢失有效信息,并且还会使系统性能下降及噪声敏感度增加。

这里不做太多深入理解,只是针对部分影响做简要说明

1、采样率下降与实时性损失

-

转换时间延长

ADC总转换时间 Tconv=采样周期+12.5×TADCCLK。若ADCCLK过低(如1MHz),即使最短采样时间(1.5周期),单次转换也需14μs,采样率仅71kSPS,难以捕捉快速变化信号(如音频突变、传感器瞬态响应)。 -

多通道系统瓶颈

扫描模式下,N个通道总时间 Ttotal=N×Tconv。例如10通道采样时,若ADCCLK=1MHz,总延迟可达140μs,导致数据同步失效。

2、混叠失真与频谱污染

-

违反奈奎斯特采样定理

当采样率 fs<2fmax(信号最高频率)时,高频分量会混叠到低频带,造成信号畸变。例如,100kHz信号用150kSPS采样时,混叠分量会干扰真实频谱。 -

虚假信号生成

混叠效应在频谱中表现为非真实的低频谐波,导致误判。如电机振动监测中,高频噪声混叠可能被误诊为机械故障。

3、噪声敏感性增强

-

热噪声主导误差

低频采样时,转换时间延长,ADC内部热噪声积累更显著,降低有效位数(ENOB)。例如14位ADC在1MHz时钟下,ENOB可能降至10-11位。 -

电源噪声耦合

长转换周期使ADC更易受电源纹波及数字开关噪声影响,信噪比(SNR)下降。尤其在高精度传感器(如电子秤)中,噪声可能导致读数漂移。

4、系统级问题

-

动态响应迟滞

控制系统(如电机调速)依赖实时反馈。若ADC采样率不足,控制器无法及时响应扰动,引发振荡或失控。 -

资源利用率低下

为补偿低速ADC,常需启用过采样或软件滤波,增加CPU负载及功耗。在电池设备中,反而抵消了低采样率省电的优势。 -

高频信号细节丢失

对宽带信号(如RF直接采样),欠采样会丢失高频信息。例如在软件无线电(SDR)中,低采样率导致频谱分辨率不足,无法解调高频调制信号。

| 危害类型 | 发生场景 | 后果 | 优化方向 |

|---|---|---|---|

| 实时性损失 | 多通道扫描、高速控制 | 数据延迟、系统失稳 | 提升ADCCLK至芯片上限(如30MHz) |

| 混叠失真 | 宽带信号采集(>0.5f_s) | 频谱污染、误诊断 | 前置抗混叠滤波器(截止频率<0.5f_s) |

| 热噪声积累 | 高精度测量(温度/压力传感) | ENOB下降、读数漂移 | 缩短采样时间 + 硬件屏蔽 |

| 动态响应迟滞 | 电机控制、电源闭环 | 控制振荡、效率降低 | 定时器触发 + DMA传输 |

低频ADCCLK或采样率不足的危害是系统性的:实时性丧失引发控制失效,混叠效应导致频谱污染,热噪声积累降低精度,资源冲突拖累整体性能。优化需硬件(抗混叠滤波、时钟提升)与软件(动态配置、过采样)协同,在速度、精度、功耗间取得平衡。对于关键应用(医疗仪器、工业控制),始终优先满足奈奎斯特准则,避免低频采样成为系统瓶颈。

ADC高时钟频率

1、会造成:采样建立时间不足(核心原因)

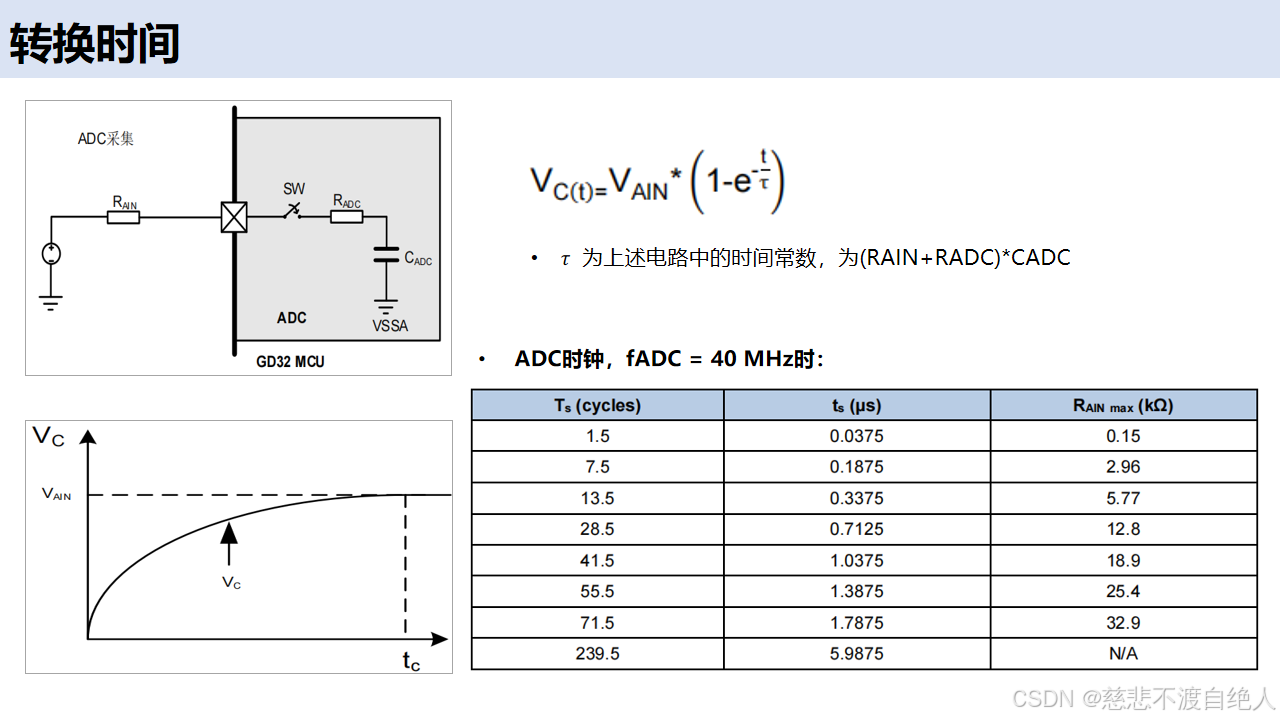

采样电容充电原理:ADC采样时,外部信号需通过输入阻抗(Rin)对内部采样电容(Csample)充电至稳定电压。充电时间常数 τ = Rin × Csample,需满足 t采样 ≥ 5τ 才能将误差控制在0.5LSB以内。《在数字电路技术基础》第五版,闫石主编 清华大学电子学教研组这本书中P545~546 有简单的说明。

高频时钟的压缩效应:ADCCLK频率升高时,每个采样周期的时间窗口缩短。若采样时间不足(如配置为1.5个周期),电容电压未稳定即进入量化阶段,导致采样值偏离真实电压,表现为增益误差或非线性失真。

-

ADCCLK = 30MHz 时,1.5周期时间 = 50ns → 勉强满足最小建立时间。

-

ADCCLK = 60MHz 时,1.5周期时间 = 25ns → 严重不足,误差可能超3LSB。

2、电源与参考电压噪声放大

-

瞬态电流冲击:高频转换时,ADC内部电容网络(如CDAC)在量化阶段频繁切换,瞬间抽取大电流(可达数十mA)。若电源响应延迟,导致VDD或VREF产生电压毛刺。

-

去耦电容失效:高频下电容的等效串联电感(ESL)形成阻抗,削弱高频噪声滤波能力。基准电压波动直接传递至比较器,引发DNL(微分非线性)误差。

案例:某12位ADC在30MHz ADCCLK下,VREF纹波需<0.5mV;若升至60MHz,相同去耦设计下纹波可能达2mV,导致ENOB从10.5位降至9位 。

3、时钟抖动(Jitter)的精度吞噬

-

采样时间不确定性:时钟边沿抖动(Δtjitter)会引入电压采样误差 ΔV = Vin × 2πfin × Δtjitter。输入信号频率(fin)越高,抖动影响越显著。

-

高频放大抖动效应:ADCCLK频率越高,相同相对抖动(如0.1%)对应的绝对时间抖动越小,但信号斜率要求更苛刻。例如:

- fin = 100kHz时,10ns抖动引入误差≈0.1%;

- fin = 1MHz时,相同抖动导致误差≈1%。

高频ADCCLK通过压缩时间窗口提升速度,但采样建立不足、电源噪声、时钟抖动三大物理限制会显著降低精度。优化需硬件设计(电源/去耦)、时钟质量、软件策略(过采样/动态配置) 多管齐下。实际设计时应根据信号带宽选择ADCCLK,而非盲目追求高频——速度提升是线性的,精度损失却可能是指数级的。

关于误差的一点好奇

最低有效位(LSB) 是定义分辨率和量化误差的核心参数。

LSB=满量程电压(FSR)2N\mathrm{LSB} = \frac{\text{满量程电压(FSR)}}{2^{N}} LSB=2N满量程电压(FSR)

12位 ADC,FSR = 5V 时

LSB=5V212=54096≈0.00122V=1.22mV\mathrm{LSB} = \frac{5\, \mathrm{V}}{2^{12}} = \frac{5}{4096} \approx 0.00122\, \mathrm{V} = 1.22\, \mathrm{mV} LSB=2125V=40965≈0.00122V=1.22mV

此时,ADC 可分辨的最小电压变化为 1.2mV,小于此值的电压变化无法被量化。

当模拟输入电压变化达到或超过 1 LSB 时,ADC 的输出数字码才会发生变化。这句话其实是不准确的,以下会说明:

假如LSB是1.22mV,但是我实际只有0.85mv,那不就是采集不到,或者识别不出来,这和将误差控制在0.5LSB有什么关系吗?

首先±0.5 LSB误差控制的本质含义:

-

定义:±0.5 LSB表示ADC的转换结果与真实模拟值之间的最大偏差不超过半个最小量化单位。

- 若LSB=1.22mV,则±0.5 LSB对应最大允许误差为±0.61mV。

-

目标:确保ADC的线性度和准确性,避免因非线性失真(如DNL、INL)导致转换结果系统性偏离。

-

关键指标:

-

DNL(微分非线性):相邻码的跳变点偏差需≤±0.5 LSB,否则会丢失某些编码(失码)。

-

INL(积分非线性):整体转换曲线与理想直线的偏差需≤±0.5 LSB,保证大范围测量的线性度。

-

示例:理想ADC在输入1.22mV时应输出码字1,实际ADC若误差为+0.5 LSB,则输出码字1的范围可能是0.61mV~1.83mV(仍能正确输出1)。相当于有了更多的冗余空间。

在ADC(模数转换器)中,误差控制在±0.5 LSB 是指ADC的转换精度(如DNL、INL等静态误差)被优化到最大偏差不超过0.5个最小量化单位。但这一指标 不改变ADC的基本量化特性——即每个输出码仍对应1 LSB宽度的输入电压范围。

输出数字码的确定原理

-

量化规则:ADC的输出码由输入电压所在的区间决定。理想情况下:

- 输入电压范围 0 ~ 0.61mV(0.5 LSB) → 输出码 0

- 输入电压范围 0.61mV ~ 1.83mV(1.5 LSB) → 输出码 1

(注:0.5 LSB是跳变点,1.5 LSB是下一个跳变点)

-

**例子:

- LSB = 1.22mV → 0.5 LSB = 0.61mV

- 输入电压 = 0.85mV,位于 0.61mV ~ 1.83mV 区间内

→ **理论输出码应为1**

尽管输入电压(0.85mV)已超过0.5 LSB(0.61mV),输出仍可能为 0,原因如下:

-

偏移误差(Offset Error):

若ADC存在负偏移误差(例如 -0.3 LSB),实际跳变点会从0.61mV偏移至 0.61mV + (-0.3×1.22mV) = 0.244mV。此时:输入0.85mV > 0.244mV → 应输出

1。 -

但若偏移误差为正值(如 +0.3 LSB):

跳变点变为 0.61mV + (0.3×1.22mV) = 0.976mV。此时:输入0.85mV < 0.976mV → 输出仍为

0。-

0 → 1 的跳变点:0.61mV+0.366mV=0.976mV

-

1 → 2 的跳变点:1.83mV+0.366mV=2.196mV

-

误差控制±0.5 LSB的意义:

它确保偏移、增益等误差的累积效应不超过±0.5 LSB,使跳变点偏移被限制在±0.61mV内,但不改变ADC的最小分辨能力(1 LSB)。

例如:若跳变点因误差从0.61mV偏移至1.0mV(仍在±0.5 LSB容忍范围内),则0.85mV输入仍低于跳变点 → 输出 0。 此误差就是偏移、增益等误差的**累积效应。

再多就不深入了解了。

个人认为不管是ADC低时钟频率还是高时钟频率都会产生影响,针对这些影响我们只需要先了解就行,并不需要太深入的理解,毕竟在开发过程中我们都是直接使用的,没有关注过具体实现细节。这些内容只是帮助我们知道我们在配置的时候应该注意什么,例如:始终优先满足奈奎斯特准则等关键性指标,至于其他的暂时只作为了解我觉得就够了。当然如果在追求一些高精度的信号采集,这些都是需要认真分析考虑的,通过这些情况分析那些事主要矛盾,那些是次要矛盾。

2.2.2 能否采样电流

还有一问题就是我们上述一直强调的是电压,也就是通过给一个基准比较电压,然后通过与采集电压进行比较,从而进行转换成数字信号,也就是12位分辨率,每一种可能代表一种电压值,12位分辨率就是表示一共有4095个情况,说白了就是将基准电压等分为4095份。但是在有些时候电流信号更容易输出,那这个时候怎么办?

ADC(模数转换器)本身只能直接采集电压信号。

但电流可以通过间接方式转换为电压信号,再利用ADC进行采集。

| 电流范围 | 推荐方案 | 关键器件 | 精度优化措施 |

|---|---|---|---|

| <100mA | 低端采样 + 运放放大 | 0.1%精度采样电阻 | 软件校准零点漂移 |

| 100mA~10A | 高端采样 + 电流检测放大器 | INA240, AD8418 | 差分输入抑制共模噪声 |

| 10A~200A | 霍尔传感器 | ACS758, LEM LAH 200-P | 温度补偿算法 |

| >200A 或交流大电流 | 电流互感器(CT) | 锰铜合金互感器 | 开尔文连接减少接触电阻 |

思路就是转换的思想,通过一些办法将电流转换为对应的电压。

电流需通过采样电阻、霍尔传感器或互感器转为电压信号。

优先用低端采样 + 精密运放;大电流/隔离需求:选霍尔传感器或互感器。

采样电阻精度、信号放大与滤波、温度补偿及软件校准。

2.3 采样原理详细分析

简单记录一下采样原理:

RAIN 等效于信号源的输出阻抗。

存在外部一个信号源,当有一个信号过来的时候,MCU内部的我们通过闭合开关SW,通过一个采样电阻RADC ,在通过一个 CADC电容进行充电,这样充满电以后就说明此时刻的信号源表示的信号已经传递到了MCU内部。

信号源的电压信号是一个动态变化的。

这里面有一个问题MCU内部开关从闭合开关的时间和断开时间这一段时间是什么呢?

对应的就是采用时间周期,并且这个时间是可以设置的。

另外值得说明的是,这个给内部 CADC电容充电的过程就应该理解为是保持的过程,

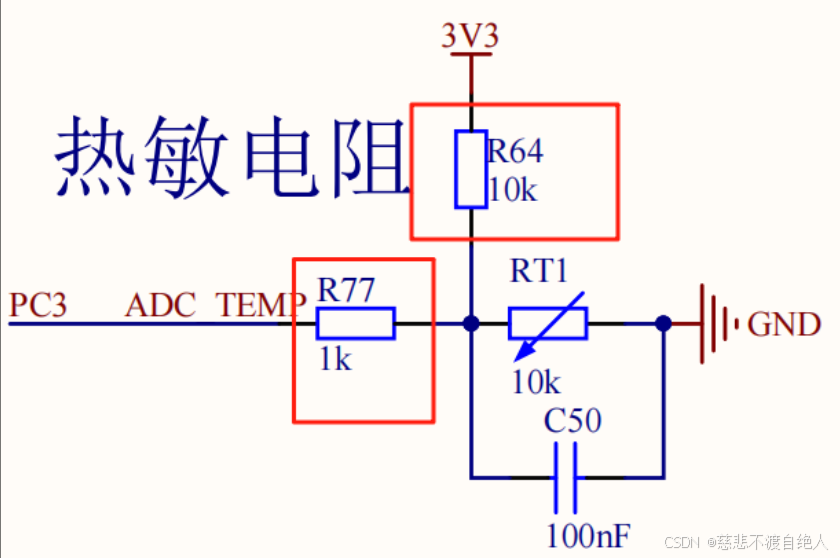

以下是设置这个采样时间的设置:根据上图电容公式可知时间常数跟外部阻抗相关,因为内部的阻抗RADC和CADC是确定的跟信号源无关,所以根据公式可以看出,时间常数是跟外部阻抗RAIN相关的。

表格代表的是40MHZ,外部阻抗和时间的关系。 该手册是芯片手册提供的。

采样时间周期是1.5,那么对应的采样时间是0.0375us(tc) 周期和采样时间是已知的从而可以推测出外部的电阻应该是多少。

从这个公式可以分析出,我们希望两个数值尽可能相等,那就是要求时间常数越小越好,也就是电阻值越小,但是这就意味着我们可以计算出一个最大值,那就是0.15K欧。

如果超过这个数字,在该状态下,也就是SW开关抬起以后,电容并没有被充满电(没有和信号源数值保持一致),那就意味着采集的数值不准确。

跟我们的信号源的输出阻抗是强相关的,这也是为什么我们看到一些ADC的外围电路有电阻的原因,因为通过刚才的计算我们明确的可以知道,这是必须要的。如下图的热敏ADC采集电路。

举个例子:

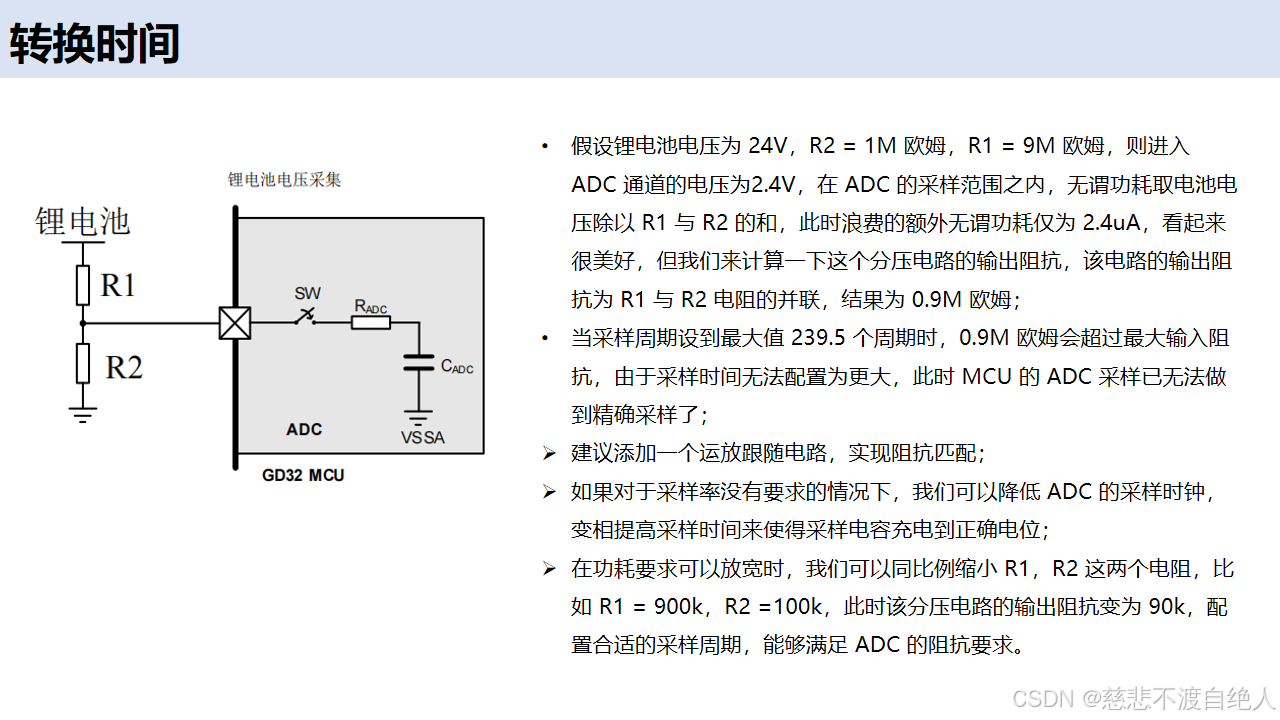

假设锂电池电压为 24V,R2=1M 欧姆,R1=9M 欧姆,则进入ADC 通道的电压为2.4V,在 ADC 的采样范围之内,无谓功耗取电池电压除以 R1 与 R2 的和,此时浪费的额外无谓功耗仅为 2.4uA,看起来很美好,但我们来计算一下这个分压电路的输出阻抗,该电路的输出阻抗为 R1 与 R2 电阻的并联,结果为 0.9M 欧姆当采样周期设到最大值 239.5 个周期时,0.9M 欧姆会超过最大输入阻抗,由于采样时间无法配置为更大,此时 MCU 的 ADC 采样已无法做到精确采样了;

1、建议添加一个运放跟随电路,实现阻抗匹配

2、如果对于采样率没有要求的情况下,我们可以降低 ADC 的采样时钟变相提高采样时间来使得采样电容充电到正确电位;

3、在功耗要求可以放宽时,我们可以同比例缩小 R1,R2 这两个电阻,比如 R1=900k,R2 =100k,此时该分压电路的输出阻抗变为90k,配置合适的采样周期,能够满足 ADC 的阻抗要求。

接下来关于ADC采集还有一部分滤波内容,后续会整理出来,做一次系统分享,因为滤波涉及内容很多,暂时还没有完全整理出来。

专栏介绍

嵌入式通信协议解析专栏

PID算法专栏

C语言指针专栏

单片机嵌入式软件相关知识

FreeRTOS源码理解专栏

文章源码获取方式:

如果您对本文的源码感兴趣,欢迎在评论区留下您的邮箱地址。我会在空闲时间整理相关代码,并通过邮件发送给您。由于个人时间有限,发送可能会有一定延迟,请您耐心等待。同时,建议您在评论时注明具体的需求或问题,以便我更好地为您提供针对性的帮助。

【版权声明】

本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议。这意味着您可以自由地共享(复制、分发)和改编(修改、转换)本文内容,但必须遵守以下条件:

署名:您必须注明原作者(即本文博主)的姓名,并提供指向原文的链接。

相同方式共享:如果您基于本文创作了新的内容,必须使用相同的 CC 4.0 BY-SA 协议进行发布。

感谢您的理解与支持!如果您有任何疑问或需要进一步协助,请随时在评论区留言。