Tang Prime 20K板I2S输入输出例程

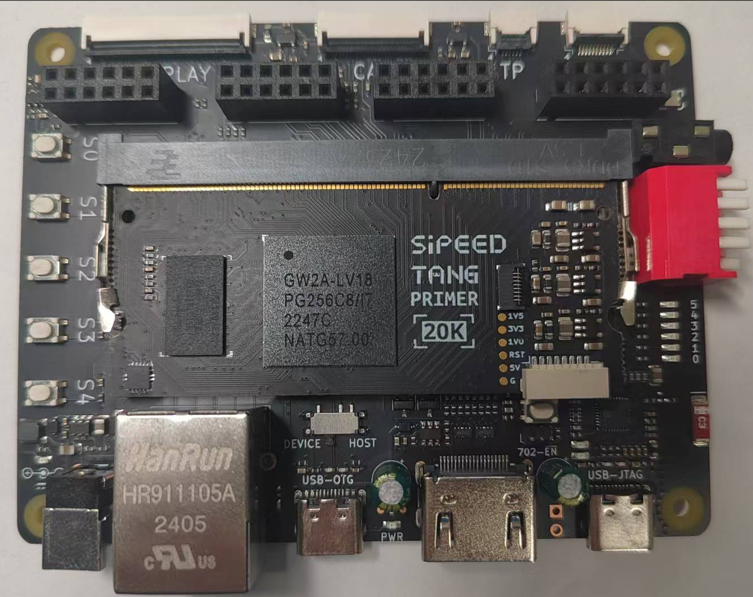

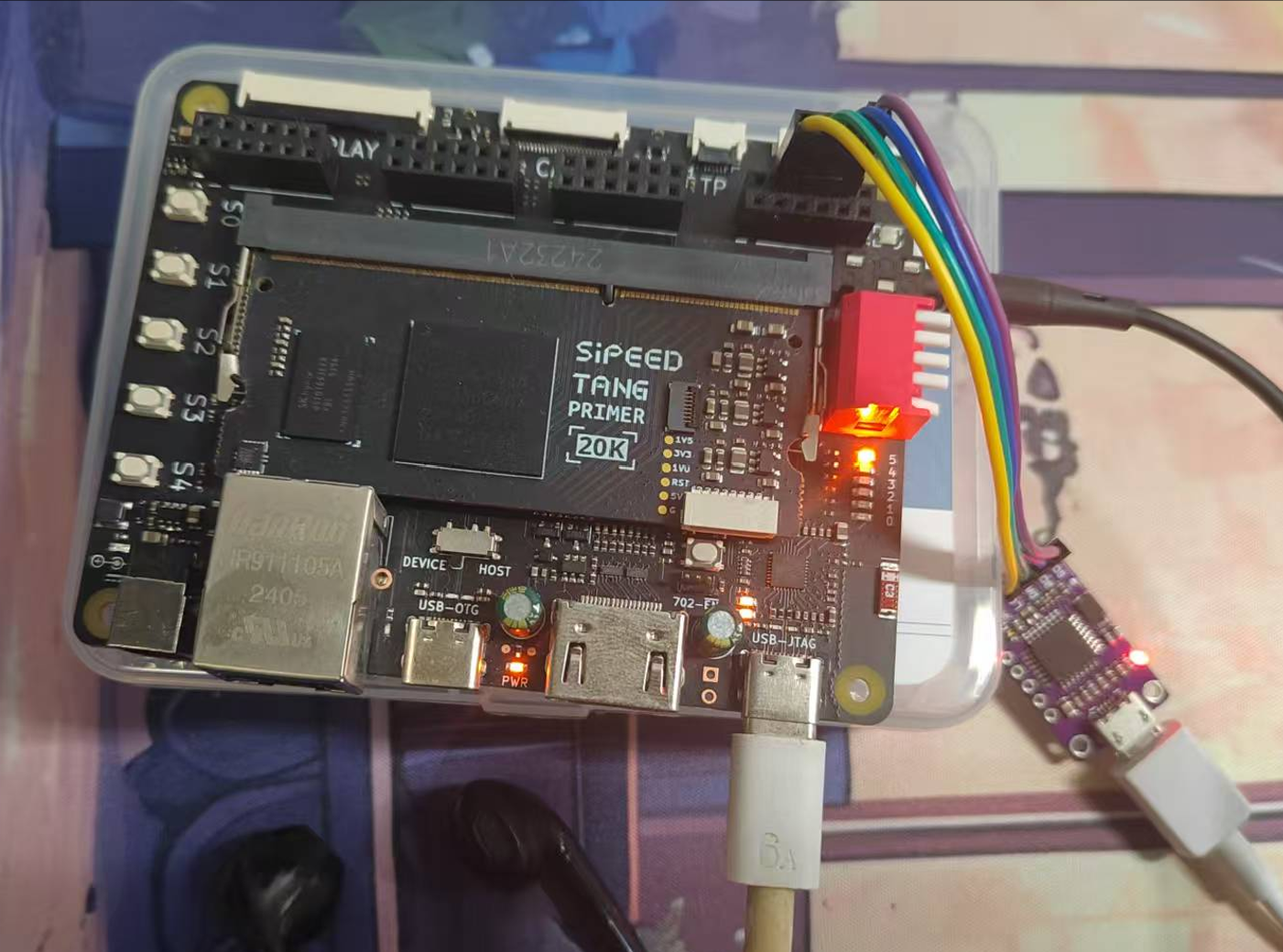

Tang Primer 20K是由开源硬件厂商SiPEED矽速科技推出,是一款以 GW2A-LV18PG256C8/I7 为主芯片的核心板,准备了 2 个扩展板,Dock 和 Lite。板卡包含有HDMI输出,DVP接口,3.5mm headphone Jack接口,按键,LED灯。另外JTAG下载器已集成在板上,只需一根USB Type-C的线就可以实现下载调试,板卡供电也是依靠这条Type-C的线。板卡相关资料可参考官方网址:https://wiki.sipeed.com/hardware/en/tang/tang-primer-20k/primer-20k.html

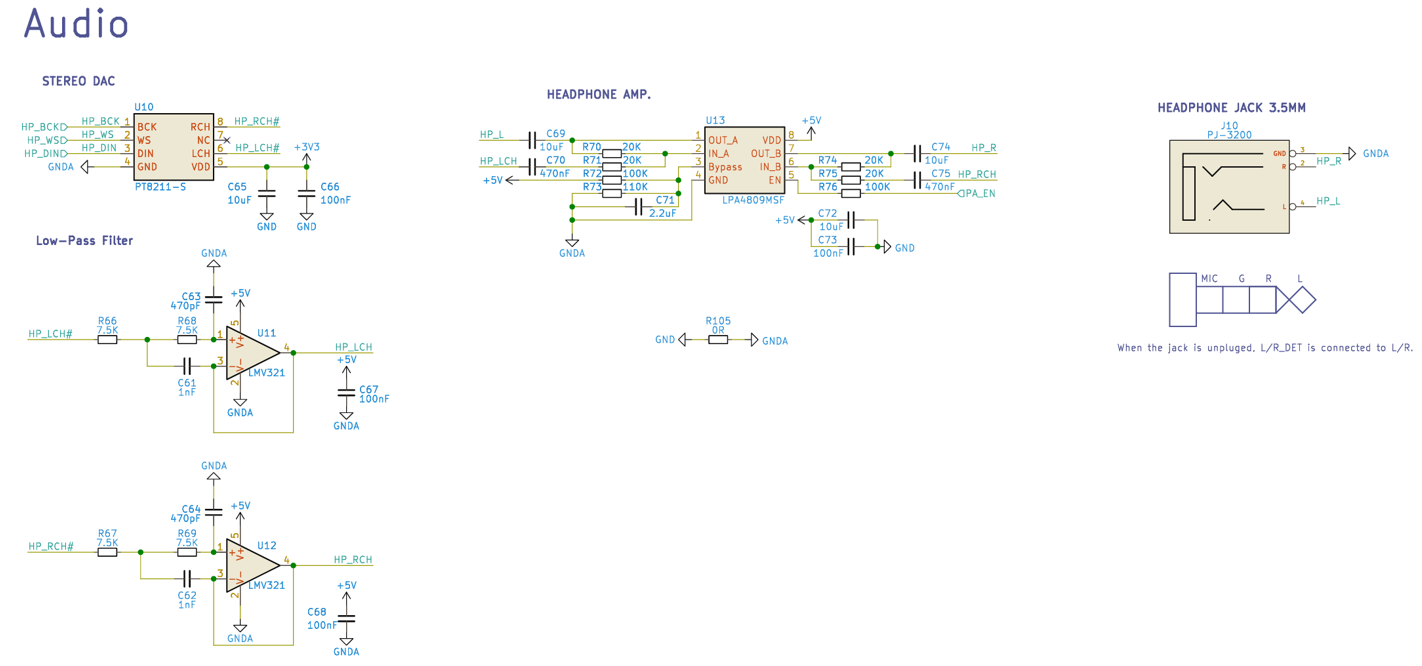

Tang Prime 20K开发板有个3.5mm headphone Jack耳机输出口,准备进行I2S音频输入输出验证。

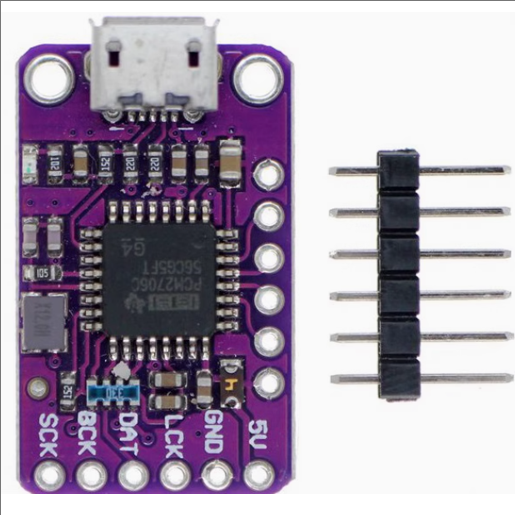

音频输出有了,还需要有个音频输入,这里使用GY-PCM2706 USB TO I2S 模块,大概30多块钱。

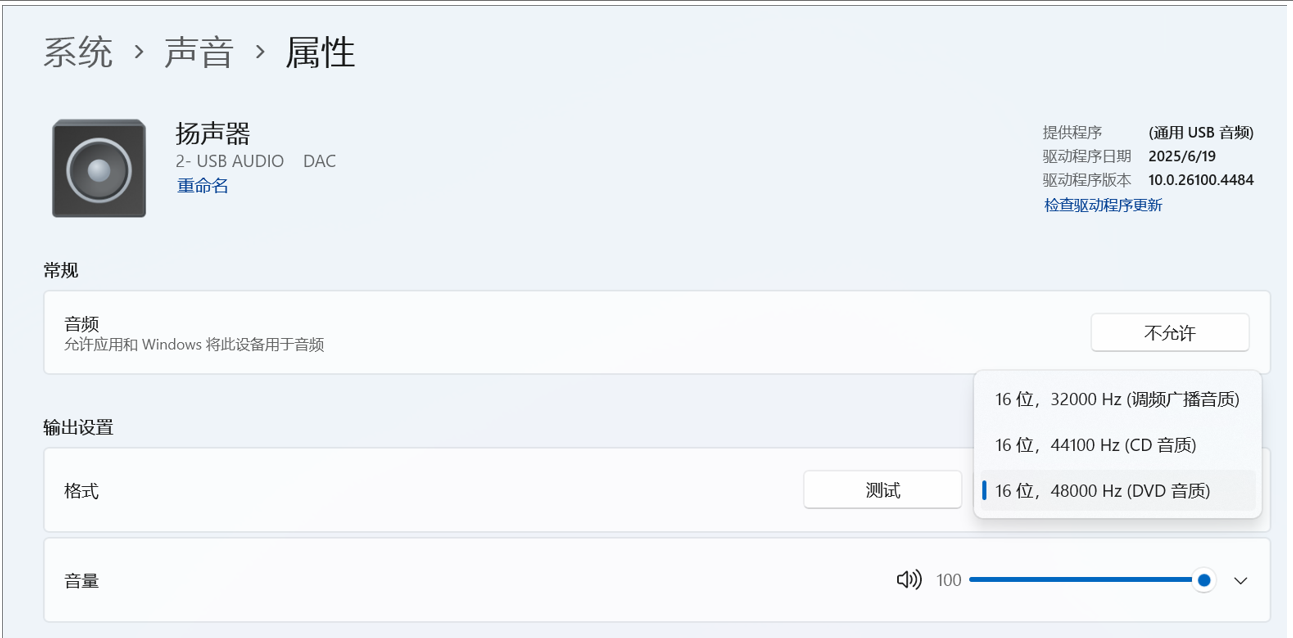

免驱动,即插即用,直接识别到一个USB Audio设备,播放音乐时用此设备输出即可。

输出格式也是常见的48KHz或44.1KHz。

1. 运行PT8211例程

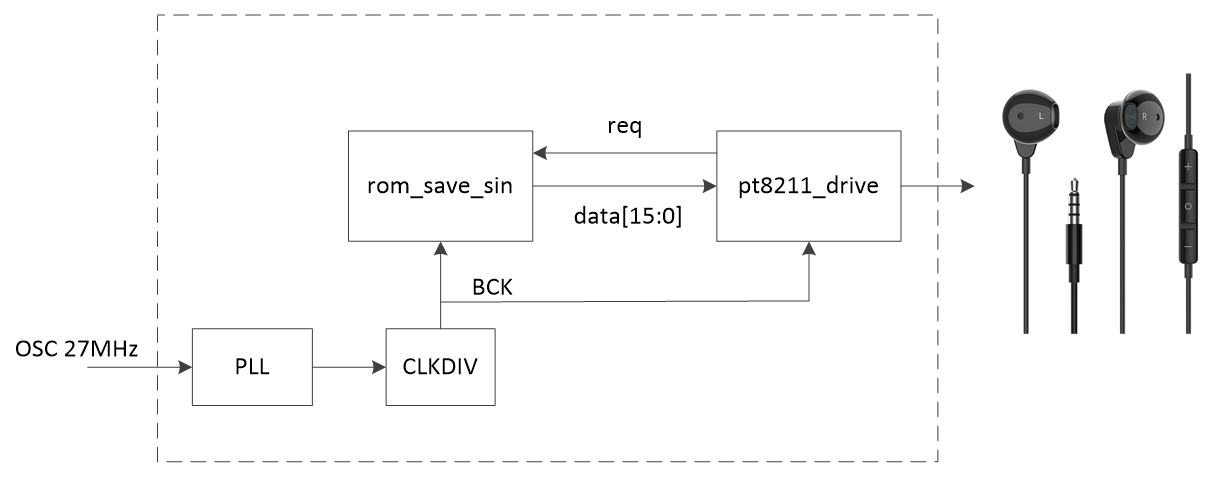

(1)程序主要结构框图

(2)github上的例程是用rom存储正弦波数据,由晶振产生约6.144MHz的时钟,再4分频得到位时钟BCK,控制pt8211驱动模块从rom中读取数据。实际听到的就是蜂鸣声,不太好确认音质,最好能听音乐声。

//pt8211驱动程序如下

module pt8211_drive(input clk_1p536m,//bit时钟,每个采样点占32个clk_1p536m(左右声道各16)input rst_n ,//低电平有效异步复位信号//用户数据接口input [15:0] idata ,output req ,//数据请求信号,可接外部FIFO的读请求//pt8211接口output HP_BCK ,//同clk_1p536moutput HP_WS ,//左右声道切换信号,低电平对应左声道output HP_DIN //dac串行数据输入信号

);

reg [4:0] b_cnt;

reg req_r,req_r1;//req_r1延迟req_r一个时钟

reg [15:0] idata_r;//暂存idata,用于移位并转串时的中间变量

reg HP_WS_r,HP_DIN_r;

assign HP_BCK = clk_1p536m;

assign HP_WS = HP_WS_r ;

assign HP_DIN = HP_DIN_r ;

assign req = req_r ;

//b_cnt

always@(posedge clk_1p536m or negedge rst_n)

begin

if(!rst_n)b_cnt <= 5'd0;

elseb_cnt <= b_cnt+1'b1;

end

//req_r

always@(posedge clk_1p536m or negedge rst_n)

begin

if(!rst_n)req_r <= 1'b0;

elsereq_r <= (b_cnt == 5'd0) || (b_cnt == 5'd16);//每16个时钟读入一个数据

end

//idata_r

always@(posedge clk_1p536m or negedge rst_n)

begin

if(!rst_n)beginreq_r1 <= 1'b0;idata_r <= 16'd0;end

elsebeginreq_r1 <= req_r;idata_r <= req_r1?idata:idata_r<<1;end

end

//HP_DIN_r

always@(posedge clk_1p536m or negedge rst_n)

begin

if(!rst_n)HP_DIN_r <= 1'b0;

elseHP_DIN_r <= idata_r[15];

end

//HP_WS_r

always@(posedge clk_1p536m or negedge rst_n)

begin

if(!rst_n)HP_WS_r <= 1'b0;

elseHP_WS_r <= (b_cnt == 5'd3)?1'b0: ((b_cnt == 5'd19)?1'b1:HP_WS_r);//对齐数据

end

endmodule

2. 运行I2S输入输出例程

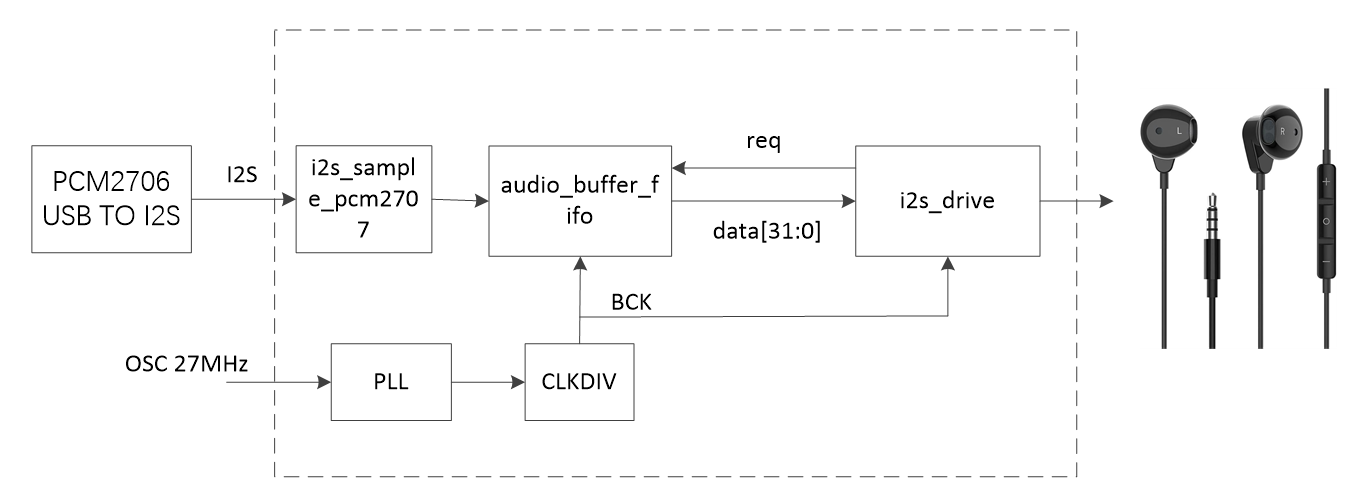

(1)程序主要结构框图

(2)I2S输入输出例程是用GY-PCM2706 USB TO I2S 模块作为音频输入源,USB与PC相连,由PC播放音频。然后用i2s_sample_pcm2706模块将串行音频数据转成并行,再存入FIFO缓存中,最后再由i2s_drive模块驱动pt8211输出。

声音可以听到,但杂音较多。提高bck时钟频率,也没什么改善。另外输出用的BCK也可以使用从pcm2706输入的bck时钟,但效果差不多。

// PCM2706采样程序如下

module i2s_sample_pcm2706

( input I_rst_n ,//low activeinput I_bclk ,input I_lrck ,input I_din ,output O_de , output[31:0] O_lr_data

);reg lrck ;

reg lrck_d1 ;

wire lrck_fall_w = (!lrck) &&lrck_d1 ;

wire channel_start = lrck_fall_w ;reg[63:0] data ;

reg de ;

reg[31:0] lr_data ;always@(posedge I_bclk or negedge I_rst_n)

begin

if(!I_rst_n)beginlrck <= 1'b0 ;lrck_d1 <= 1'b0 ;end

elsebeginlrck <= I_lrck ;lrck_d1 <= lrck ;end

endalways@(posedge I_bclk or negedge I_rst_n)

begin

if(!I_rst_n)begindata <= 64'h0;end

elsebegindata <= {data[62:0],I_din} ; end

endalways@(posedge I_bclk or negedge I_rst_n)

begin

if(!I_rst_n)beginde <= 1'b0 ;lr_data <= 32'h0;end

elsebeginif(channel_start)beginde <= 1'b1 ;lr_data <= {data[30:15],data[62:47]};endelsebeginde <= 1'b0 ; lr_data <= lr_data;endend

endassign O_de = de ;

assign O_lr_data = lr_data ;

endmodule

//i2s_drive模块程序如下,在原程序上做了修改,对左右声道数据分开请求。

//bck频率=2*采样率*位宽

//---------------------------

//1.536MHz = 2 * 48KHz * 16

//---------------------------

//1.4112MHz = 2 * 44.1KHz * 16

//---------------------------module i2s_drive #

(DWIDTH = 16 //data width 16/24/32

)

(input sclk ,//bit时钟, F(sclk) = F(WS) * 2 * DWIDTH (左右声道各DWIDTH位宽)input rst_n ,//低电平有效异步复位信号input [DWIDTH-1:0] l_idata ,//左声道数据input [DWIDTH-1:0] r_idata ,//右声道数据output l_req ,//数据请求信号,可接外部FIFO的读请求output r_req ,//output BCK ,//同clk_1p536moutput WS ,//左右声道切换信号,低电平对应左声道output DIN //dac串行数据输入信号

);localparam CNTMAX = 2*DWIDTH-1;

reg [5:0] b_cnt;//最大计到63,覆盖左右声道各32bit的情况reg l_req_r,l_req_r1,l_req_r2;//req_r1延迟req_r一个时钟

reg r_req_r,r_req_r1,r_req_r2;//req_r1延迟req_r一个时钟

reg [DWIDTH-1:0] idata_r;//暂存idata,用于移位并转串时的中间变量

reg HP_WS_r,HP_DIN_r;assign BCK = sclk;

assign WS = HP_WS_r ;

assign DIN = HP_DIN_r ;//左右声道数据各自独立取,那就需要两个请求信号

assign l_req = l_req_r ;

assign r_req = r_req_r ;//b_cnt

always@(posedge sclk or negedge rst_n)

beginif(!rst_n)b_cnt <= 6'd0;else if(b_cnt>=CNTMAX)b_cnt <= 6'd0;elseb_cnt <= b_cnt+1'b1;

end//req_r

always@(posedge sclk or negedge rst_n)

begin

if(!rst_n)l_req_r <= 1'b0;

elsel_req_r <= (b_cnt == 0);//第0时钟取左声道数据

endalways@(posedge sclk or negedge rst_n)

begin

if(!rst_n)r_req_r <= 1'b0;

elser_req_r <= (b_cnt == DWIDTH);//第DWIDTH时钟取右声道数据

end//idata_r

always@(posedge sclk or negedge rst_n)

begin

if(!rst_n)beginl_req_r1 <= 1'b0;l_req_r2 <= 1'b0;r_req_r1 <= 1'b0;r_req_r2 <= 1'b0;idata_r <= {DWIDTH{1'd0}};end

elsebeginl_req_r1 <= l_req_r;l_req_r2 <= l_req_r1;r_req_r1 <= r_req_r;r_req_r2 <= r_req_r1;idata_r <= l_req_r1 ? l_idata : //l_req_r2r_req_r1 ? r_idata : idata_r<<1; //左右数据交替输入 //r_req_r2end

end//HP_DIN_r

always@(posedge sclk or negedge rst_n)

begin

if(!rst_n)HP_DIN_r <= 1'b0;

elseHP_DIN_r <= idata_r[DWIDTH-1];

end//HP_WS_r

always@(posedge sclk or negedge rst_n)

begin

if(!rst_n)HP_WS_r <= 1'b0;

elseHP_WS_r <= (b_cnt == (0+3))?1'b0: ((b_cnt == (DWIDTH+3))?1'b1:HP_WS_r);//对齐WS与数据

endendmodule