数电汇总——logisim的辛酸史

二、Logisim安装和使用

我用github上的 release 版本下载的,但却得到了这样的问题

我初次的时候改了一下路径,改成D盘,还是出现了这样的问题,于是我仔细阅读了英文,大胆猜测是权限不够的问题,我想以管理员的权限打开,竟然发现没有,用STFW方法暴力操作了一顿,好像还是不行,属性也点过了,那一个管理员权限似乎不给开启,遂放弃,用百度网盘吧!

还是不行,实在想不出有什么解决方案了,就拿着问题去问问AI,我之前的版本是

java version "1.8.0_271"

Java(TM) SE Runtime Environment (build 1.8.0_271-b09)

Java HotSpot(TM) 64-Bit Server VM (build 25.271-b09, mixed mode)

远远低于logisim 3.8.0的版本,于是我就去oracle官网更新了一波Java环境

java version "21.0.7" 2025-04-15 LTS

Java(TM) SE Runtime Environment (build 21.0.7+8-LTS-245)

Java HotSpot(TM) 64-Bit Server VM (build 21.0.7+8-LTS-245, mixed mode, sharing)

更新成功

直接去github相应3.8.0下载一个 .jar包即可

java -jar "C:\Users\Alaso\Desktop\logisim-evolution-3.8.0-all.jar"

笑麻了,这个花了我两个小时时间

触发器学习

SR触发器

需要关注输入端是否有0的与非门

PS:

Q = 1,Q非 = 0 为触发器的“1”状态;

Q = 0,Q非 = 1 为触发器的“0”状态。

SR触发器有两个输入端,一个是 置位 (set),另一个是复位(Reset)

弊端:输入要保持一段时间,否则可能出现“空翻”现象

我理解的空翻:

给定你想要的信号,你需要改变原先信号,那么得到你想要信号的一段阈值后,其他段信号也会随着你输入的改变而改变,最终会得到后面一段与之原本不匹配的现象,叫做空翻

S为低电平、R为高电平时,SR触发器变成复位状态(次态全部为0)

S和R均为低电平时,SR触发器保持前一个状态(次态与初态保持不变)

S 为高电平,R为低电平时,SR触发器变成置位状态(也就是次态全部变成1)

两个都是高电平不合理(结合图例,当S = 1时,S’ = 0;当R = 1时,R’=0,又因为经过与门,0毫无疑问输出肯定为0,再取反,Q’ = 1,代入去S’那一端,得到Q = 1,两者矛盾)

作用:初始化电路

待补:同步和异步

D触发器

只有一个输入端,次态和你输入的信号相同,不管初态是什么[注意:当前仅当时钟频率一样的时候输出相同]

T触发器

只有一个T输入端,次态和你输入的信号相反,不管你初态是什么

问题:为什么当CLK是1时,Q和Q’的高低电平会不太一样,不是说输出和输入一样吗?

多路电路复用学习

问题:为什么会形成多路电路?怎么形成的呢,你在一个文件里面创建电路,就可以拿这个电路作为复用工具集成在下一个文件上

我以为 3:1 多路电路,没想到输出端子就只有两个,下面Sel_0 和 Sel_1是选择开关,于是我用按键开关代替了一下

这才是正确的图示,多路电路任选一个即可,但这里我还有个疑问:是否是一 一对应的电路关系,就比如我第一个输入置为高电平,第一个输出是否也是直接高电平输出;而第二个输入置为高电平,第一个输出是否为高电平,如果不是,是为什么? 我试的结果是不是高电平

数字逻辑电路基础

通过晶体管搭建门电路

或非门分析:

解答:

搭建异或门

晶体管数最少

搭建同或门

通过门电路搭建基本组合逻辑电路

搭建2——4译码器

其实就按照00 01 10 11 排列即可,但是注意此处 00 指的是你打开T0的状态,也就是说你的输入一旦打开后需要两个都取反才能得到正确结果,下面搭建也是一样的思路

译码器的输入即为地址, 输出则是选择信号

搭建3-8译码器

先封装子电路

搭建3——8译码器的错误示范

注意:你的2——4译码器的输出单单指2——4译码器的输出,不是3——8译码器的输出

所以你得在2——4译码器之后继续添加与门,其实也就是合并两个位,剩余那位做控制信号,有一个位变化得非常有规律,就是第一位 前七位稳定是0,后七位稳定是1观察到此规律后就可以直接加非门进行操作了!

七段数码管译码器

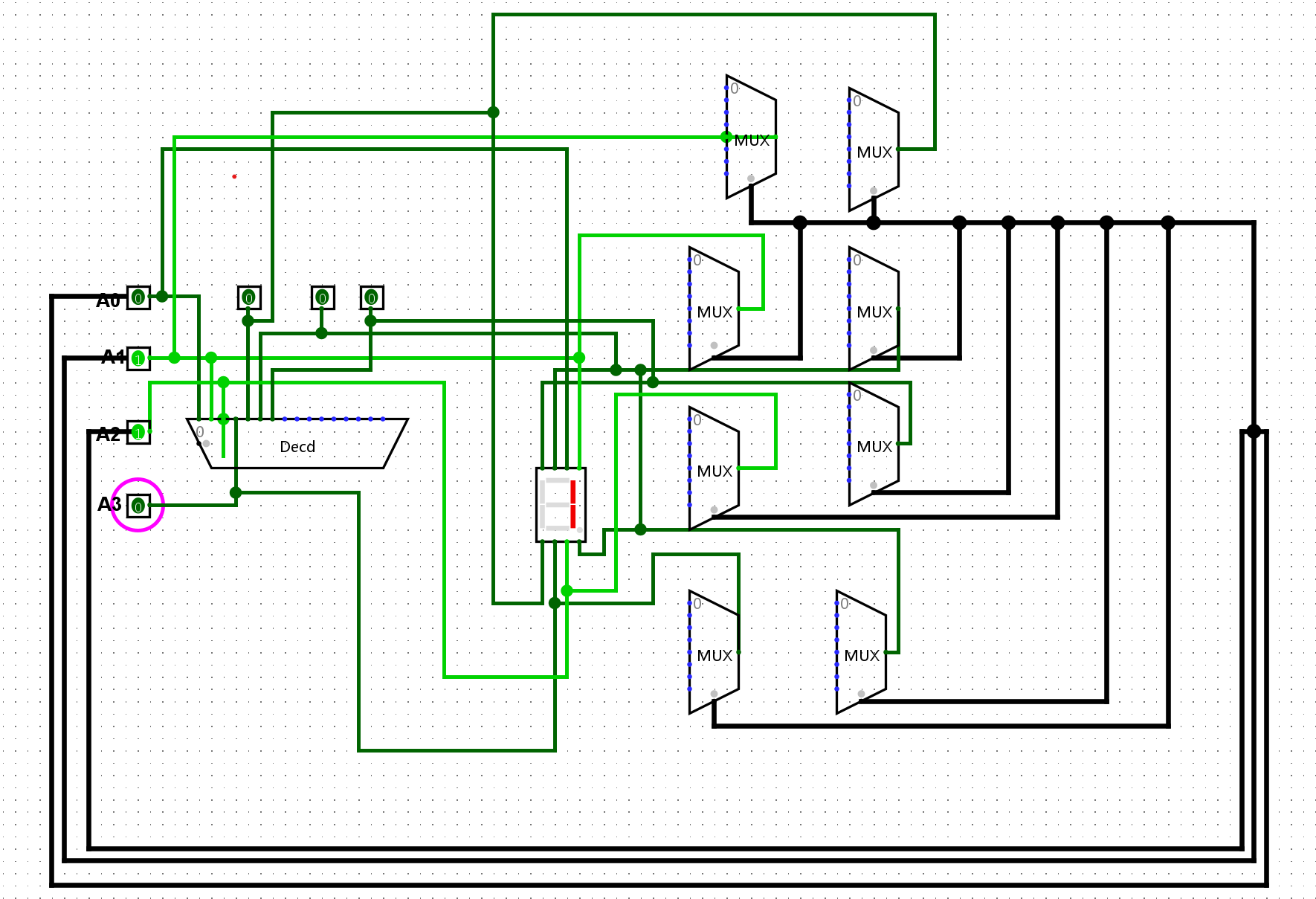

直接用了8:1译码器和4——16多路复用器组合上手操作

我发现多路复用器没有发挥应有的作用于是直接用了8:1译码器上手操作

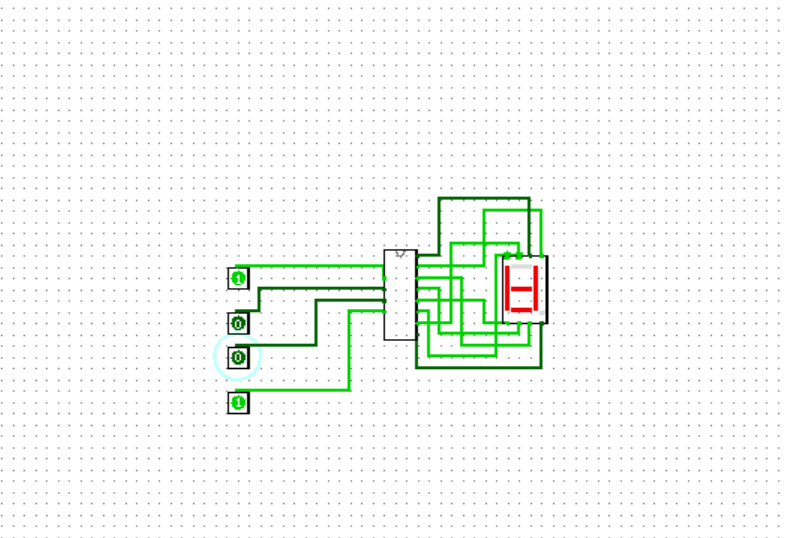

然后设计16进制的,我自己用真值表自动生成了一个子电路,然后用四个开关决定4位二进制数,似乎位置搞反了(这个软件突然抽风,上面没有显示abcdefg了)其实还可以加一个或门优化操作

搭建编码器

搭建16-4编码器,思路大概是 列出所有位的真值表,输入 I0 ~ I15 ,输出 Y0 ~ Y3 ,分别列出对应的01数值后,看输出对应有“1”的地方就是其最小项,直接列出即可,然后再将这些项加起来(或门连接)就是对应这个输出的门电路!其实还有一个办法就是用两个8-3编码器组合在一起,然后用相应逻辑门(与门和或门)来连接

还有一个办法就是使用5个4-2编码器,但是能耗大

搭建4-2优先编码器

首先让我们来解释一下什么叫做优先编码器,用书上的话来说就是希望在输入不为独热码的时候仍然输出有效的信息,而我的理解是,你之前的编码器输入不都是需要一位1撑着吗,1后面的位必须为0,而优先编码器恰恰解决了这个麻烦的问题,只要前一位为1,你就可以不用管后一位究竟是什么。

先搭建一个 4-2编码器

再对其真值表改一下即可

Y1 = X3 + X2

Y0 = X3 + (~X2 & X1)

V = X0 + X1 + X2 + X3

于是,4-2优先编码器就出来了

多加了一个有效信号V

两者的区别: 4-2普通编码器用了2个门电路,4-2优先编码器用了5个门电路(估计我中途化简成最小项了)

减法器

其实跟加法有异曲同工之妙

| A | B | S | C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 所以可以提取到的公式是: |

S = A ^ B

C = ~A & B

电路图如下:

全减法器其实就要考虑低位向高位借位了,就像全加器一样,有Co(本位)和 Cl(进位)

补速通数电 Day1

chapter1

工程三大特点: 层次化,模块化,纪律性

重点:

1.进制之间的转换

2.原码补码反码的介绍(正数的反码和补码都是他本身;负数的反码是除符号位之外取反,负数的补码是反码+1)

3.符号扩展和0扩展

简单来说就类似于左移右移需要补位一样,注意区分有符号数或者无符号数

4.逻辑门

5.待补:NMOS和PMOS的原理(半导体导电那个)

6.注意:NMOS在高电平时能有优势,所以需要接地;PMOS在低电平中有优势,所以接VCC

与非门:

PMOS并联,NMOS串联(分别给予2 ^ 2 = 4种情况信号) 总结:上并下串

非门:

PMOS管 和 NMOS管 并联

或非门:

PMOS管串联 ,NMOS管并联 总结:上串下并

chapter2:

组合逻辑:输出完全由输入决定,多输出电路的话具有优先级

时序分析简单概念引入:

1.传播延迟Tpd:输入的转变发生到 (稳定输出转变发生的最大时间) 和 污染延迟 Tcd(输入的转变发生到刚刚影响输出的最小时间)

(这两者对应着延迟的最大值或者是最小值)其中传播延迟的路径与时间成正比

PS:这里有个很容易忽略的点就是:一般从1/2的位置开始测 为什么的话这里存疑

概念:

1.浮动状态:一个节点既没有驱动到高电平,也没有驱动到低电平,用Z表示浮动状态

2.卡诺图化简

3.多路复用器(上面会有选择几个节点决定输出端口,若输入端口有n个,那么输出端口就有log2N个)

4.解码器 特性:n个输入端,2 ^ n个输出端口

chapter3:

时序电路:

1.时序电路的输出不仅取决于当前的输入,还与之前的输入值有关

2.电路分类:

(1)双稳态电路 Bistable Circuit

两个输出 无输入

组成:两个朝向相同的非门

弊端:无法控制输入

(2)SR 锁存器

总结:当S = 1时,Q会被置为1;R = 1时,Q会被置为0;当S = 0,R = 0时,锁存器仅保留之前存储的值

(3)D 锁存器

两个输入CLK(控制何时发生变化),Data(控制变成何种状态)

实际上是刚刚的 SR锁存器前面加两个与门,与门前面放时钟信号和Data(D和~D)

(4)D触发器

两个输入 CLK(这里简化为三角形,也就是边沿触发(该电路对时钟信号的边沿做出respond)这里的时钟指01信号随着时间变化,0->1为上升沿,1->0为下降沿),D

组成:两个D锁存器结合,但上面有CLK的正向信号和反向信号组成

这里我有个疑问,你的前面D锁存器把D传输到N1,N1不是个通道吗,为什么能暂时存下这个D,然后再用时钟把N1中的数据放到第二个D锁存器?

是这样,可以暂存在N1中暂存D

有限状态机

可以用按键PPT课件页数来理解这个抽象概念

你的当前PPT页数作为你的当前状态,你的按键作为输入参数,下一页页码由当前状态下的页码和你的输入共同决定

数电速通 Day2

组合逻辑:

毛刺:每个电路经过的逻辑门时延不同,最后汇聚到一起经过同一个门电路的时间也不同,那么输出会有一段时间为0

阵列电路:

1.编码器

常见的8-3编码器,注意这里2 ^ n = 8 所以对应输出端口有n = 3个,因此我们可以用这三个端口来表示八个输入,000~111表示下去即可

若要连接三个输出的门,得看是什么电平促使他可以工作的!!!

注意:输入口太多会导致扇入的问题,输出口太多也会导致扇出的问题

2.译码器

与编码器相反,2 ^ (已知输入端子) = n ,这个n就是我们需要设计的输出端子的个数,注意一般4-16路译码器会采用4 - (~ 中途连过去时有取反)8- 8实现,目的主要为了不要让他产生扇出

3.多路复用器

看控制输入的二进制数是什么,再通过译码器的组合后面再增添一个与门(这样做不会影响电路整体,只会和你输入的数据保持一致)

4.只读存储器ROM

作用:地址到值的映射

这里有一个很抽象的点,就是假设你的数据有3个,那么就得去找你的2^M条字线的地址,对应每一位取或运算,能留下来的就接一条线去数据那里

5.可编程逻辑阵列(PLA)(仅作了解即可)

算术电路:

1.移位器 (了解即可)

2.加法器