【更新中】《硬件架构的艺术》笔记(三):处理多个时钟

介绍

单时钟设计更易于实现,也更少出现亚稳态、建立和保持时间违例方面的问题。但在实践中,很少有设计只在一个时钟下运行。

多时钟域

多个始终可以有以下一种或多种时钟关系:

1、时钟频率不同。

2、时钟频率相同,但相位不同。

多时钟域设计的难题

1、建立时间和保持时间的违背。

2、亚稳态。

事实上1就会导致2

违背建立时间和保持时间

多时钟域情况下,很容易出现一个时钟域的输出在另一个时钟域的时钟上升沿到来时发生改变的现象。

图中xclk_output1不满足建立时间和保持时间,所以会造成亚稳态。而xclk_output2则没有该问题。

多时钟设计的处理技术

通用准则:

1、时钟命名

2、分模块设计

时钟命名法

为了方便脚本使用通配符对所有时钟进行操作,对时钟应有一个确定的命名,如sys_clk、tx_clk和rx_clk,同属一个时钟域的信号也应在命名时使用同样的前缀,这样可以方便分辨出信号所属时钟域,并决定时直接使用该信号,还是同步后使用。

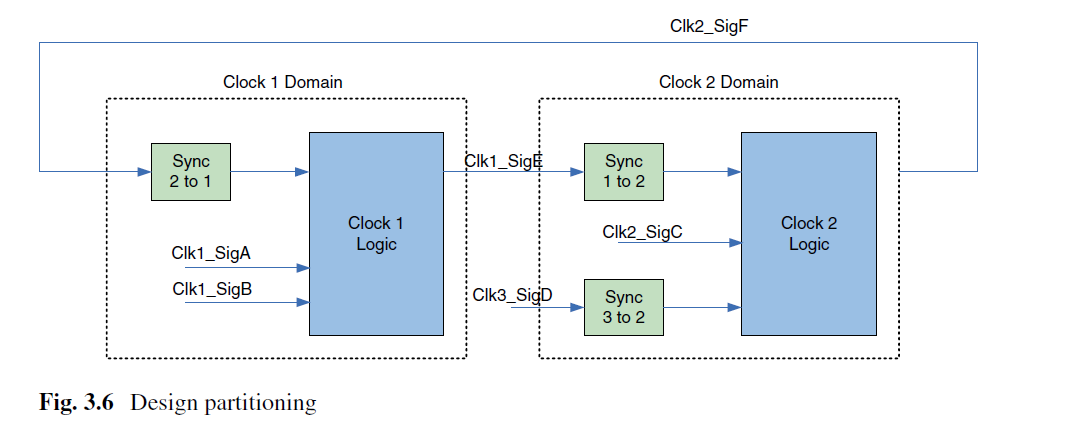

分块化设计

- 每个模块只因当在单个时钟下工作

- 在信号跨时钟域传输时,使用同步器模块。

- 同步器规模尽可能小。

优点:使静态时序分析变得很简单。单个模块可以看作是完全同步的。另外,同步模块不需要做静态时序分析,但是要保证满足保持时间要求。

如图所有跨时钟域传输的信号都要经过一个额外的同步器模块。

跨时钟域

两类:控制信号的传输、数据信号的传输。

控制信号的传输(同步化)

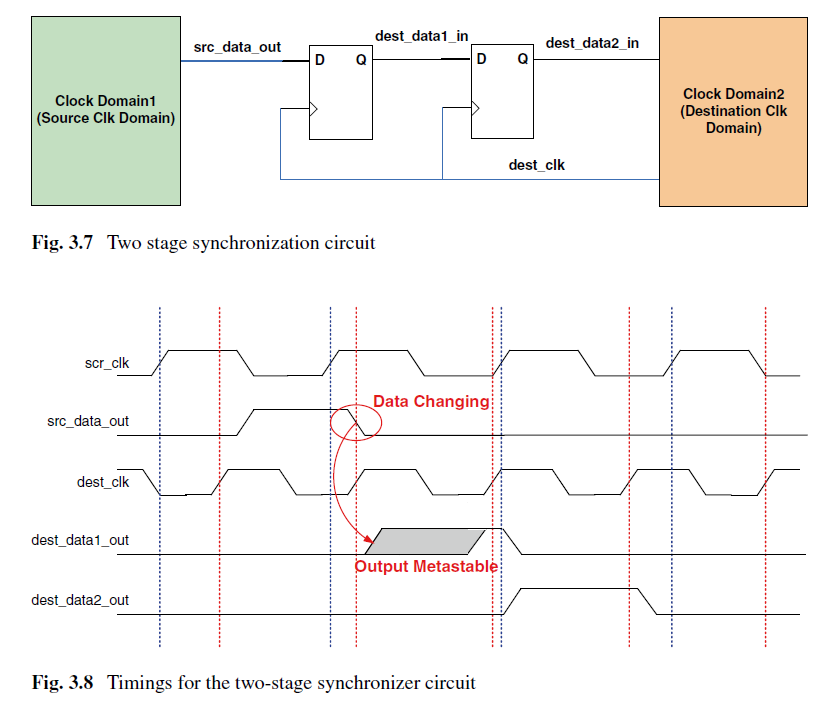

最常用的方式:多级同步器。(只能降低亚稳态可能性,增加更多级触发器,可以进一步降低亚稳态出现的可能性)

缺点(不可避免地开销):增加了电路的整体延时。

可以看到,亚稳态如果在一个周期内稳定下来,第二级寄存器就能输出一个稳定的值。

有时第一级同步器信号从亚稳态进入稳态需要不止一个周期,第二级触发器输出依然亚稳态,这是为了安全起见,应加入三级同步器。

大多数设计中两级同步电路就足以避免亚稳态出现了,只有在时钟频率非常高的设计中才要求使用三级同步器电路。

数据信号的传输

两种方法:

1、握手信号

2、异步FIFO

同频零相位差时钟

其实就是单时钟设计。

同频恒定相位差时钟

从这幅图看感觉对建立时间要求更高了,对保持时间要求变低了。对组合逻辑的延时约束会变得更紧。这种情况不需要同步器,只需要使设计STA通过即可。

非同频、可变相位差时钟

整数倍频率的时钟

clk2捕获数据的时间可能是T、2T、3T,取决于数据在clk1哪个边沿发出。任意路径的最差延迟都应在时钟边沿相位差T时满足建立时间要求。最差保持时间应在时钟边沿相位差为零时进行。

可以使源数据每三个源时钟改变一次,防止丢失数据。

非整数倍频率的时钟

情况一:源时钟有效沿和目的时钟有效沿之间有足够大的相位差,不会有亚稳态产生。

clk1和clk2分别是对同一个时钟的3分频和2分频,如图,两个时钟最小相位差为2.5ns,满足建立时间和保持时间,但应避免在跨时钟位置使用任何组合逻辑。

慢到快不会有数据丢失;快到慢可能出现数据丢失,为了解决这个问题,必须将元数据保持至少一个目标时钟周期。

情况2:两个有效沿很近,但当再出出现挨着的情况前,接下来的几个周期两个时钟沿会保留足够的裕量。

图中期望的波形使B1,实际的波形使B2。这里数据不会丢失(因为是从慢到快),但是可能不连贯。

从快倒满可能出现数据丢失,为了阻止这种情况,源数据应保持至少一个目标时钟周期不变。

情况三:相位差异小,能连续存在几个周期。

图中前两个周期可能违背建立时间,后两个周期可能违背保持时间。

这种情况下,即使数据从慢到快时钟域也可能丢失。

为了不丢数据,数据应保持至少两个目的时钟周期,这同时适用于快到慢和慢到快。但是数据不连续的问题依然存在。

这时,使用握手和FIFO传输数据就更有效,因为它们解决了数据不连续的问题。

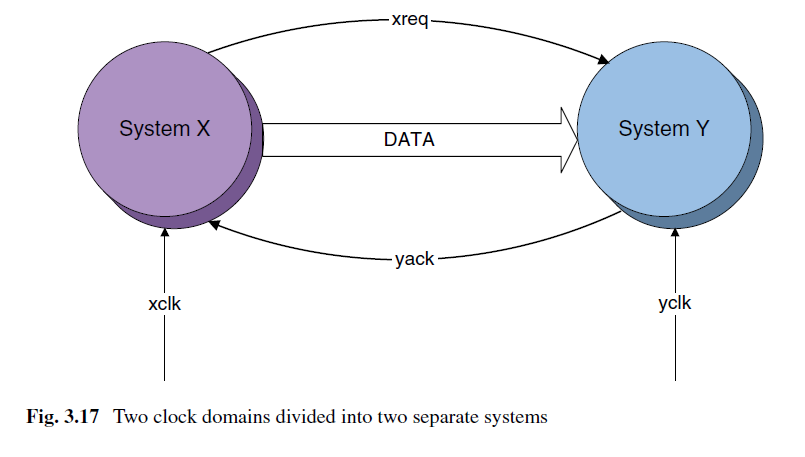

握手信号方法

- X将数放在数据总线上兵发出xreq信号,表示有效数据已经发到接收器Y的数据总线上。

- xreq信号同步到接收器时钟域ylk上。

- Y在识别xreq同步的信号yreq2后,锁存数据总线上信号。

- Y发出确认信号yack,表示其已经接收了数据。

- yack同步到发送时钟xclk上。

- X识别到同步的xack2信号后,将下一个数据放到数据总线上。

如图,安全地将一个数据从发送器传输到接收器需要5个时钟周期。

握手信号的要求

数据应在发送时钟域内稳定至少两个时钟上升沿。

xreq宽度应该超过两个上升沿时钟,否则从高速时钟域到低速时钟域传递可能无法捕捉到该信号。

握手信号缺点

传输单个数据延迟比FIFO传输同样的数据大得多。

使用同步FIFO传输数据

DPRAM(双端口RAM)用作FIFO以使读、写可以独立进行。

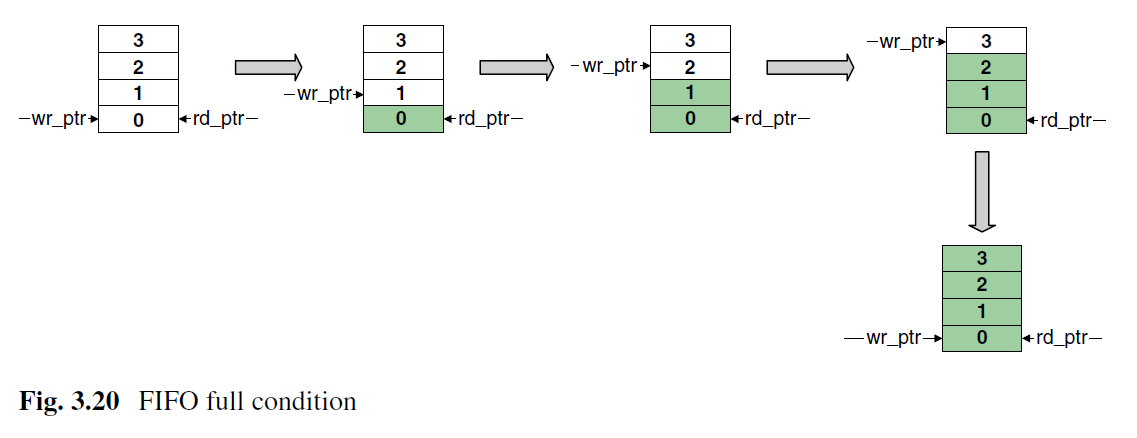

- 写指针指向下一个要写的地址,读指针指向下一个要读的地址。写使能使写指针递增,读使能使读指针递增。

- 根据读写指针可以产生空信号和满信号,也可以对FIFO内数据进行计数。

- DPRAM可以同步读取或者异步读取。同步读时,应在FIFO输出有效前给都信号。异步读时,输出不会寄存。数据只要一写入就可用。

FIFO空满的产生

图中为FIFO满的情况,当读指针等于写指针加一并进行写操作,FIFO满。

同样,当读操作使两个指针在下个周期相等时,FIFO变空。

另一种方法

另一种方法使使用计数器来指示FIFO中空或满位置的个数。写入数据时计数器加一,读取数据时计数器减一。

这种方法原理上简单,但是要增加额外的硬件(比较器)。FIFO深度增加,比较器宽度也会增加,这最终会降低FIFO操作的最高频率。