【IC每日一题:AMBA总线--APB协议时序及Verilog实现】

AMBA总线--APB协议时序及Verilog实现

- 1 APB3协议

- 1.1 APB3时序

- 1.1.1 APB写操作

- 1.1.2 APB读操作

- 2 代码

- 2.1 apb_master

- 2.2 apb_slave

【博客首发于微信公众号《漫谈芯片与编程》,欢迎专注一下,多谢大家】

AMBA总线是用于连接微控制器和外围设备的总线协议,由ARM公司提出的一种片上系统SoC互联标准。

AMBA总线协议家族主要包括:APB、AHB、AXI、ACI、CHI协议;其中后两个协议主要是专门为了缓存一致性;

本篇博客主要介绍 APB3协议;

1 APB3协议

APB3协议:APB用来实现与外围设备进行通信–一般用来配置寄存器;APB协议是一主多从,唯一的master一般是apb_bridge模块;

总体特点:低功耗、低带宽、无流水线结构、每次传输至少需要两个时钟周期;

1.1 APB3时序

在这里会分别给出有等待和无等待的时序图做对比,在项目中主要还是用的有等待时序图;

什么是无等待:即slave会直接在maste拉高penable时进行拉高,只维持一个周期;

什么是有等待:即slave会跟自己内部业务进行任意时刻拉高pready,而在此期间以上master的信号都要维持不变;

1.1.1 APB写操作

【描述】

1.T0周期(T0-T1):IDLE状态;

2.T1周期(T1-T2):master提前准备好pasel,paddr,pwrite,pwdata;

3.T2周期(T2-T3):master拉高penable,告知当前数据有效,进行采样传输;

–>T3周期(T3-T4):是代表数据传输结束,回到IDLE状态;

1.1.2 APB读操作

T0周期:IDLE状态;

T1周期:master提前准备好psel,paddr,pwrite;

T2周期:在无等待模式下:slave准备好prdate并拉高pready;当然在有等待模式下,pready可以继续没准备好,当pready准备好拉高后,prdata同时返回并有效;

2 代码

从前面系列篇可知:对待时序,我们尽量用状态机来设计指导编码;

在这里官方给出状态机:正好对应上面时序图上的周期;

IDLE:deault state;

SetUp:psel立刻拉高,相关信号在setup阶段准备好,并且下一周期就立刻转移到下一状态;

Access:penable在该状态拉高,相关信号paddr,pwrite,psel,pwdata等在这保持;

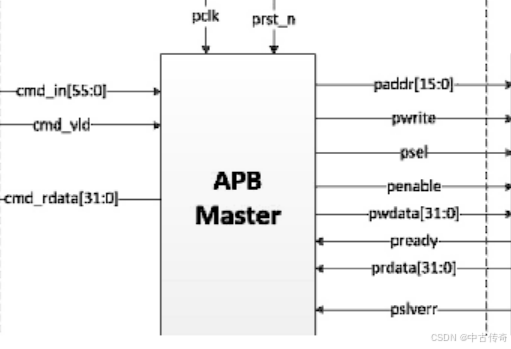

2.1 apb_master

在这里实现一个apb_master的代码示例:

/*-------------------------------------------------------------

-- modified by xlinxdu, 2022/05/27

-- pclk 50MHz

-- APB3,No pslverr signal

-- cmd_i:56bit;[55:48]:r/w ,8'b0 -> read,8'b1 -> write[47:32]:paddr ,[31:0]:pwdata

-------------------------------------------------------------*/

module apb

#(parameter RD_FLAG = 8'b0 ,parameter WR_FLAG = 8'b1 ,parameter CMD_RW_WIDTH = 8 ,parameter CMD_ADDR_WIDTH = 16 ,parameter CMD_DATA_WIDTH = 32 ,parameter CMD_WIDTH = CMD_RW_WIDTH + CMD_ADDR_WIDTH + CMD_DATA_WIDTH

)(

//-- system signalinput pclk_i ,input prst_n_i ,//-- cmd_ininput [CMD_WIDTH-1:0] cmd_i ,input cmd_vld_i ,output reg [CMD_DATA_WIDTH-1:0] cmd_rd_data_o,//-- apb interfaceoutput reg [CMD_ADDR_WIDTH-1:0] paddr_o ,output reg pwrite_o ,output reg psel_o ,output reg penable_o ,output reg [CMD_DATA_WIDTH-1:0] pwdata_o ,input [CMD_DATA_WIDTH-1:0] prdata_i ,input pready_i ,input pslverr_i

);//-- FSM state

parameter IDLE = 3'b001;

parameter SETUP = 3'b010;

parameter ACCESS = 3'b100;//-- current state and next state

reg [2:0] cur_state;

reg [2:0] nxt_state;//-- data buf

reg start_flag ;

reg [CMD_WIDTH-1:0] cmd_in_buf ;

reg [CMD_DATA_WIDTH-1:0] cmd_rd_data_buf;/*-----------------------------------------------\-- update cmd_in_buf --

\-----------------------------------------------*/

always @ (posedge pclk_i or negedge prst_n_i) beginif (!prst_n_i) begincmd_in_buf <= {(CMD_WIDTH){1'b0}};endelse if (cmd_vld_i && pready_i) begincmd_in_buf <= cmd_i;end

end/*-----------------------------------------------\-- start flag of transfer --

\-----------------------------------------------*/

always @ (posedge pclk_i or negedge prst_n_i) beginif (!prst_n_i) beginstart_flag <= 1'b0;endelse if (cmd_vld_i && pready_i) beginstart_flag <= 1'b1;endelse beginstart_flag <= 1'b0;end

end/*-----------------------------------------------\-- update current state --

\-----------------------------------------------*/

always @ (posedge pclk_i or negedge prst_n_i) beginif (!prst_n_i) begincur_state <= IDLE;endelse begincur_state <= nxt_state;end

end/*-----------------------------------------------\-- update next state --

\-----------------------------------------------*/

always @ (*) begincase(cur_state)IDLE :if(start_flag)beginnxt_state = SETUP;endelse beginnxt_state = IDLE;endSETUP :nxt_state = ACCESS;ACCESS:if (!pready_i)beginnxt_state = ACCESS;endelse if(start_flag)beginnxt_state = SETUP;endelse if(!cmd_vld_i && pready_i)beginnxt_state = IDLE;endendcase

end/*-----------------------------------------------\-- update signal of output --

\-----------------------------------------------*/

always @ (posedge pclk_i or negedge prst_n_i) beginif (!prst_n_i) beginpwrite_o <= 1'b0;psel_o <= 1'b0;penable_o <= 1'b0;paddr_o <= {(CMD_ADDR_WIDTH){1'b0}};pwdata_o <= {(CMD_DATA_WIDTH){1'b0}};endelse if (nxt_state == IDLE) beginpsel_o <= 1'b0;penable_o <= 1'b0;endelse if(nxt_state == SETUP)beginpsel_o <= 1'b1;penable_o <= 1'b0;paddr_o <= cmd_in_buf[CMD_WIDTH-CMD_RW_WIDTH-1:CMD_DATA_WIDTH];//-- readif(cmd_in_buf[CMD_WIDTH-1:CMD_WIDTH-8] == RD_FLAG)beginpwrite_o <= 1'b0;end//-- writeelse beginpwrite_o <= 1'b1;pwdata_o <= cmd_in_buf[CMD_DATA_WIDTH-1:0];endendelse if(nxt_state == ACCESS)beginpenable_o <= 1'b1;end

end/*-----------------------------------------------\-- update cmd_rd_data_buf --

\-----------------------------------------------*/

always @ (posedge pclk_i or negedge prst_n_i) beginif (!prst_n_i) begincmd_rd_data_buf <= {(CMD_DATA_WIDTH){1'b0}};endelse if (pready_i && psel_o && penable_o) begincmd_rd_data_buf <= prdata_i;end

end/*-----------------------------------------------\-- update cmd_rd_data_o --

\-----------------------------------------------*/

always @ (posedge pclk_i or negedge prst_n_i) beginif (!prst_n_i) begincmd_rd_data_o <= {(CMD_DATA_WIDTH){1'b0}};endelse begincmd_rd_data_o <= cmd_rd_data_buf;end

endendmodule2.2 apb_slave

在这里实现一个apb_slave读写寄存器的Demo;

`timescale 1ns/100psmodule apb_slave #(parameter AW = 32,//地址总线宽度parameter DW = 32 //数据总线宽度) (//systeminput reset_n,//apb_interfaceinput pclk, //时钟input [AW-1:0] paddr, //地址input pwrite, //读/写控制信号input psel, //选择信号input penable, //使能信号input [DW-1:0] pwdata, //写(输入)数据output reg [DW-1:0] prdata, //读(输出)数据output reg pready, //传输完成标志,low未完成,high完成output reg pslverr //错误标志,high出现错误);

//apb状态机

parameter IDLE = 2'b00;

parameter SETUP = 2'b01;

parameter ACCESS = 2'b10;

reg [1:0] state_now = 2'b00;

reg [1:0] state_next = 2'b00;//映射到总线上的寄存器

reg [31:0] readonly32; //0x10000000,只可读

reg [15:0] readonly16; //0x10000004,只可读

reg [31:0] readwrite32; //0x10000008,可读可写

reg [15:0] readwrite16; //0x1000000C,可读可写always @(posedge pclk or negedge reset_n) begin: init_and_change_stateif (!reset_n) beginpready <= 1'b0;pslverr <= 1'b0;prdata <= 32'h0;readwrite32 <= 32'h0;readwrite16 <= 16'h0;readonly32 <= 32'h12345678;readonly16 <= 16'habcd;state_now <= IDLE;endelse beginstate_now <= state_next;end

end//! fsm_extract

always @(posedge pclk) begin :main_fsm_of_apbcase (state_now)IDLE: begin //IDLE状态case (psel)1'b1: state_next <= SETUP; //选择本apb外设,进入setup状态1'b0: state_next <= IDLE;default: state_next <= IDLE;endcaseendSETUP: begin//SETUP状态case (psel)1'b1: begincase (penable)1'b1: state_next <= ACCESS;//选中且enable信号拉高,进入ACCESS模式传输数据1'b0: state_next <= SETUP;default: state_next <= SETUP;endcaseend1'b0: state_next <= IDLE; //未被选中,回到IDLEdefault: state_next <= IDLE;endcasepready <= 1'b0;endACCESS: begin //ACCESS状态,根据寄存器地址读写prdata <= 32'h0;pslverr <= 1'b0;if (pwrite) begin //wirte信号拉高,写入模式case (paddr)32'h10000008: begin readwrite32 <= pwdata; pready <= 1'b1; end//数据传输完成 32'h1000000C: begin readwrite16 <= pwdata[15:0]; pready <= 1'b1; end//数据传输完成 default: pslverr <= 1'b1;endcaseendelse if(!pwrite) begin //write信号拉低,读取模式case (paddr)32'h10000000: begin prdata <= readonly32; pready <= 1'b1; end//数据传输完成 32'h10000004: begin prdata <= readonly16; pready <= 1'b1; end//数据传输完成 32'h10000008: begin prdata <= readwrite32; pready <= 1'b1; end//数据传输完成 32'h1000000C: begin prdata <= readwrite16; pready <= 1'b1; end//数据传输完成 default: pslverr <= 1'b1;endcaseendif (pready) begincase (psel)1'b1: state_next <= SETUP; //不需要传输数据,回到SETUP1'b0: state_next <= IDLE; //未被选中,回到IDLEdefault: state_next <= IDLE;endcaseendelse state_next <= ACCESS; //需要继续传输数据,则回到ACCESS enddefault: state_next <= IDLE;endcase

end

endmodule[ref]

1.https://blog.csdn.net/qq_43244515/article/details/124968189

2.https://www.amghank.cn/2021/08/24/CORE%E5%AD%A6%E4%B9%A0%EF%BC%9AAMBA3–APB%E6%80%BB%E7%BA%BF%E5%8D%8F%E8%AE%AE%E5%8F%8A%E7%AE%80%E5%8D%95%E4%BE%8B%E5%AD%90/